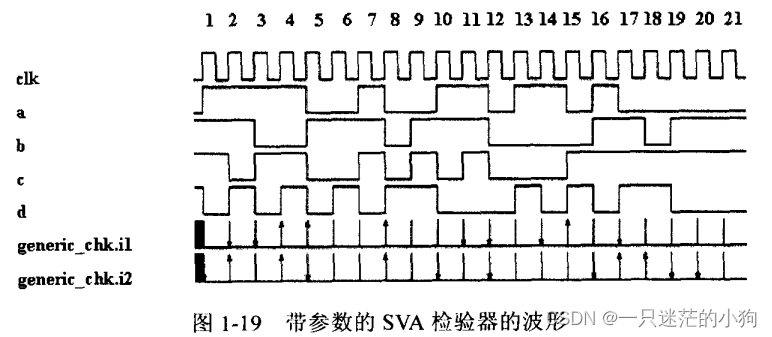

1.17使用参数的SVA检验器

SVA允许像 Verilog那样在检验器中使用参数( parameter),这为创建可重用的属性提供了很大的灵活性。比如,两个信号间的延迟信息可以在检验器中用参数表示,那么这种检验器就可以在设计只有时序关系不同的情况中重用。例子1.2显示了个带延迟默认值参数的检验器。如果这个检验器在设计中被调用,它使用一个时钟周期作为延迟默认值。如果在实例化时重设检验器中延迟参数值,那么同一个检验器就可以被重用。在例子1.2中,模块“top”有两个“ generic_chk”的实例。实例i1将延迟参数改写为2个时钟周期,而实例i使用默认的1个时钟周期。

例12使用参数的SA检验器的例子

module generic_chk(input logic a,b,clk);

parameter delay=1;

property p16;

@(posedge clk) a |-> ## delay b;

endproperty

a16 :assert property (p16);

endmodule

//call checker from the top level module

module top(...);

logic clk,a,b,c,d;

generic_chk #(.delay(2)) i1 (a,b,clk);

generic_chk #(c,d,clk);

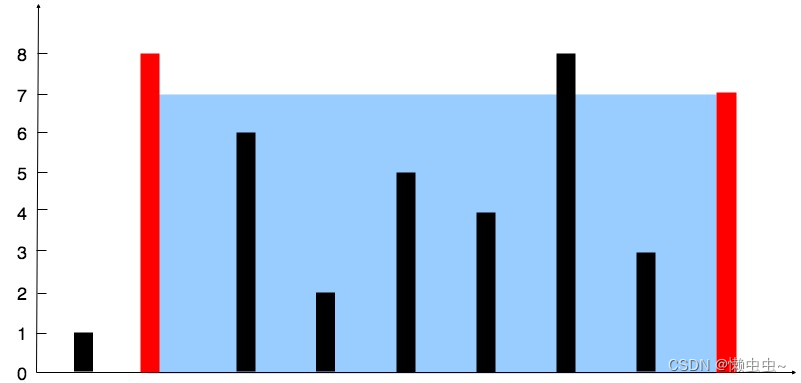

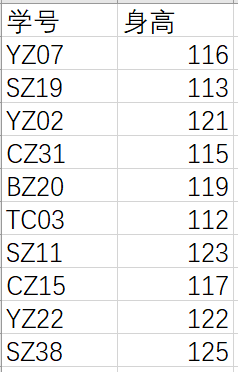

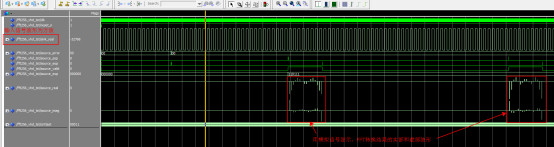

endmodule 图1-19显示了两个检验器实例i和i在模拟过程中对信号变化的响应。