上一篇介绍了tcl脚本的应用,这一篇将介绍SignalTapII。

之前的工程我们是做仿真,设置激励,观察输出波形去判断代码没有问题,但事实上我们真实的需求是综合后的代码下载到FPGA芯片中能够符合预期。

其中可能出现问题的原因有:

1、我们是写testbench设置激励,事实上当代码量大时,不可能100%覆盖率,例如一个与门有四种可能的激励(0&0,0&1,1&0,1&1),当testbench的激励只涉及其中两种时就只有50%的覆盖率。如果不能把所有的可能性包含进去,就不能保证结果全部正确

2、硬件本身的信号干扰等问题也是可能的,高速系统的问题尤其多

逻辑分析仪的原理:

逻辑分析仪是属于数据域测试仪器中的一种总线分析仪,即以总线概念为基础,同时对多条数据线上的数据流进行观察和测试的仪器,利用时钟从测试设备上采集和显示数字信号 。逻辑分析仪通常只显示两个电压。设定了参考电压后,逻辑分析仪将被测信号通过比较器进行判定,高于参考电压者为1,低于参考电压者为0

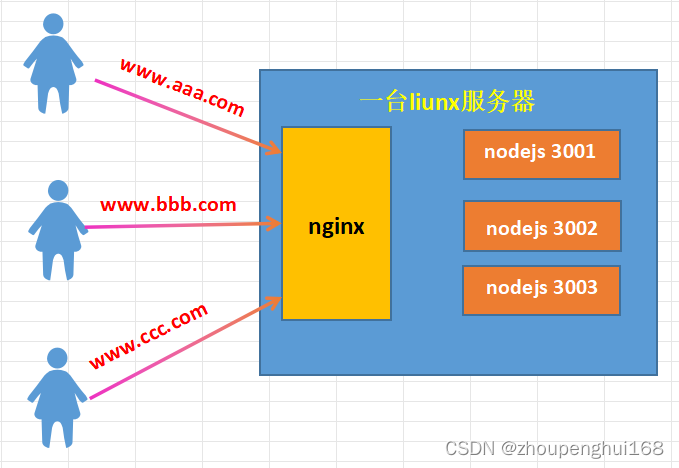

在线调试的方式主要有两种:

1、利用外部测试设备,把内部信号传送到FPGA 针脚上,然后用示波器或者逻辑分析仪观察信号

2、利用嵌入式逻辑分析仪,过程是这样的:我们在SignalTapII设置采样时钟和选择想查看的信号,在 FPGA中开辟一个存储器,存储器的大小限制了我们能存储的信息量。根据采样时钟和信号对数据进行采样并放置在存储空间中。根据提前设置的触发条件,将触发前后的数据返回给测试软件进行波形显示。

我们采用流水灯作为例子来学习SignalTap II的使用,在SignalTap II中设置好采样的时钟、深度、要抓取的信号和触发条件,然后将综合后的程序下载到开发板中,使用PC端的串口调试助手发送数据,最后在SignalTap II中观察波形。详细步骤如下:

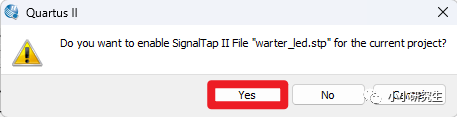

准备工作:打开流水灯工程,插好开发板。因为分析仪有点类似于,用户在图形化界面工具中的设置会被处理成一个模块,需要添加到原工程中,重新完成编译生成下载等过程,并将读取的数据返回进行显示。

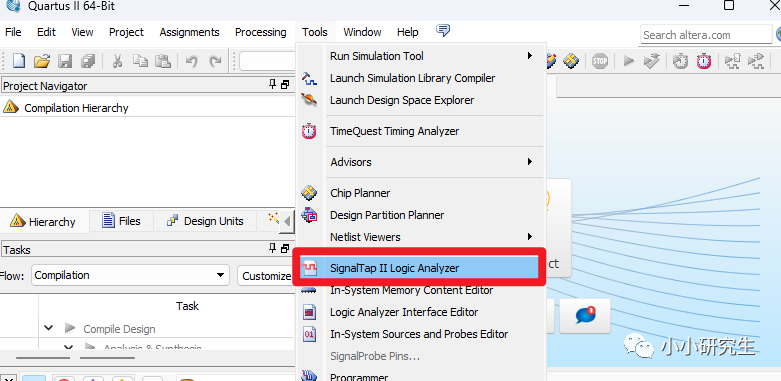

Step1:打开SignalTapII

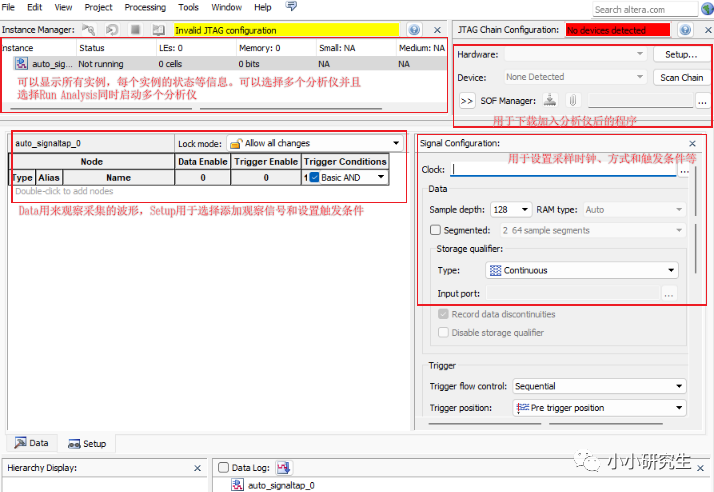

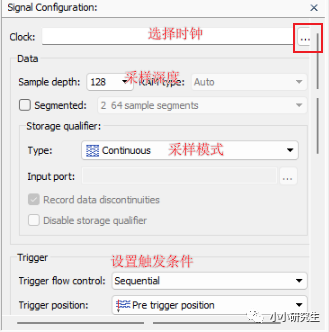

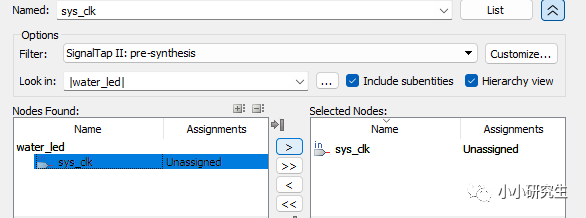

Step2:选择并添加采样时钟。采样时钟的频率越高,采集的数据点就越密集。开发板上采用的是50MHz的晶振,在引脚分配时已经将它作为输入的时钟信号 sys_clk,我们把它作为采样时钟。“ Named”、“Filter” 和“ Look in”用于精确查找我们所要添加的信号。Named是通过信号名称筛选信号,输入“syc_clk”可以快速准确定位到信号;Filter是根据信号类型来过滤我们所需要的信号,常用的有 “pre-synthesis” 和“post-fitting”,其中 “pre-synthesis” 代表综合前设计中的信号,与 Verilog 设计中存在的信号最为接近,用于选择RTL级的信号;而“ post-fitting” 用于选择综合优化、布局布线之后的一些信号,与设计电路的物理结构最为接近。“pre-synthesis ”并不能筛选出到所有信号节点,但寄存器端口和组合逻辑端口可以被提取到,大部分情况下我们使用 “pre-synthesis ”已经足够。Look in可以将信号筛选锁定在某个层次和模块,在一个复杂的工程包含多个不同层次的模块非常有用,能够帮助我们快速锁定信号所在的层次和模块,然后再去寻找具体的信号。

Step3:双击空白处,在对话框选择要观察的信号,这里我们需要的信号就是计数和输出信号

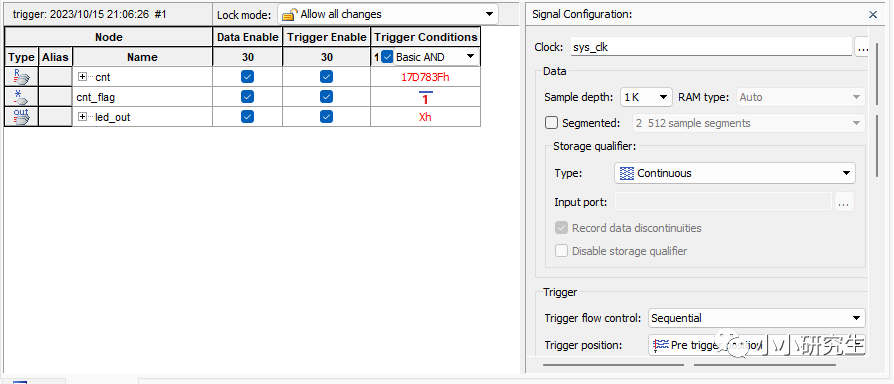

Step4:条件设置。采样深度是设置需要多大的存储空间来显示波形(所占用的总存储空间=要观察的信号总位宽x设置的采样深度),采样深度越大所占用的FPGA片上存储空间就越大,但资源有限,所以不要一味的追求更深的采样深度。这里选用1K的采样深度。通过 RAM 类型设置,用户可以选择使用哪一类型的存储器模块资源(例如M4K、M9K)来实现 SignalTap 存储器缓冲,从而防止使用到其他的存储器。我们使用的器件并不支持,所以显示为灰色默认 AUTO。采样模式分为分段采样和非分段采样(也叫循环采样),如果没有勾选上Segmented,就是非分段采样,在信号触发后就连续采样至采样深度;如果勾选上了“Segmented:”,就是分段采样,将采样深度分为 N 段,信号每触发一次就采样一段长度的数据,需要连续触发 N 次采样才能至采样深度。“2 512 sample segments”代表将采样深度分成2段,每段采样512个点。Type类型我们一般默认Continuous 即可。触发方式分为Trigger flow control、Trigger position和Trigger conditions。Trigger flow control是触发流程控制的设置,分为“ Sequential”和 “State-based”两种,基于状态用于较复杂的触发控制,对于一般的信号分析选择“ Sequential” 即可。“Trigger position”是触发位置,可以选择触发位置前后数据的比例,“Pre trigger position:”是保存触发信号发生之前的信号状态信息(88%触发前数据,12%触发后数据);“Center trigger position:”保存触发信号发生前后的数据信息,各占 50%;“Post trigger position:”保存触发信号发生之后的信号状态信息(12%触发前数据,88%触发后数据)。“Trigger conditions”是触发条件,可以选择触发条件的级别,最多可以设置 10 个触发级别。以“Sequential ”控制触发为例,对于多个级别的触发条件,如果非分段采样,则先等待判断 1 级触发条件是否满足,若满足则跳到触发条件 2 等待判断,否则继续等待,直到最后一级的触发条件判断满足后才正式开始捕获信号;对于分段采样,最后一级触发条件满足后开始捕获第一段信号,后面只需满足最后一级触发条件就再次捕获一段,也可以理解为前面级别的触发条件满足一次即可。大多数情况下1个触发条件已经足够了。触发条件的类型分为 “Basic” 和“Advanced”,我们选择默认的“ Basic ADN”即可。给观察信号设置触发条件,选中某个信号后右击弹出触发条件选择菜单,根据需求选择触发条件:“Don’t Care ”代表任意条件都触发,“Low” 表示信号低电平时触发,“Falling Edge”表示信号下降沿时触发,“Rising Edge ”表示信号上升沿时触发,“High” 表示信号高电平时触发,“Either Edge ”表示任意沿触发,如果是总线可以直接输入具体的值。同一列中的“Trigger Conditons ”属于同一级别,可以给该列中多个信号同时设置触发条件,但是要同时满足条件时才会触发,与触发条件级别的同时满足是有区别的。

如下图进行设置,cnt触发条件为计数到24999999(十进制)计满,flag的触发条件为高电平,led_out有四种状态不设置

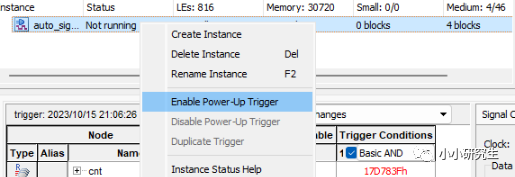

在使用SignalTap II 抓取信号时,经常会遇到有些信号只在开机后很短的时间内出现(比如几十us),如果按常规在开机运行后,再打开SignalTap II 抓取信号,此时需要抓取的信号已经过了,不能被抓取到,所所以SignalTap II里有一个“Power-Up Trigger”功能,可以在开机后就进行信号的捕获,这样只要是上电运行后的信号都能被抓取到。

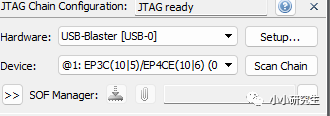

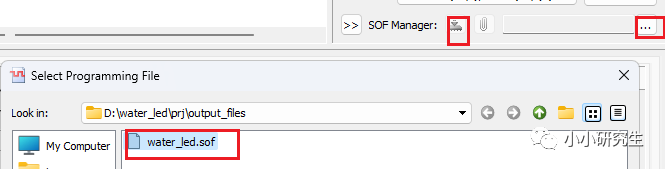

Step5:上述所有配置完成后一定!!!要在工程界面中点击“Start Analysis & Synthesis”图标进行分析和综合才能将在线逻辑分析仪映射到FPGA中,然后将生成的新.sof文件下载到我们的开发板中进行在线调试。

![]()

Step6:捕获信号。1是运行按钮,点击一次捕获一次信号;2是连续运行按钮,点击一次捕获连续进行;3是停止按钮,可以中止当前的信号捕获。Status栏显示着捕获状态,分为Not running(未运行)、Waiting for trigger(等待触发)和offloading acquired data(导出捕获到的数据)。

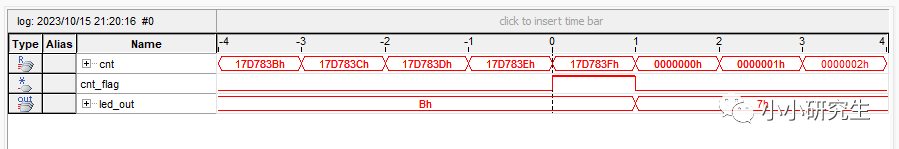

点击运行键,开始捕获信号,捕获完成后,设置区会自动切换到数据区,得到数据。

![]()

分析:cnt在计数值为17D783F(16进制)时flag拉高,led_out从一个灯亮到另一个灯亮(即1011到0111)。

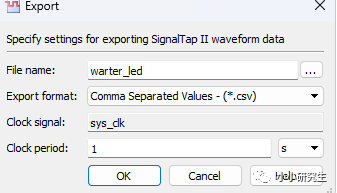

SignalTap II嵌入式逻辑分析仪可以采用矢量波形(.vwf)、矢量表(.tbl)、矢量文件(.vec)、逗号分割数据(.csv)和Verilog数值更改转存(.vcd) 文件格式输出所捕获的数据。这些文件格式可以被第三方验证工具读入,显示和分析SignalTap II嵌入式逻辑分析仪所捕获的数据。点击“File”目录下的“export”,选择合适的文件类型,点击“ok”保存即可。

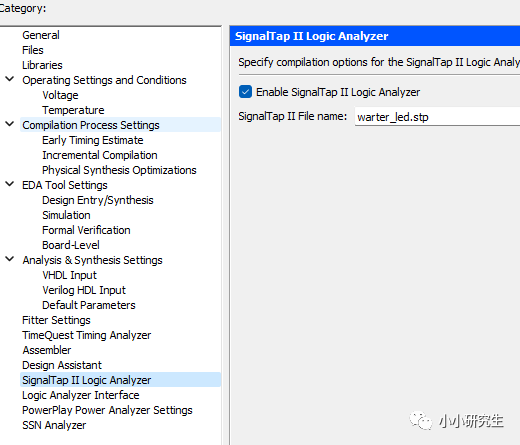

使用 SignalTap II 功能时会占用FPGA内部的存储资源,所以调试之后要将这部分资源释放掉。Assignments-Settings-SignalTap II Logic Analyzer-可以看到打勾,去掉这个勾即可关闭分析仪,然后再次综合就把在线逻辑分析仪所使用的资源给释放掉了,需要使用时再将其使能即可。