名称:简单秒表设计仿真VHDL跑表

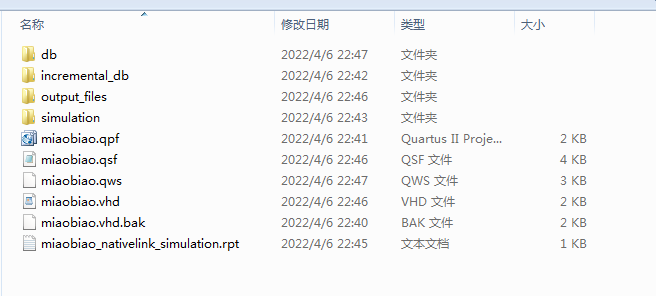

软件:Quartus

语言:VHDL

代码功能:

数字秒表功能描述

本次练习只需要一个数码管(假设该数码管已被选中),实现数码管显示功能,具体要求如下(设数码管为共阳)

1)实现秒表计时功能。

2)复位时,数码管显示

3)数码管依次从0变到9显示。

2信号列表 clk:50MHz的工作时钟,输入

系统复位信号,输入,低电平有效

segment:8位,输出,数码管显示信号,共8位。由低到高,分别表示数码管的a,b,c,d,e,f,g,h。当该比特为0时,表示点亮相应位置;为1时熄灭。

本代码包含2个工程,2工程代码一样,但是一个使用modelsim仿真,一个使用quartus自带的wvf仿真。

演示视频:简单秒表设计仿真VHDL跑表_Verilog/VHDL资源下载

FPGA代码资源下载网:hdlcode.com

代码下载:

简单秒表设计仿真VHDL跑表_Verilog/VHDL资源下载名称:简单秒表设计仿真VHDL跑表(代码在文末付费下载)软件:Quartus语言:VHDL代码功能:数字秒表功能描述 本次练习只需要一个数码管(假设该数码管已被选中),实现数码管显示功能,具体要求如下(设数码管为共阳)1)实现秒表计时功能。 2)复位时,数码管显示 3)数码管依次从0变到9显示。2信号列表 clk:50MHz的工作时钟,输入 系统复位信号,输入,低电平有效 segment:8位,输![]() http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=201

http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=201

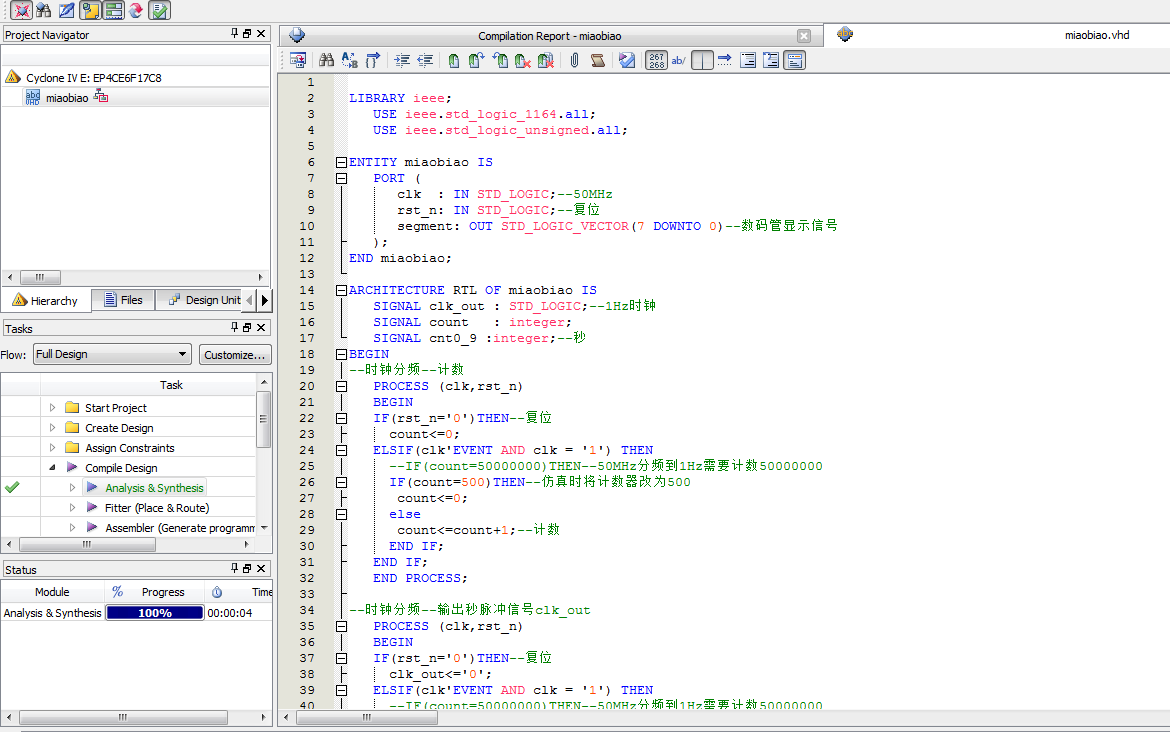

部分代码展示

LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_unsigned.all; ENTITY miaobiao IS PORT ( clk : IN STD_LOGIC;--50MHz rst_n: IN STD_LOGIC;--复位 segment: OUT STD_LOGIC_VECTOR(7 DOWNTO 0)--数码管显示信号 ); END miaobiao; ARCHITECTURE RTL OF miaobiao IS SIGNAL clk_out : STD_LOGIC;--1Hz时钟 SIGNAL count : integer; SIGNAL cnt0_9 :integer;--秒 BEGIN --时钟分频--计数 PROCESS (clk,rst_n) BEGIN IF(rst_n='0')THEN--复位 count<=0; ELSIF(clk'EVENT AND clk = '1') THEN --IF(count=50000000)THEN--50MHz分频到1Hz需要计数50000000 IF(count=500)THEN--仿真时将计数器改为500 count<=0; else count<=count+1;--计数 END IF; END IF; END PROCESS; --时钟分频--输出秒脉冲信号clk_out PROCESS (clk,rst_n) BEGIN IF(rst_n='0')THEN--复位 clk_out<='0'; ELSIF(clk'EVENT AND clk = '1') THEN --IF(count=50000000)THEN--50MHz分频到1Hz需要计数50000000 IF(count=500)THEN--仿真时将计数器改为500 clk_out<='1';--输出1Hz秒计时信号 else clk_out<='0'; END IF; END IF; END PROCESS; --秒计数 PROCESS (clk_out,rst_n) BEGIN IF(rst_n='0')THEN--复位 cnt0_9<=0; ELSIF(clk_out'EVENT AND clk_out = '1') THEN--使用秒脉冲信号计数 IF(cnt0_9<9)THEN--最大到9 cnt0_9<=cnt0_9+1;--加 else cnt0_9<=0;--清零 END IF;

设计文档:

设计文档.doc ----quartus仿真

设计文档.doc ----modeslim仿真

1. 工程文件

2. 程序文件

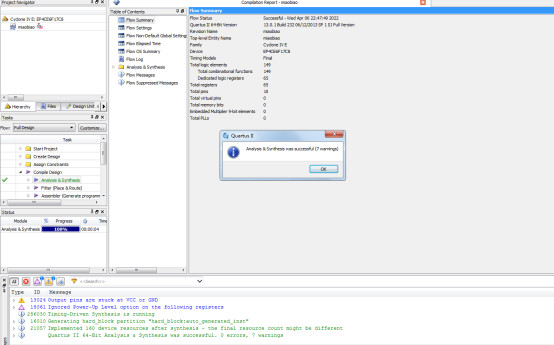

3. 程序编译

4. Testbench

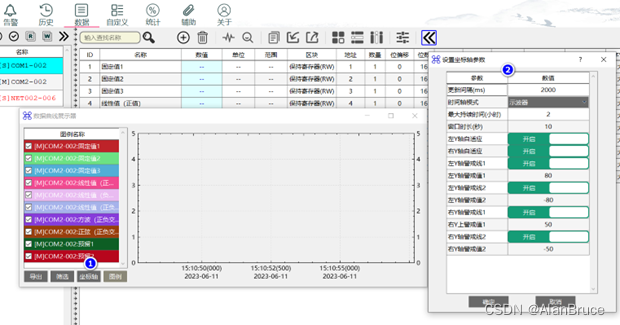

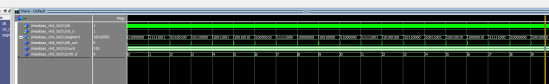

5. modelism仿真图

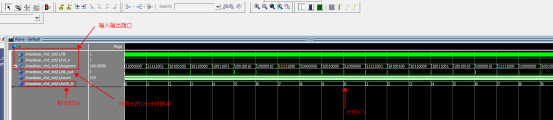

6. quartus wvf仿真图