总线:总线是传输数据的通道,由各种逻辑器件构成,一般由数据线、地址线、控制线等构成

接口:连接标准,又称之为物理接口i

协议:传输数据的规则

什么是AXI

AXI(Advanced Extensible Interfece)是高级可扩展接口,是ARM AMBA(Adavanced Microcontroller Bus Architecture,高级控制器总线架构)的一部分。

AXI三种类型:

AXI4(AXI-Full):用于高性能存储映射需求(存储器映射:主机对从机进行读写操作时,会给定一个目标地址,这个目标地址会对应系统存储空间的地址,表示对该该空间进行读写操作)

AXI-Lite:是AXI4的简化版,用于低吞吐率的存储映射接口

AXI-Stream(ST):用于高速的流数据通信

AXI协议的特点是:

- 分离的地址/控制和数据相位

- 使用字节选通的方式实现非对齐传输

- 主机只提供起始地址

- 分离的读写数据通道,提供低成本的DMA访问

- 支持乱序传输

- 总线主设备(如处理器)可以同时发起多个读写事务,并且这些事务可以并行进行,而不需要等待之前的事务完成。

AXI总线优势: - 生产力

- 灵活性

- 可获得性

AXI架构

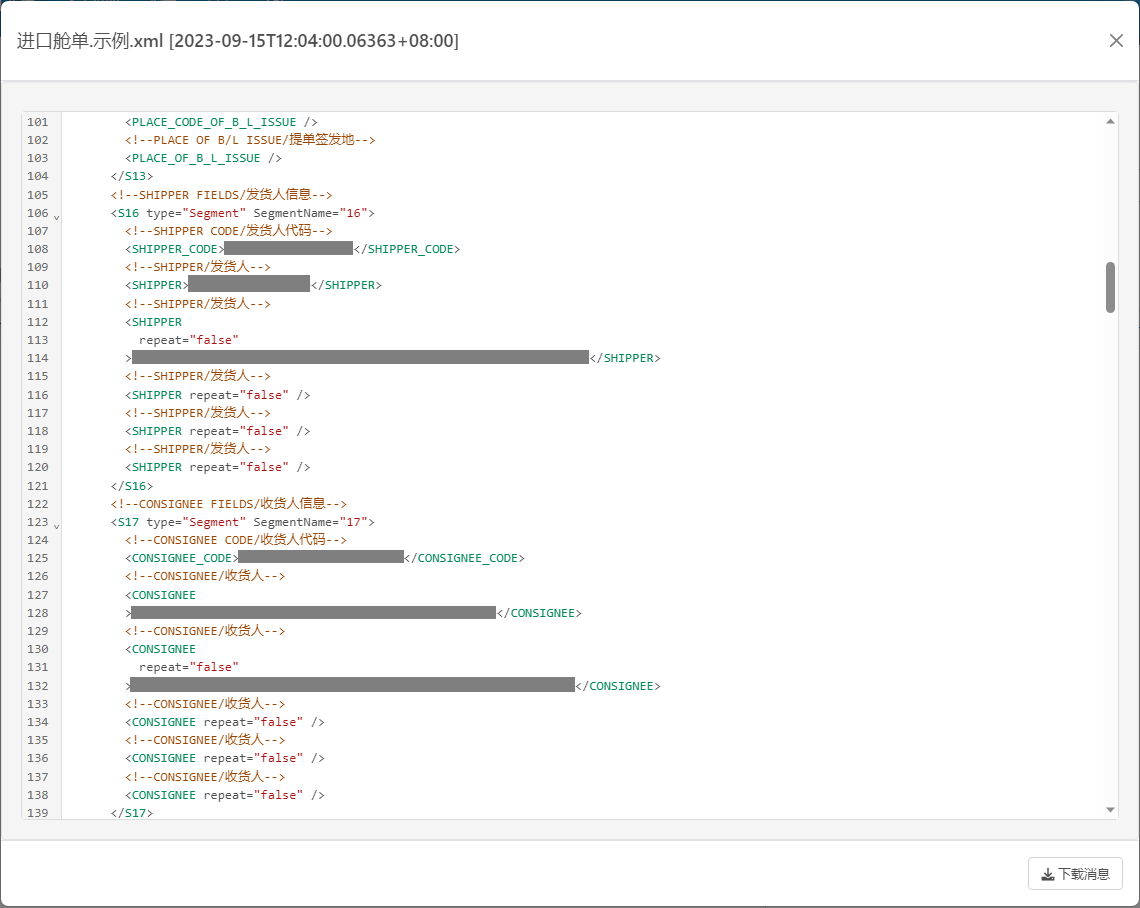

AXI协议有独立的五个通道:

1. 写地址通道:包含AWVALID,AWADDR, AWREADY信号

2. 写数据通道:包含WVALID, WDATA,WSTRB, WREADY信号

3. 写响应通道:包含BVALID, BRESP, BREADY信号

4. 读地址通道:包含ARVALID, ARADDR, ARREADY信号。

5. 读数据通道:包含RVALID, RDATA, RREADY, RRESP信号

其中写读地址通道包含控制信息

AXI总线读写数据的机制:

使用读地址和读数据通道实现传输过程的如下图所示:

在一个读传输过程中,主机要在读地址通道给出地址和控制信号,然后从机由读数据通道返回读出的数据。另外我们需要注意的是,这是一次突发读操作,主机只给出一个地址,从该地址连续突发读出四个数据。

写传输过程如下图所示:

写传输过程如下图所示:

用到了写地址、写数据和写响应三个通道。主机在写地址给出地址和控制信号,然后在写数据通道连续突发写四个数据。从机在接收数据后,在写响应通道给出响应信号。