Verilog刷题HDLBits——Exams/ece241 2014 q5a

- 题目描述

- 代码

- 结果

题目描述

You are to design a one-input one-output serial 2’s complementer Moore state machine. The input (x) is a series of bits (one per clock cycle) beginning with the least-significant bit of the number, and the output (Z) is the 2’s complement of the input. The machine will accept input numbers of arbitrary length. The circuit requires an asynchronous reset. The conversion begins when Reset is released and stops when Reset is asserted.

For example:

代码

module top_module (

input clk,

input areset,

input x,

output z

);

parameter idle=0,b1=1,b2=2;

reg[1:0] state,next_state;

always@(*)

case(state)

idle: next_state=x?b1:idle;

b1: next_state=x?b2:b1;

b2: next_state=x?b2:b1;

endcase

always@(posedge clk or posedge areset)

if(areset)

state<=idle;

else

state<=next_state;

assign z = state==b1;

endmodule

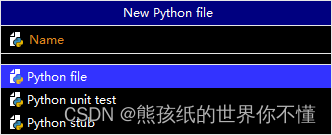

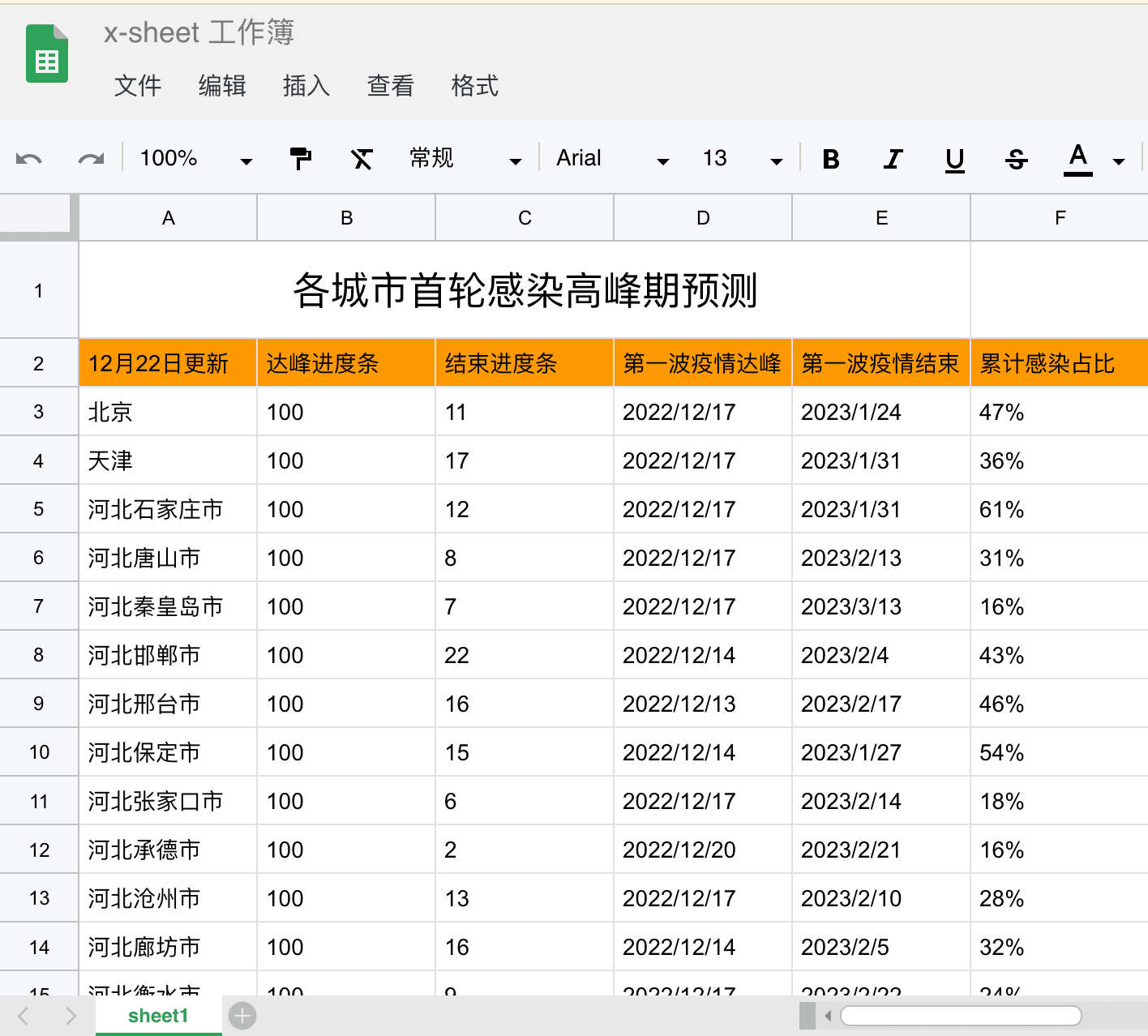

结果