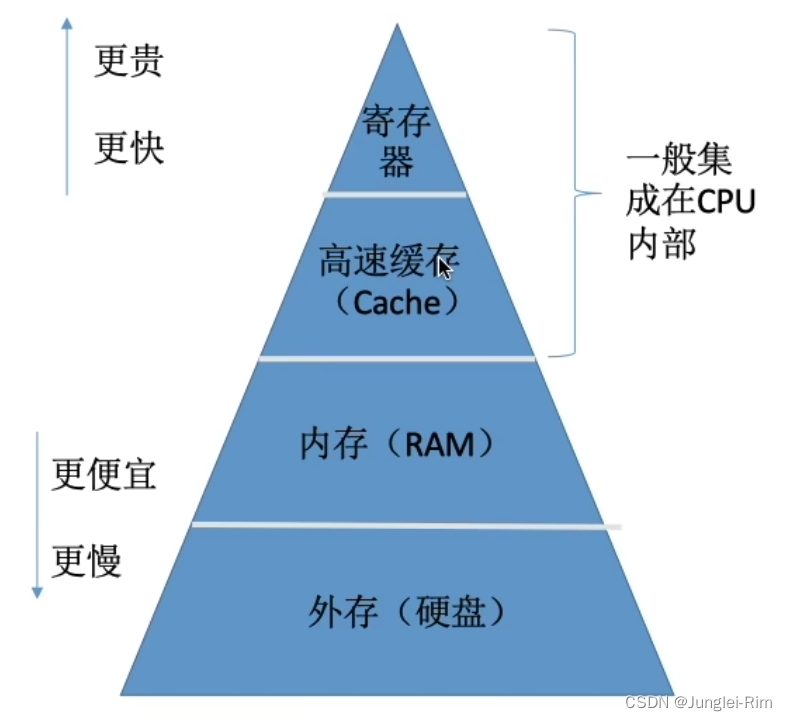

1.快表(TLB)

快表,又称联想寄存器(TLB,translation lookaside buffer),

是一种访问速度比内存快很多的高速缓存(TLB不是内存! ),

用来存放最近访问的页表项的副本,可以加速地址变换的速度。

与此对应,内存中的页表常称为慢表。

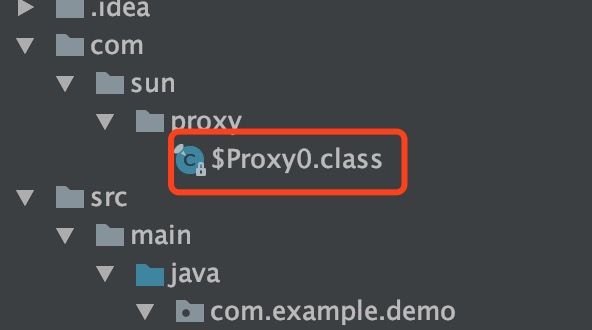

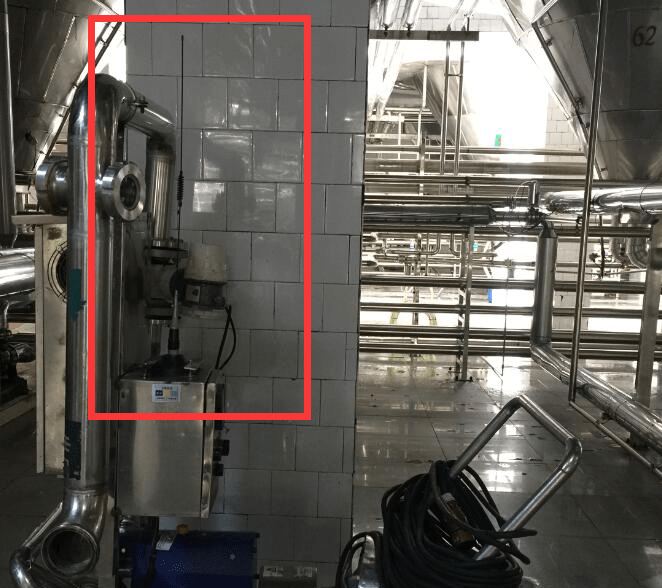

访问快表,慢表的过程:

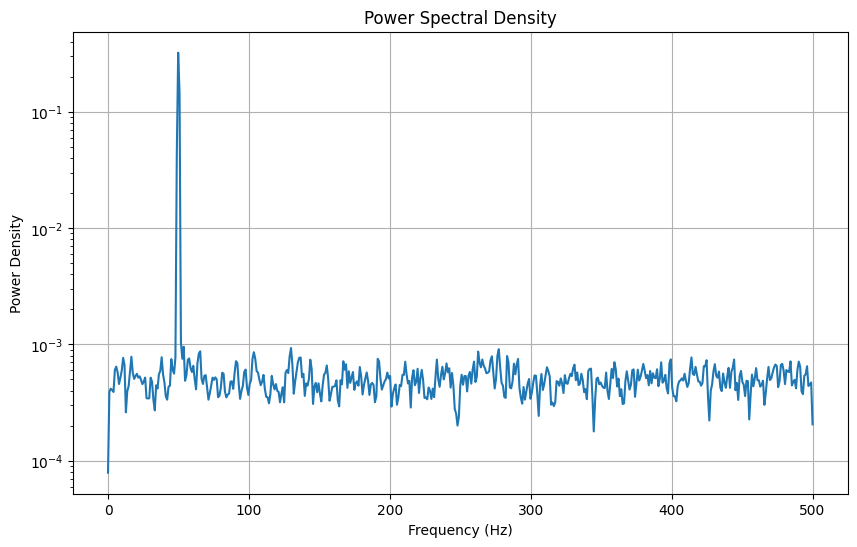

2.引入快表后,地址的变换过程

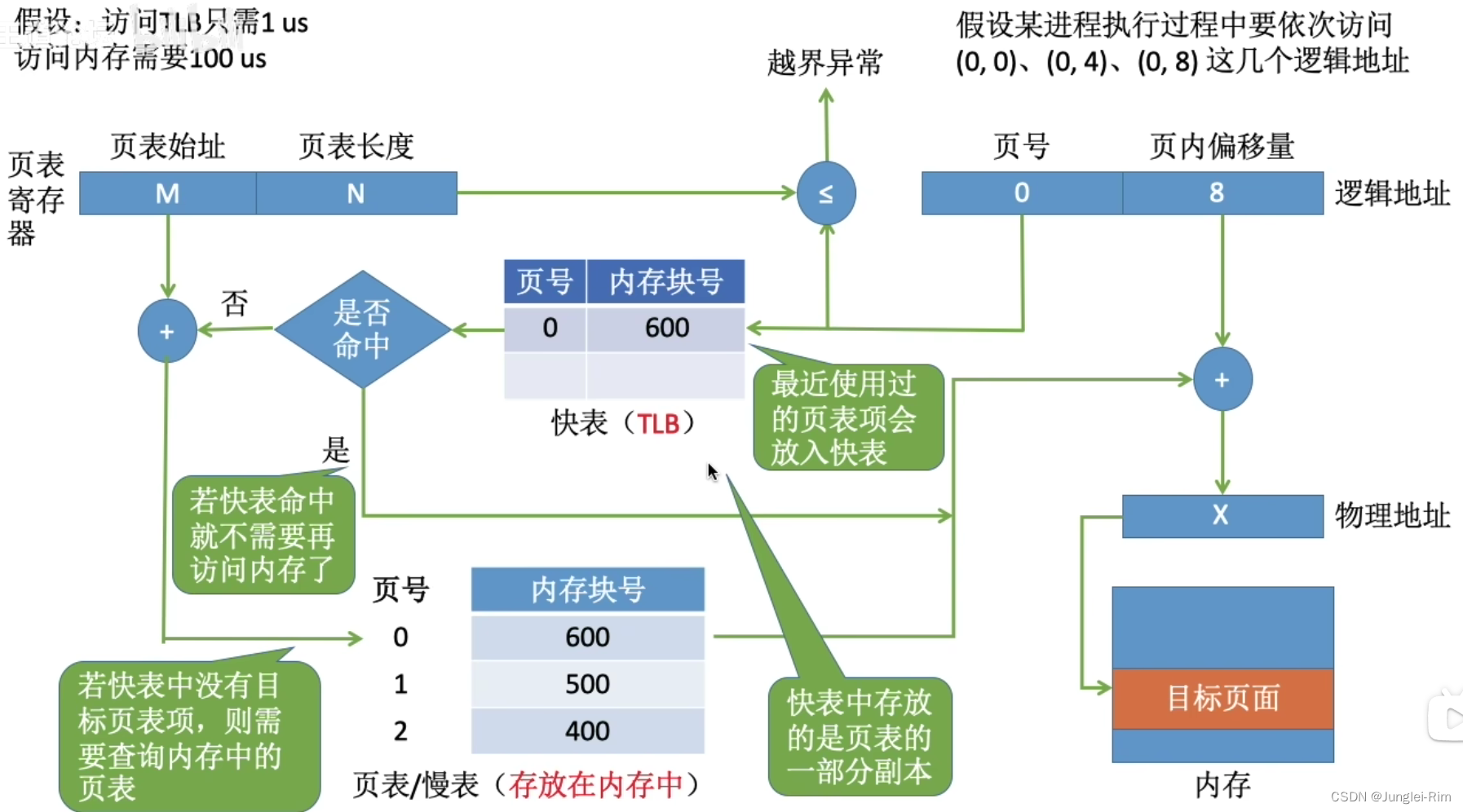

- CPU给出逻辑地址,由某个硬件算得页号、页内偏移量,将页号与快表中的所有页号进行比较。

- 如果找到匹配的页号,说明要访问的页表项在快表中有副本,则直接从中取出该页对应的内存块号,再将内存块号与页内偏移量拼接形成物理地址,最后,访问该物理地址对应的内存单元。

- 因此,若快表命中,则访问某个逻辑地址仅需一次访存即可。

- 如果没有找到匹配的页号,则需要访问内存中的页表,找到对应页表项,得到页面存放的内存块号,再将内存块号与页内偏移量拼接形成物理地址,最后,访问该物理地址对应的内存单元。

- 因此,若快表未命中,则访问某个逻辑地址需要两次访存(注意:在找到页表项后,应同时将其存入快表,以便后面可能的再次访问。但若快表已满,则必须按照一定的算法对旧的页表项进行替换)

由于查询快表的速度比查询页表的速度快很多,因此只要快表命中,就可以节省很多时间。

因为局部性原理,一般来说快表的命中率可以达到90%以上。

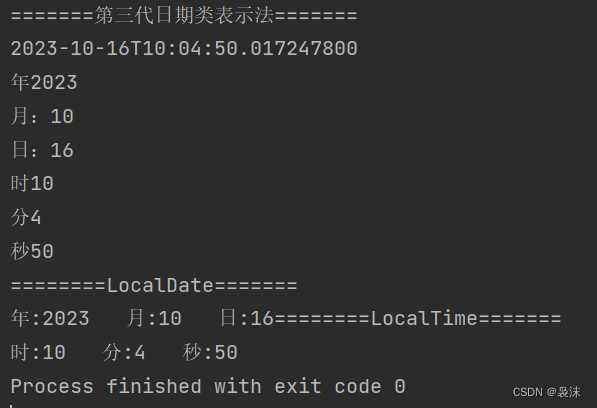

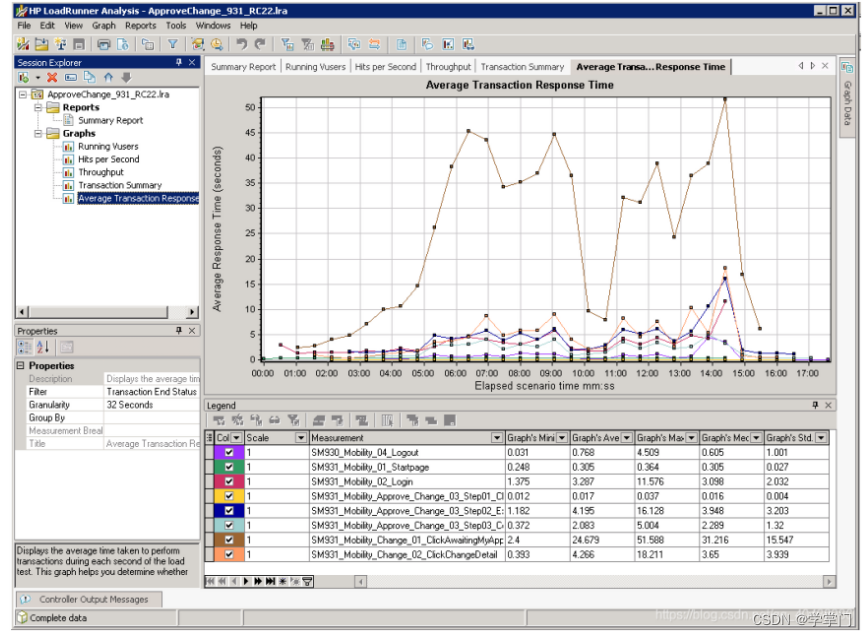

1.例题

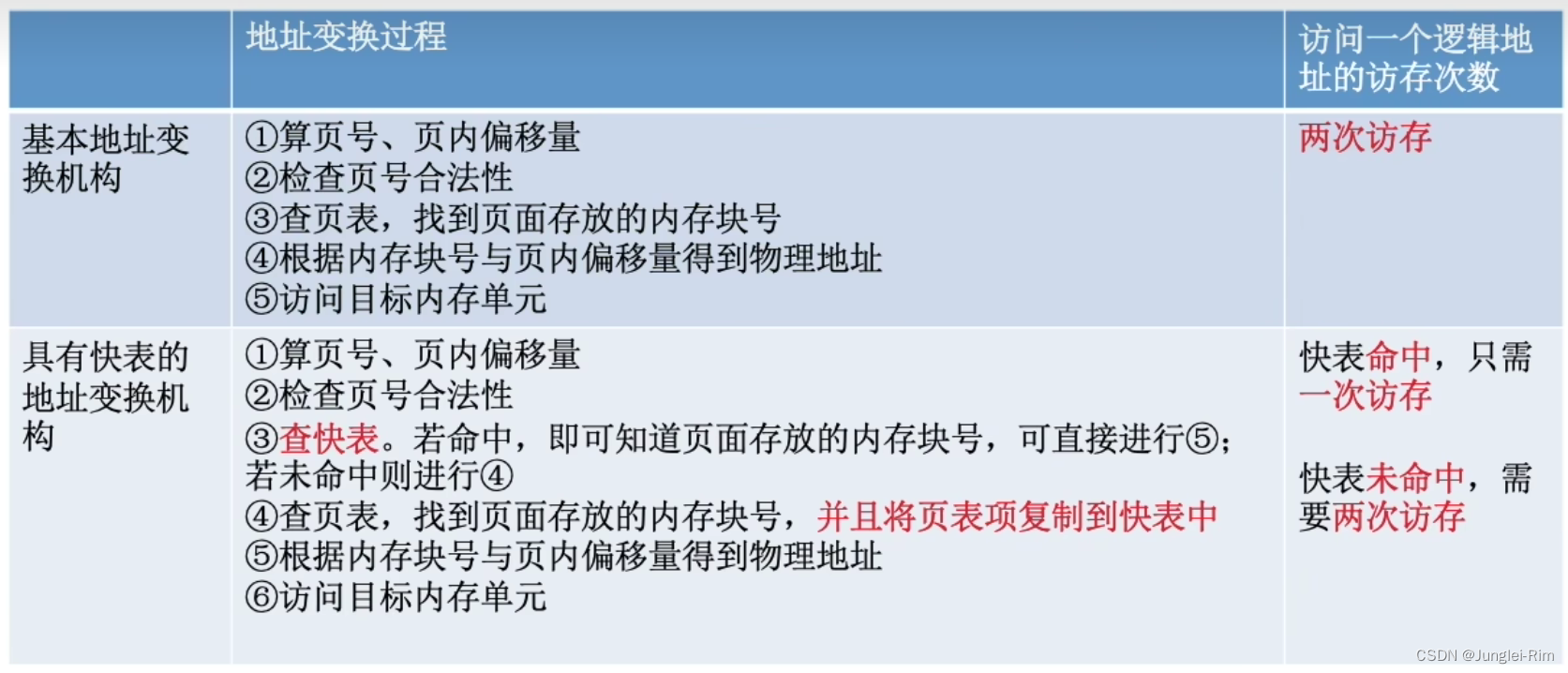

某系统使用基本分页存储管理,并采用了具有快表的地址变换机构。

访问一次快表耗时1us,访问一次内存耗时100us。若快表的命中率为90%,那么访问一个逻辑地址的平均耗时是多少?

(

1

+

100

)

∗

0.9

+

(

1

+

100

+

100

)

∗

0.1

=

111

u

s

(1+100)* 0.9+(1+100+100)*0.1=111 us

(1+100)∗0.9+(1+100+100)∗0.1=111us

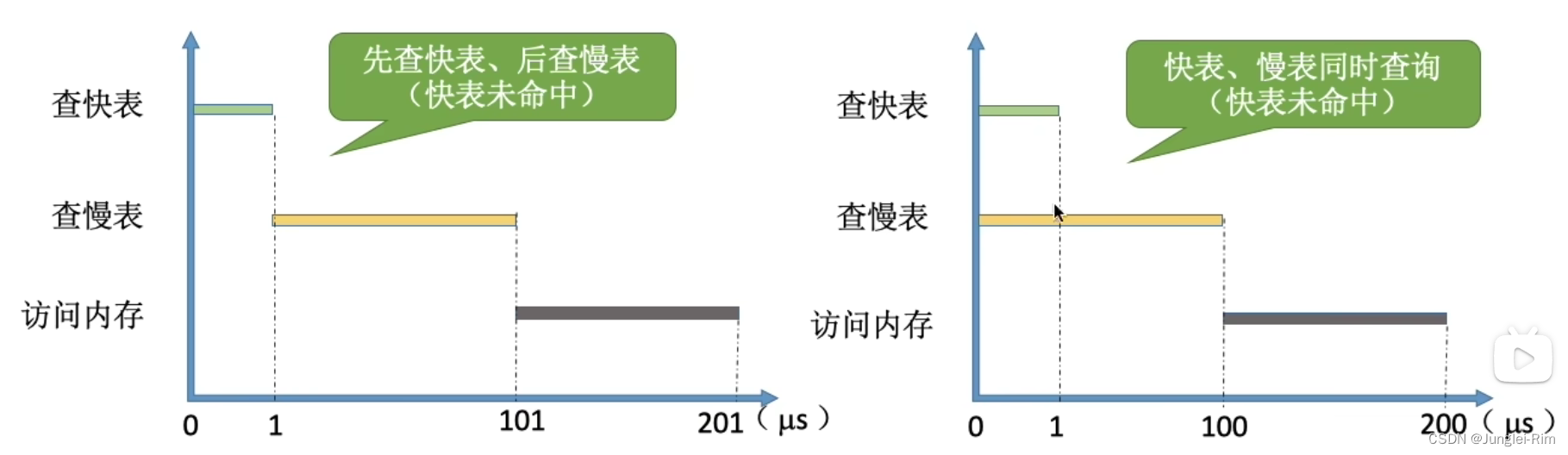

有的系统支持快表和慢表同时查找,如果是这样,平均耗时应该是

(

1

+

100

)

∗

0.9

+

(

100

+

100

)

∗

0.1

=

110.9

u

s

(1+100)*0.9 +(100+100)*0.1=110.9 us

(1+100)∗0.9+(100+100)∗0.1=110.9us

若未采用快表机制,则访问一个逻辑地址需要

100

+

100

=

200

u

s

100+100 = 200us

100+100=200us

3.局部性原理

1.时间局部性:

如果执行了程序中的某条指令,那么不久后这条指令很有可能再次执行;

如果某个数据被访问过,不久之后该数据很可能再次被访问。(因为程序中存在大量的循环)

2.空间局部性:

一旦程序访问了某个存储单元,在不久之后,其附近的存储单元也很有可能被访问。

(因为很多数据在内存中都是连续存放的)

在基本地址变换机构中,每次要访问一个逻辑地址,都需要查询内存中的页表。

由于局部性原理,可能连续很多次查到的都是同一个页表项。

TLB和普通Cache的区别:TLB中只有页表项的副本,而普通Cache中可能会有其他各种数据的副本。