后面的那个是延时精度

verilog文件结构

文件名称与写的模板没有关系,这个文件名为P1,但模板名为andgate

![]()

但是如果是仿真文件,就需要开头的模板名和仿真文件名相同

.v是源文件,设计文件

.v在设计与sim里都有,静态共享,是.v当中的设计文件在其中都有,而仿真,调用文件只在sim里有。什么文件的后缀名都是.v,因为都是verliog实现的,

也就是说仿真文件在创建的时候也是.v,和源文件没区别,只是在具体写的时候,写完的时候,计算机才能识别出哪个是仿真文件,哪个是设计文件。

没有实现新函数方法,只调用已有方法的是仿真文件

创建,设计了新函数方法的是源文件

举例

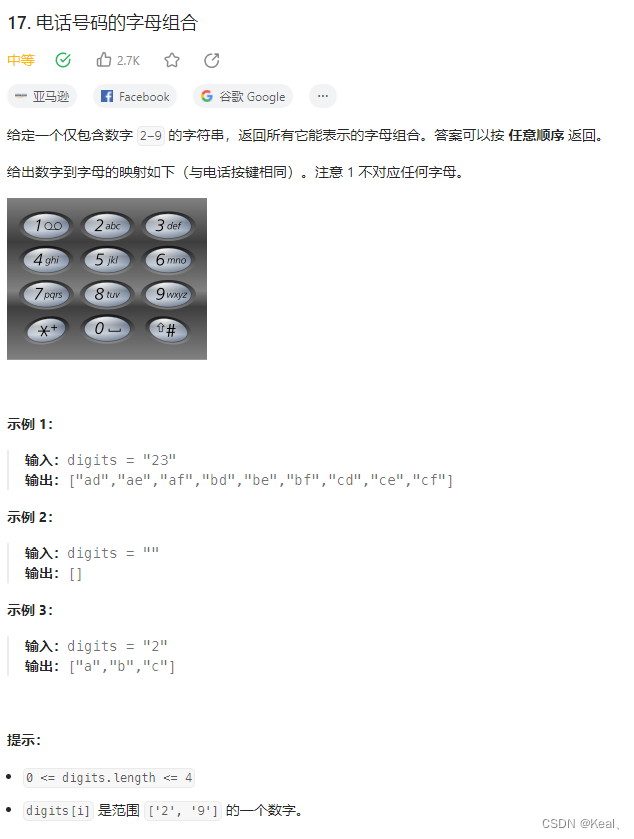

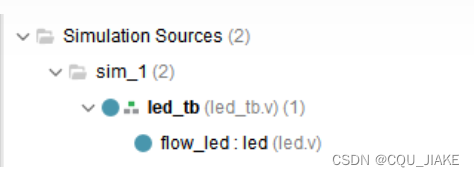

在仿真文件夹中,仿真文件有个名字,在上图中为led_tb,

在仿真时,仿真文件会调用源文件里的文件,调用了哪些,就意味着哪些文件附属在仿真文件之下,这里的仿真文件led_tb调用了led.v的源文件,所以led.v附属在其之下

而且,在仿真文件当中,实例化其的对象名称为flow_led,所以附属的结构为flow_led:led(led.v)

led表示源文件里实现的方法,flow_led表示这个仿真文件实例化这个类的一个具体名称,在Led之下,(led.v)表示在这个文件之中

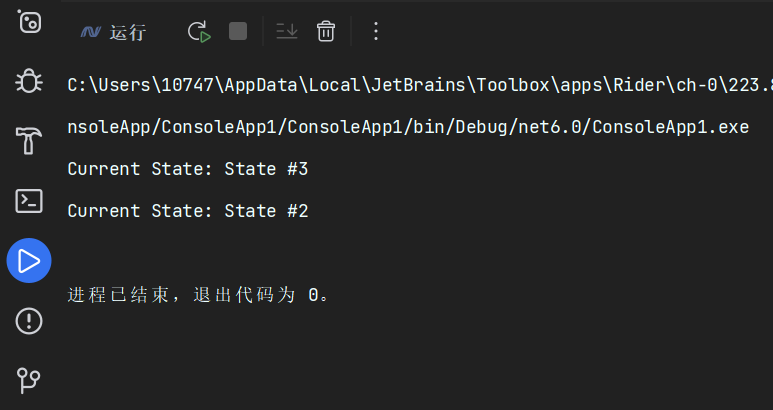

运行

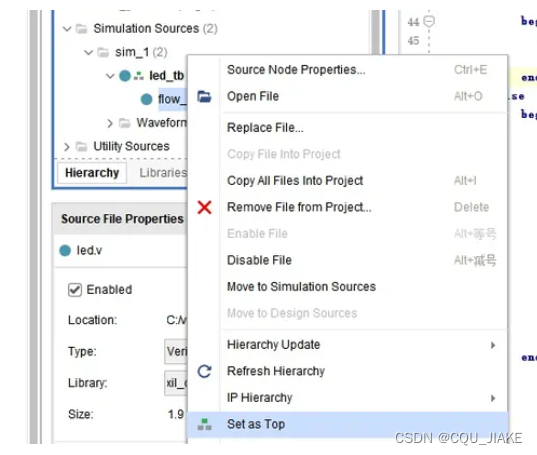

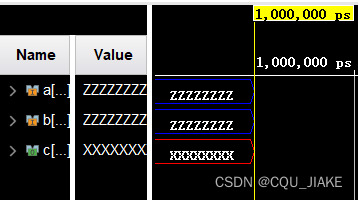

在实际运行中,这样的结果是错的,会导致出问题。即使原文件,原代码都是没问题的

因为仿真时是要运行仿真文件,

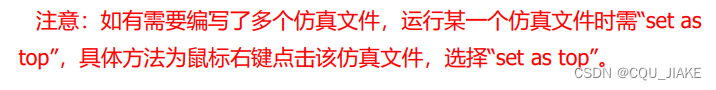

如果先说运行某个仿真文件下的实例化文件,就会出问题,正确的应该是始终保持仿真文件为顶头文件,一是要注意如果有多个文件,要顶头一个仿真文件;二是要注意顶头的是一级文件,即tp1,而不是p1,

这样就没问题了

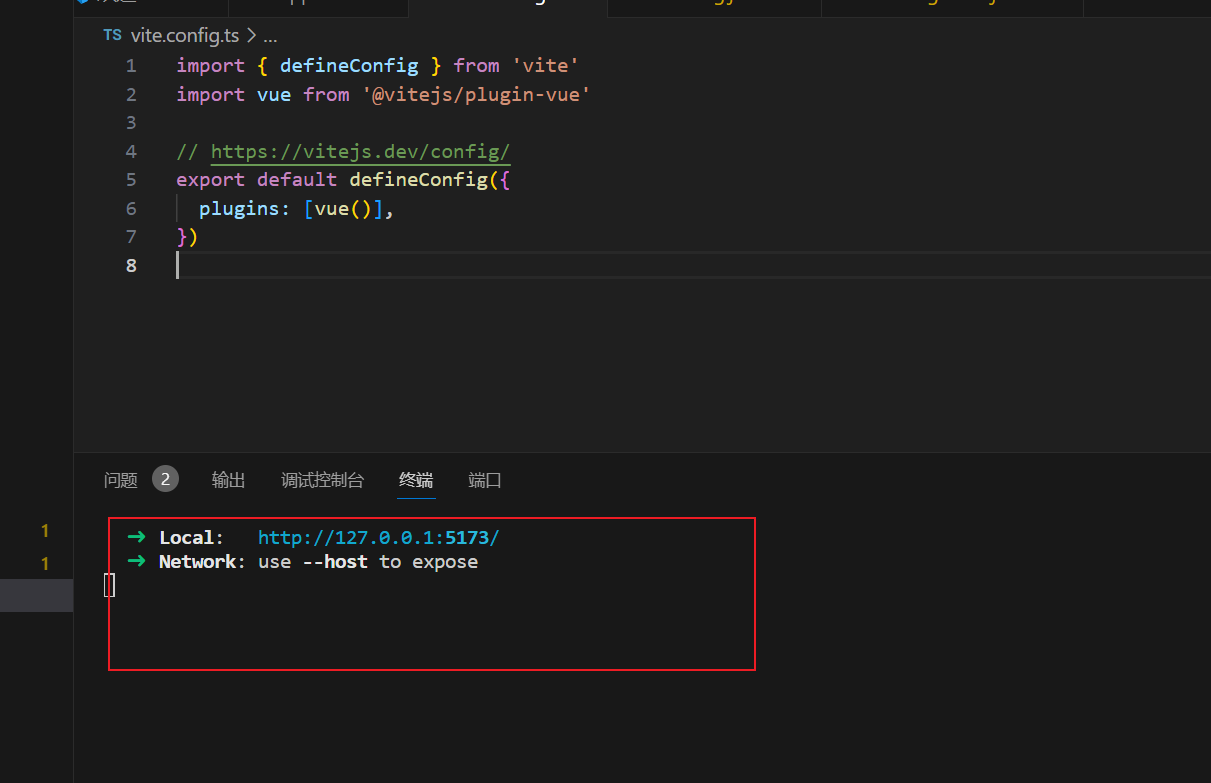

1.创建设计文件

就是写每个门或电路需要哪些信号以及用来干什么,输出什么

2.写仿真文件

仿真文件开始时要写一个模板,表示的是这个仿真文件的名字,要和文件名一样

仿真文件不实现新方法,所以其模板、类名称不需要定义,只需要声明一个空类即可

之后是声明与定义信号,

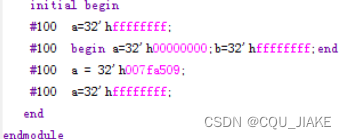

声明完后写initial,表示在不同的时间里上面声明的信号的值的情况是怎样的,即开始定义信号

最后end表示initial结束,即输入信号的完成

最后一步就是实例化一个源文件里的电路,然后把输入信号传进去即可

在信号定义之前之后好像都可以,最好在之前

在赋值当中,如果遇到对多个信号赋值,需要写begin,end,如果只有一个则不需要

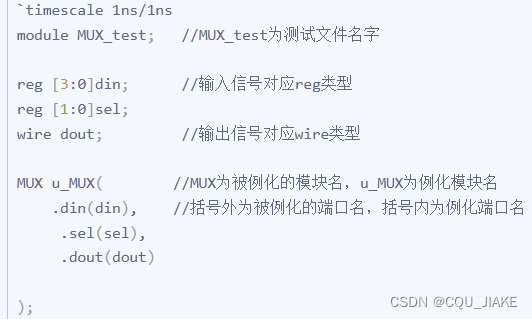

实例化的时候要这样,.din(din)

![]() 这样不行,这样是错的

这样不行,这样是错的

这是设计文件里的信号类型,输入是wire,输出是reg

这是设计文件里的信号类型,输入是wire,输出是reg

这是测试文件里的信号,可以发现输入wire定义成了reg,输出定义成了wire,注意一下

这是测试文件里的信号,可以发现输入wire定义成了reg,输出定义成了wire,注意一下

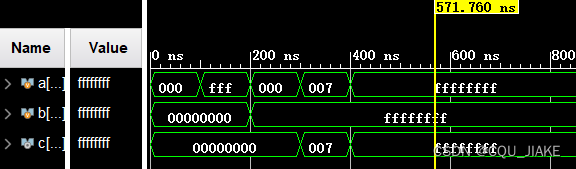

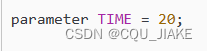

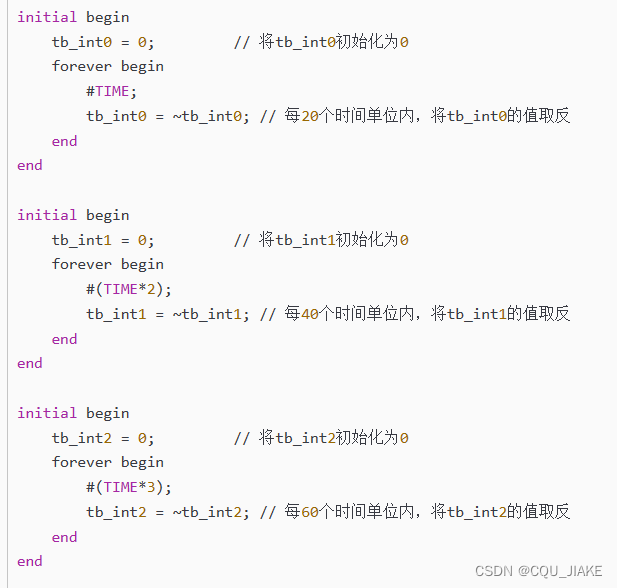

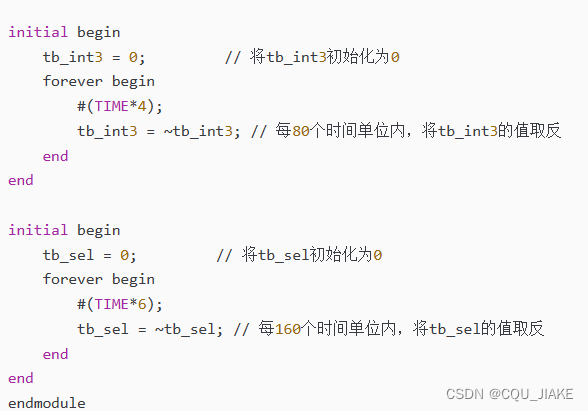

周期仿真,赋值

上面有定义时间参数为20

3.跑仿真

4.写引脚文件

5.综合

6.上板

?什么叫数据的宽度?

前面一个数字代表总共多少比特,b,h代表用二进制,十六进制,后面是实际的表示数据,基于前面选择的进制

比特就是二进制,不管用什么进制,都要转化为比特,比特的概念是二进制下的,就是说后面不管怎么表示,前面开头的比特数是一定的,只是根据选择进制不同,有不同的表现形式

固定为16时,如果为H表示,则用4位,用b表示,用16位

每位十六进制数字需要4位二进制数字表示,所以2位十六进制的位宽为8,8‘h11等价于8'b0001_0001

4'h1,一共4位二进制数。每个数字表示1位十六进制,即4位二进制数,等价于4’b0001

16'h4012,一共16位二进制数,每个数字表示1位十六进制数,即4位二进制数,一共4个数字,所以一共是4*4=16位,表示的二进制为0100_0000_0001_0010

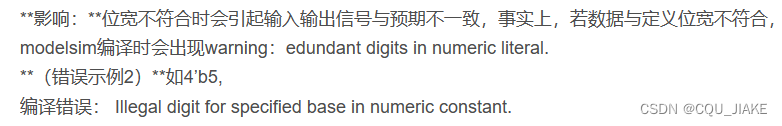

若实际记录的比前面标定的位数多,比如4‘h1111,实际记录了16位,但是前面预计记录只有4位,此时读数时,只会从实际记录的最低位向高位截取记录的相应位数,即实际记录为4‘h1,等价于4’b0001

redundant冗余的,numeric literal数字的,文本

specified指定的,numeric constant数字常量,specified base指定基数

?怎么在实际中传入多位宽的信号?

寄存器类型是reg,就是只有在满足always条件时才进行赋值,并且赋值完后具有记忆性,能在下次赋值前一直保持之前赋的值,

如果always@(*),里面是*,就表示一直满足条件,就会一直赋值,寄存的信号就和输入信号始终保持一致,就和assign没有什么区别

assign就是始终赋值,不保存信号,唯一的作用就是决定怎么赋值,实现一个对信号的处理,处理完后就直接传出去,不保存

如果没有信号时,用assign,会使输出信号为0,而always就会输出上次不为0的信号

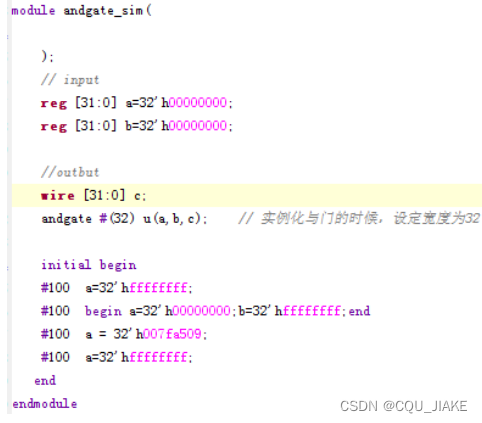

设计文件

仿真文件

设计文件当中定义了一个参数,那么在声明与实例化时,也要表明这个参数的值,不然就是缺省信号,按计划值赋值

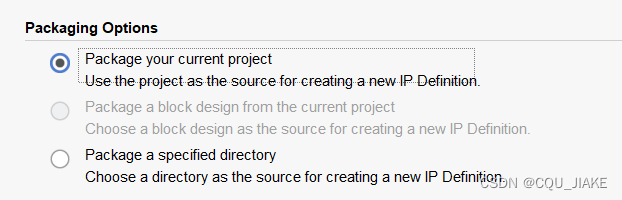

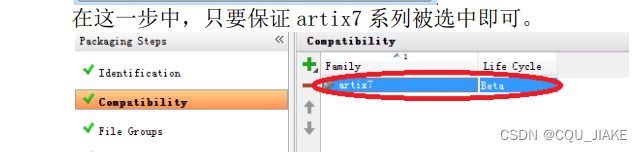

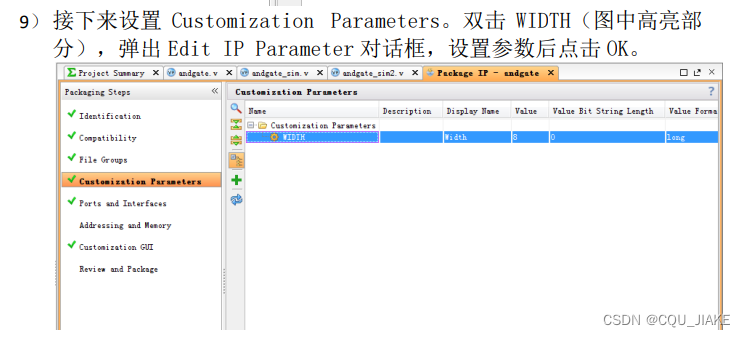

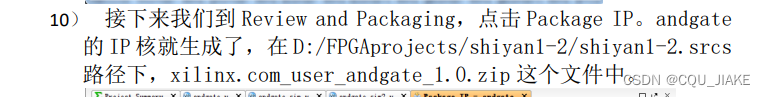

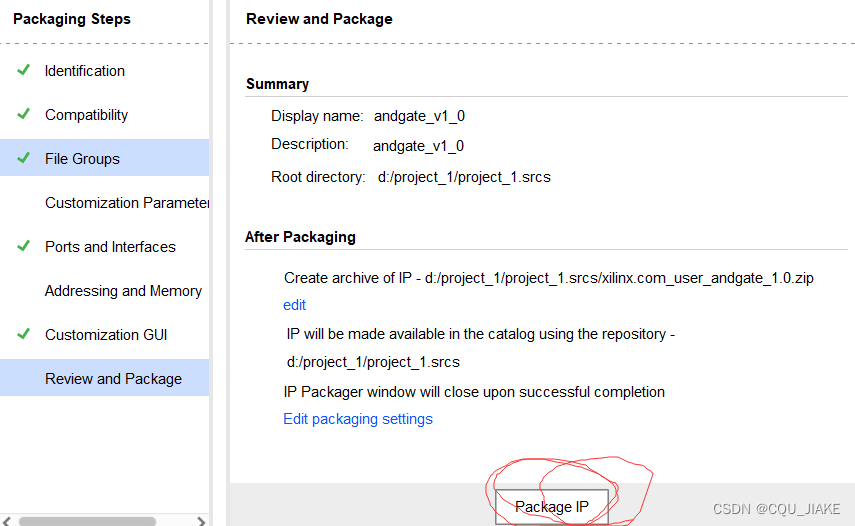

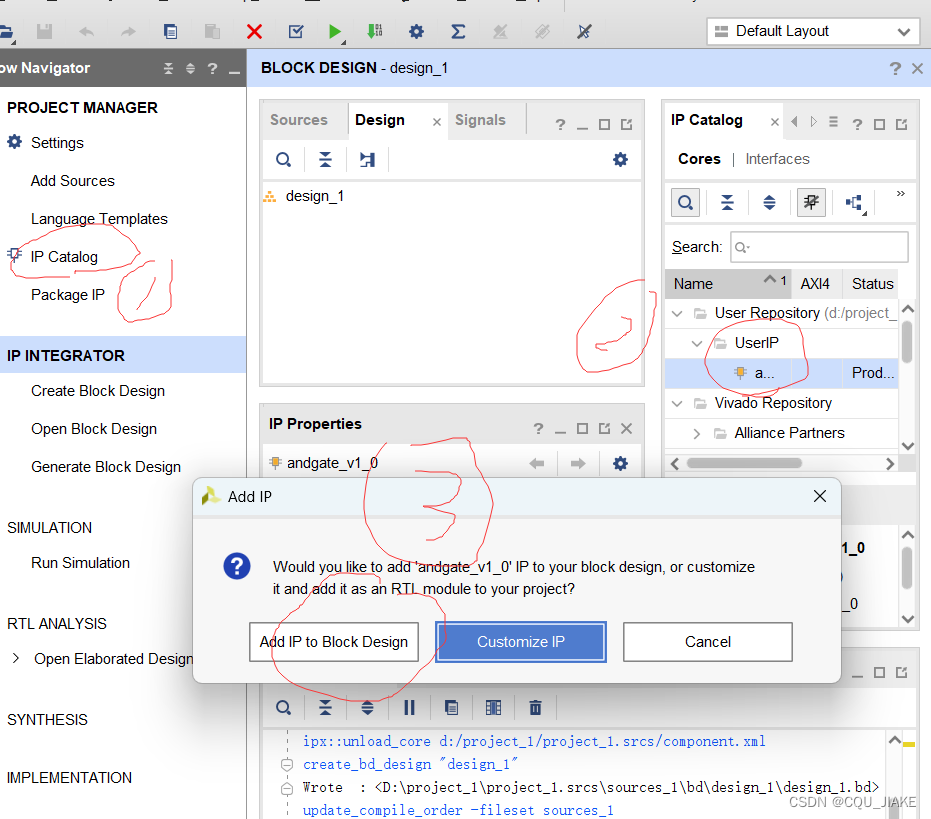

创建IP核

流程

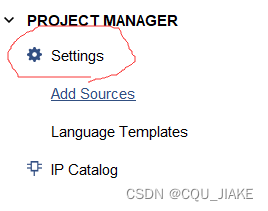

1点这个

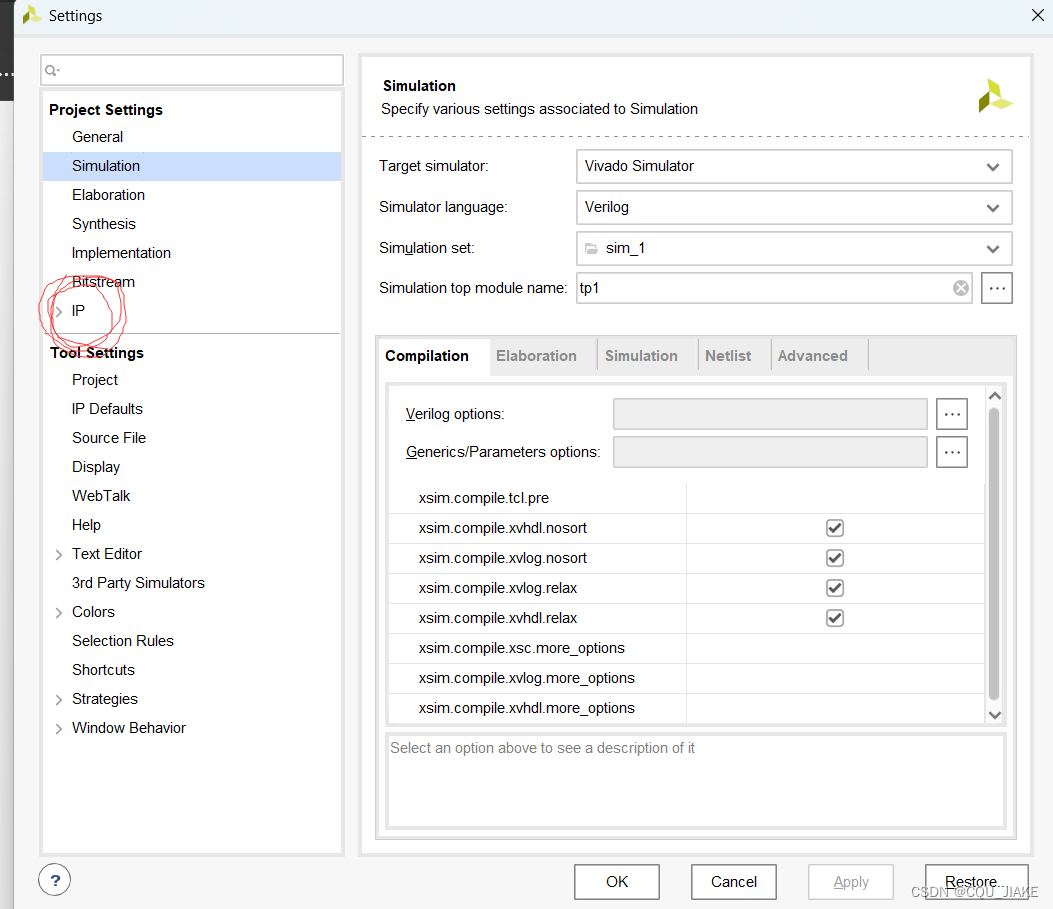

2.点这个,并展开

3.这样配置

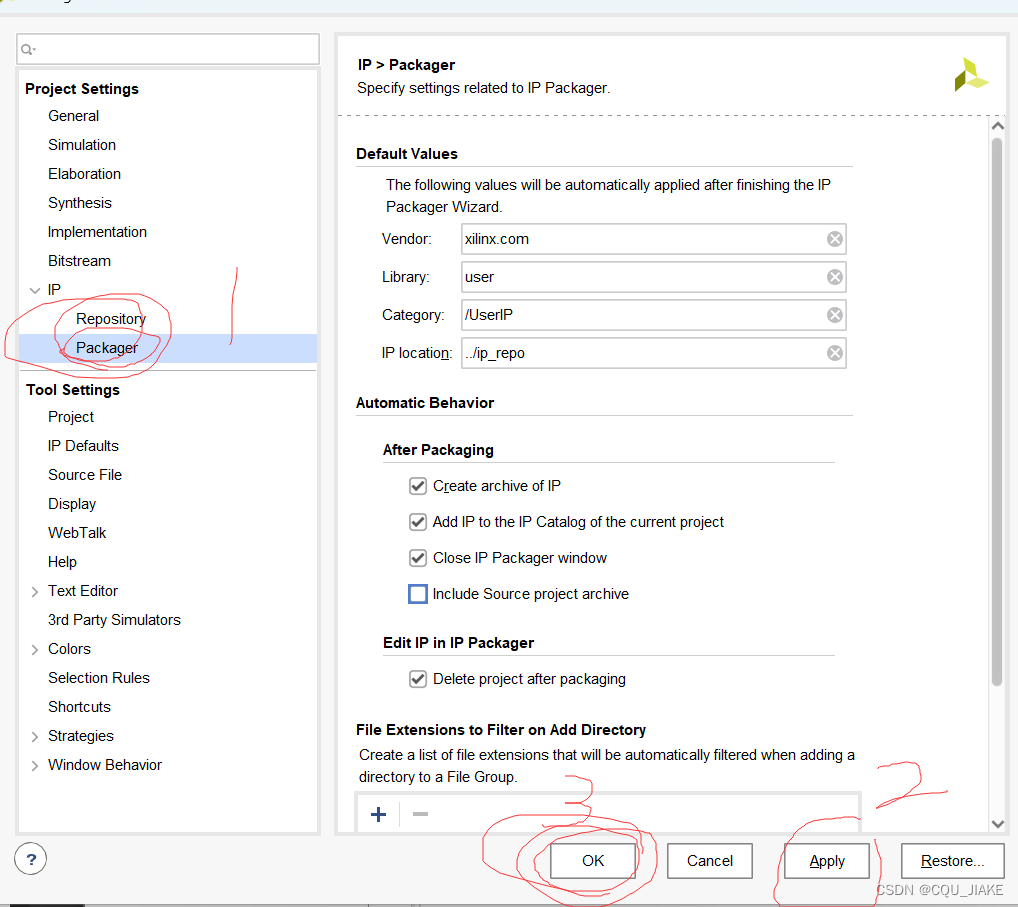

4

5.之后就是一直点下面的next即可

6.

7参数设置,有就整,没有就忽略

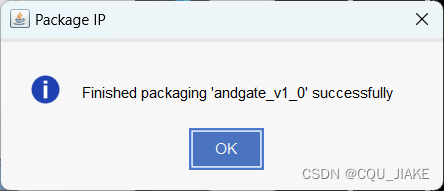

8.最后一步,生成

使用BOLCK DESIGN设计

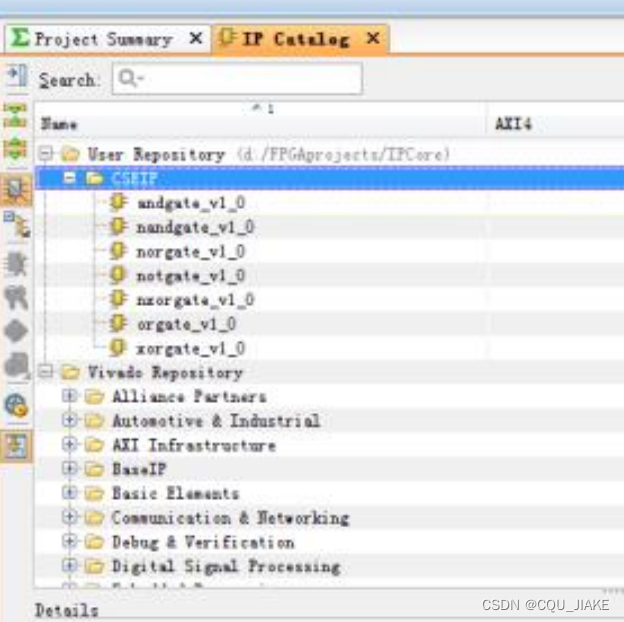

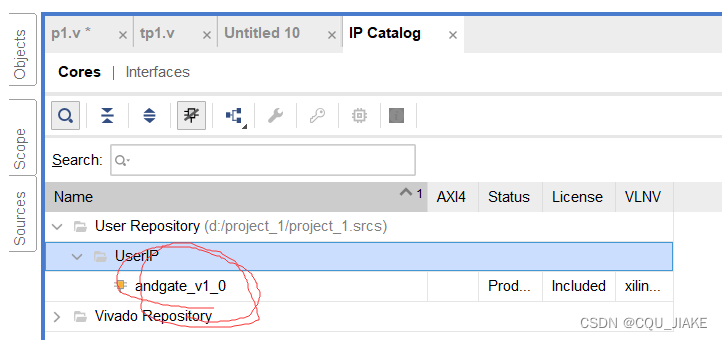

1.创建IP核

即创建块设计中所需要的IP核

在这里的IP Catalog中可以看到已有的IP核

在这里的IP Catalog中可以看到已有的IP核

2.创建bd设计文件

2.创建bd设计文件

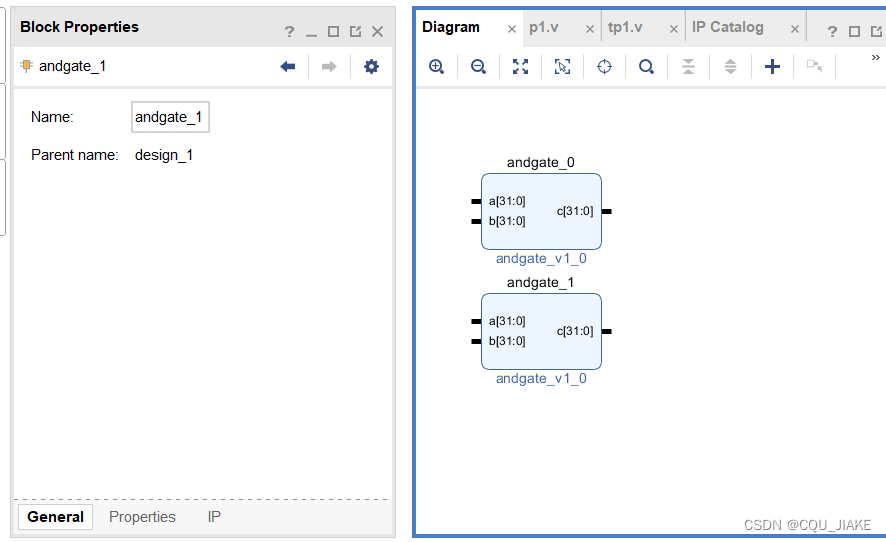

3.将Ip核放入bd文件里

重复这一过程,将不同或相同的块放入文件中

4.放置输入输出端口

放置好后就是连线

放置好后就是连线

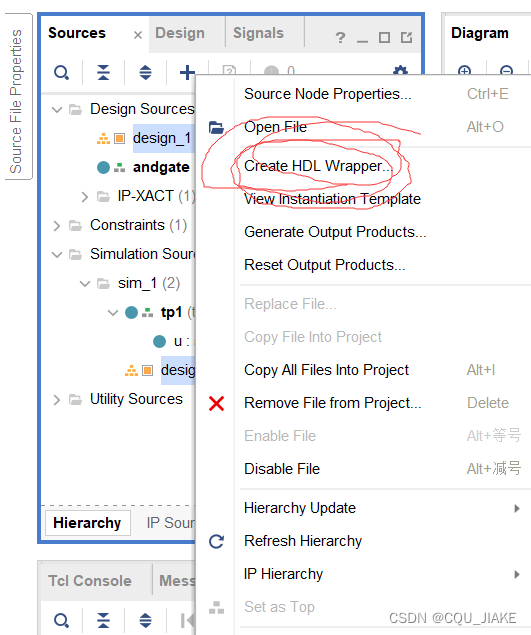

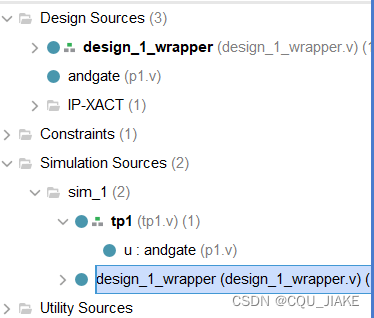

5.生成结果

![论文笔记[156]PARAFAC. tutorial and applications](https://img-blog.csdnimg.cn/62c9ad9a573741e78993eb571431a58f.png)