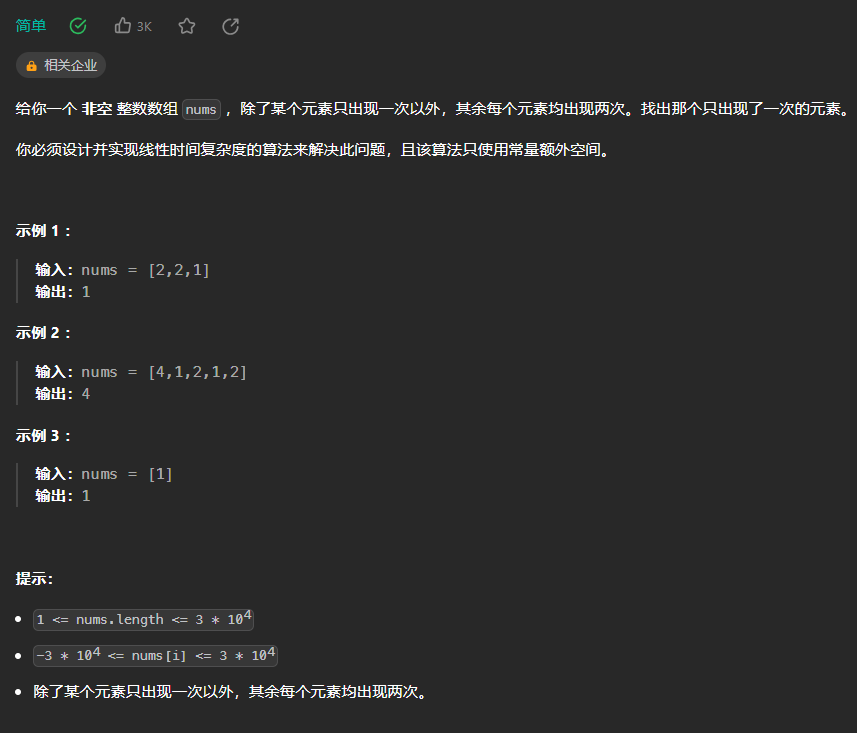

题目要求:

用

M

e

a

l

y

\rm Mealy

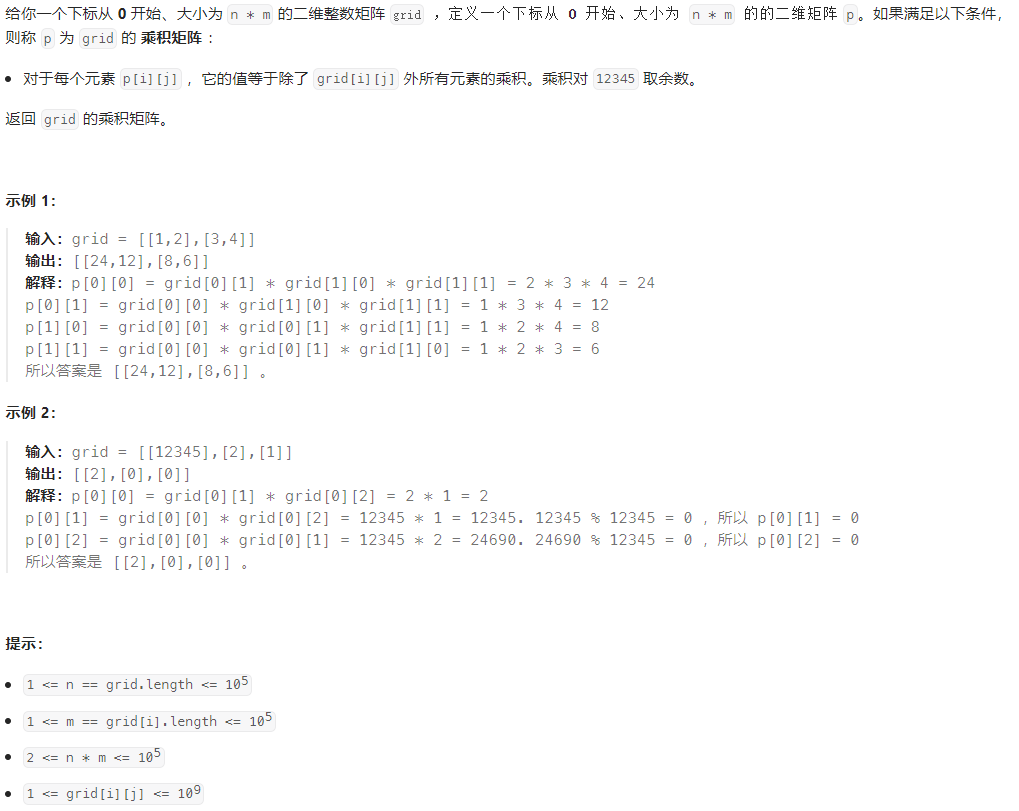

Mealy型状态机验证

1101

1101

1101序列

题目描述:

使用状态机验证

1101

1101

1101序列,注意:允许重复子序列。

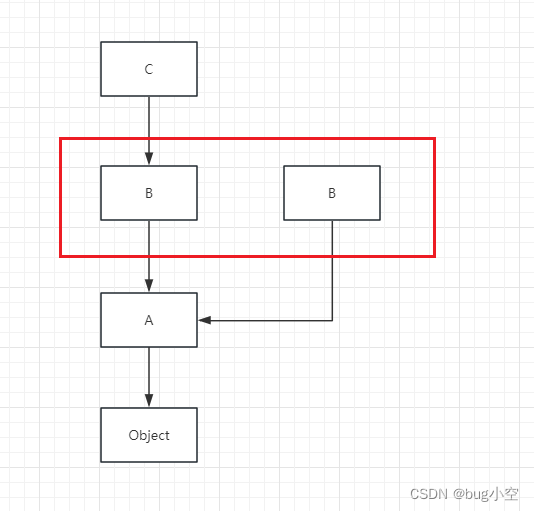

方法一: 去掉 M o o r e \rm Moore Moore的 s 4 s_4 s4,然后将最后一个always的条件改成*。

module mealy_1101(

input clk,

input clr,

input din,

output reg dout);

reg [2 : 0] curr, next;//状态保存

parameter temp = 3'd0, s1 = 3'd1, s2 = 3'd2, s3 = 3'd3;

always @ (posedge clk) begin

if (clr) curr = temp;

else curr = next;

end

always @ (*) begin

case(curr)

temp: next <= din ? s1 : temp;//闲置状态

s1: next <= din ? s2 : temp;//已有一个1的状态,再得到一个1进s2,得到0则进闲置

s2: next <= din ? s2 : s3;//已有11的状态,再得到1进s2,得到0进s3

s3: next <= din ? s1 : temp;//已有110的状态,再得到一个1进s4,得到0进闲置

endcase

end//状态转移

always @ (*) begin

if (clr) dout <= 0;

else dout <= ((curr == s3) ? 1 : 0);

end

endmodule

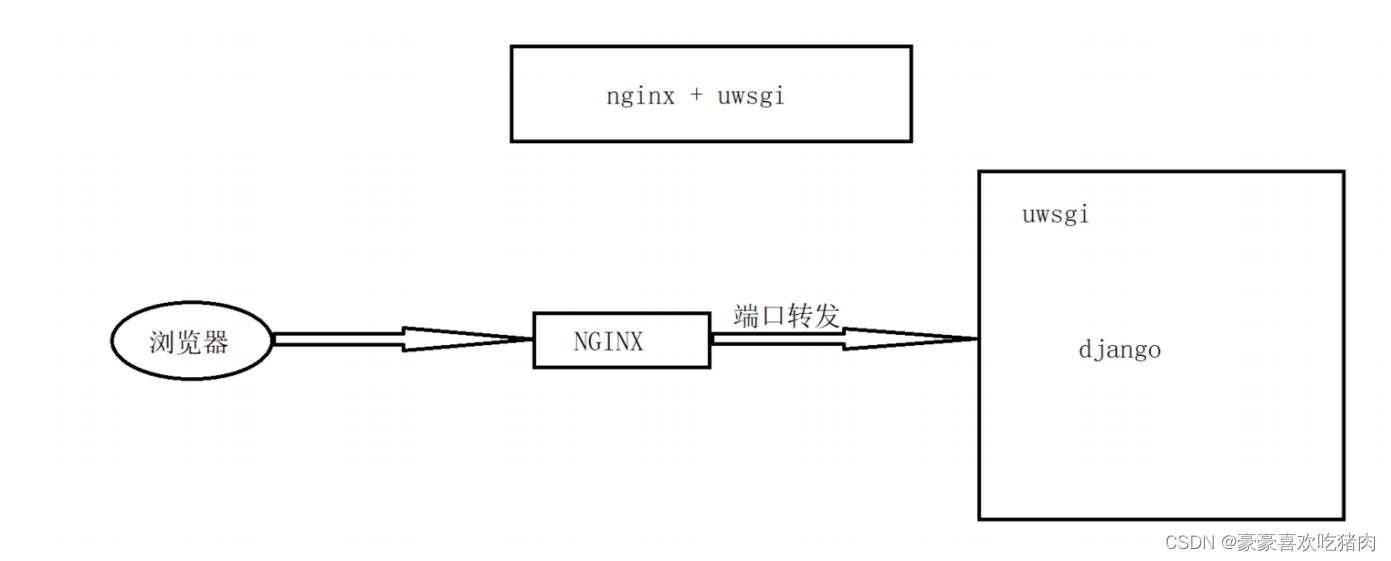

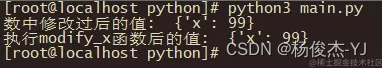

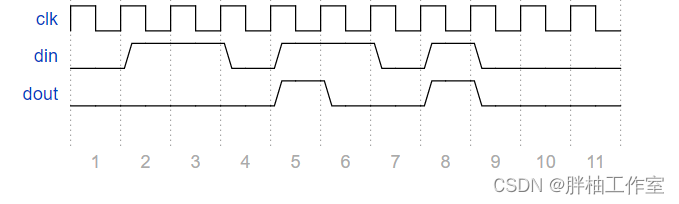

方法二:

上文已经说过,使用

n

n

n个触发器为能解决所有问题的通用解法,那么对于具体问题,我们能否使用更少的触发器实现呢?

答案是可以的

以

1101

1101

1101序列为例

使用

3

3

3个

D

D

D触发器,则在现态为

110

110

110,输入为

1

1

1时输出

1

1

1

输出方程改为

c

o

u

t

=

\rm cout =

cout=

q

2

q_2

q2 &

q

1

q_1

q1 & ~

q

0

q_0

q0 &

x

x

x;

删除

q

3

q_3

q3,此即为

M

e

a

l

y

\rm Mealy

Mealy型电路

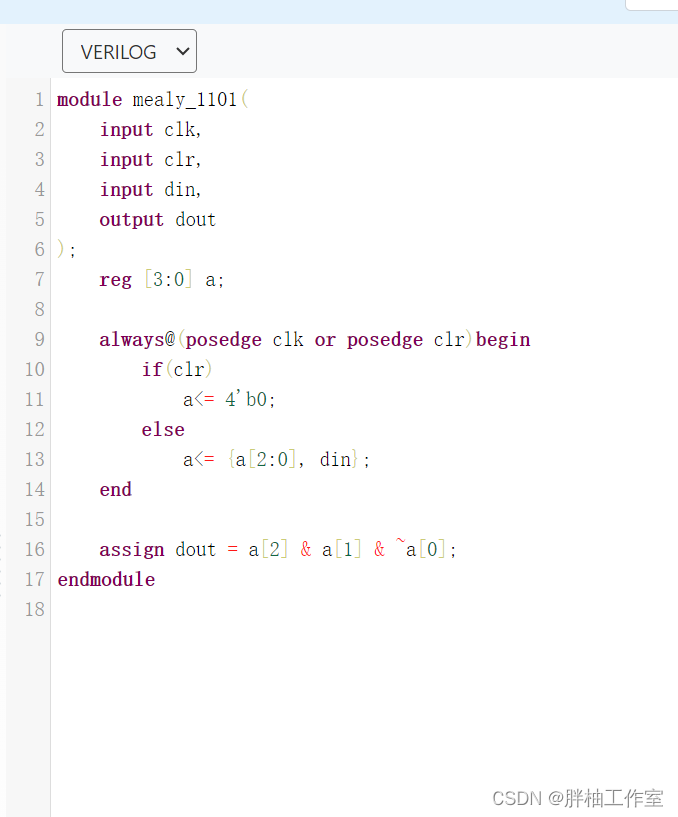

module mealy_1101(

input clk,

input clr,

input din,

output dout);

reg q2 = 0, q1 = 0, q0 = 0;

always @ (posedge clk or posedge clr) begin

if (!clr) begin

q0 <= din;

q1 <= q0;

q2 <= q1;

end

else begin

q0 <= 0;

q1 <= 0;

q2 <= 0;

end

end

assign dout = (({q2, q1, q0, din} == 4'b1101) ? 1 : 0);

endmodule

方法三:

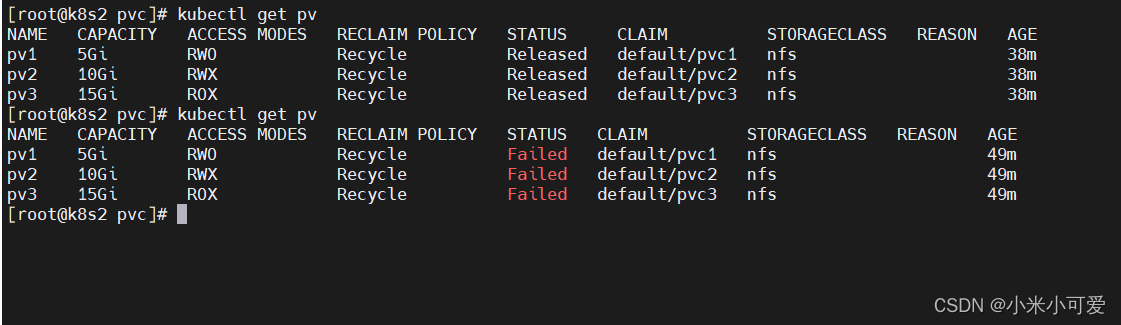

总结:

M

o

o

r

e

\rm Moore

Moore型电路的特点是现态即输出,意思是只有现态影响输出,输入只影响状态转移。

而

M

e

a

l

y

\rm Mealy

Mealy型电路的输出不仅与现态有关,还与输入有关。