实验2 存储器设计与实现【计算机组成原理】

- 实验2 存储器设计与实现

- 一、实验目的

- 二、实验环境

- 三、实验原理

- 四、实验任务

- 五、实验结果:

- 六、心得体会:

实验2 存储器设计与实现

一、实验目的

- 掌握单端口RAM和ROM原理和设计方法。

- 掌握32位数据的读出和写入方法。

- 掌握ModelSim和ISE\Vivado工具软件。

- 掌握基本的测试代码编写和FPGA开发板使用方法。

二、实验环境

- 装有ModelSim和ISE\Vivado的计算机。

- Sword\Basys3\EGo1实验系统。

三、实验原理

片内存储器分为RAM和ROM两大类。RAM是随机存储器,存储单元的内容可按需随意取出或存入。这种存储器在断电后将丢失所有数据,因此一般用来存储一些短时间内使用的程序和数据。

ROM即只读存储器,是一种只能读出事先存储的数据的存储器,其特性是存入的数据无法改变。也就是说,这种存储器只能读不能写。由于ROM在断电之后数据不会丢失,所以通常用在不需经常变更的电子资料。

通常情况下,存储器系统是按照字节(Byte)编址,但CPU访问时,通常按照字(Word)读取,因此地址就有字节地址和字地址的区别。以32位处理器为例,如图2所示。

图2 32位处理器字节编址与字地址示意图

四、实验任务

- 用Verilog HDL设计深度为1K个字单元、每个单元位宽为32 bit的单端口ROM,在Modelsim上完成仿真测试,要求用组合逻辑完成,按照字地址读取,要求读取采用组合逻辑。

- 用Verilog HDL设计深度为1K个字单元、每个单元位宽为32 bit的单端口RAM,在Modelsim上完成仿真测试,要求能够按照字地址进行读和写操作,其中读取用组合逻辑完成,写入用时序逻辑完成。

图3 32位存储器物理结构示意图

五、实验结果:

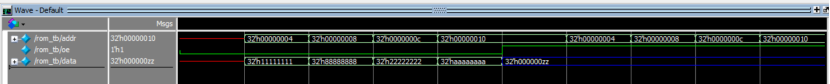

(1)ROM

1.运算程序:

module ROM(addr, data, oe);

output [31:0] data;

input [31:0] addr;

input oe;

reg[31:0] mem [0:1023];

assign data= (oe==0)?mem[addr[11:2]]:8'hzz;

initial

begin

mem[0]=32'hffff_ffff;

mem[1]=32'h1111_1111;

mem[2]=32'h8888_8888;

mem[3]=32'h2222_2222;

mem[4]=32'haaaa_aaaa;

end

endmodule

2.测试程序:

module ROM(addr, data, oe);

output [31:0] data;

input [31:0] addr;

input oe;

reg[31:0] mem [0:1023];

assign data= (oe==0)?mem[addr[11:2]]:8'hzz;

initial

begin

mem[0]=32'hffff_ffff;

mem[1]=32'h1111_1111;

mem[2]=32'h8888_8888;

mem[3]=32'h2222_2222;

mem[4]=32'haaaa_aaaa;

end

endmodule

3.仿真图

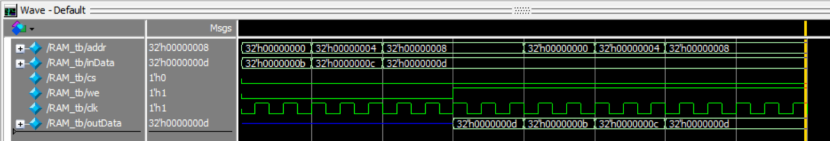

(2) RAM

1.运算程序:

module RAM(

input wire [31:0] addr,

input wire [31:0] inData,

input wire cs,

input wire we,

input wire clk,

input wire [31:0] outData

);

reg [31:0] memData [1023:0];

assign outData=(!cs&&we)?(memData[addr[11:2]]):(32'hzz);

always@(posedge clk)

if(!cs&&!we)

memData[addr[11:2]]=inData;

else;

endmodule

2.测试程序:

module RAM_tb;

reg [31:0]addr;

reg [31:0]inData;

reg cs,we;

reg clk;

wire [31:0]outData;

RAM U1(addr,inData,cs,we,clk,outData);

always #10 clk=~clk;

initial

begin

cs=0;we=0;

clk=0;addr=0;inData=11;

#50 addr=4;inData=12;

#50 addr=8;inData=13;

#50 we=1;

#50 addr=0;

#50 addr=4;

#50 addr=8;

end

endmodule

3.仿真图

六、心得体会:

通过本次实验的学习,我掌握了单端口RAM和ROM原理和设计方法;掌握了32位数据的读出和写入方法;掌握了ModelSim和ISE\Vivado工具软件;掌握了基本的测试代码编写和FPGA开发板使用方法。