双稳态多谐振荡器配置

文章目录

- 双稳态多谐振荡器配置

- 1、概述

- 2、双稳态多谐振荡器的内部运行原理

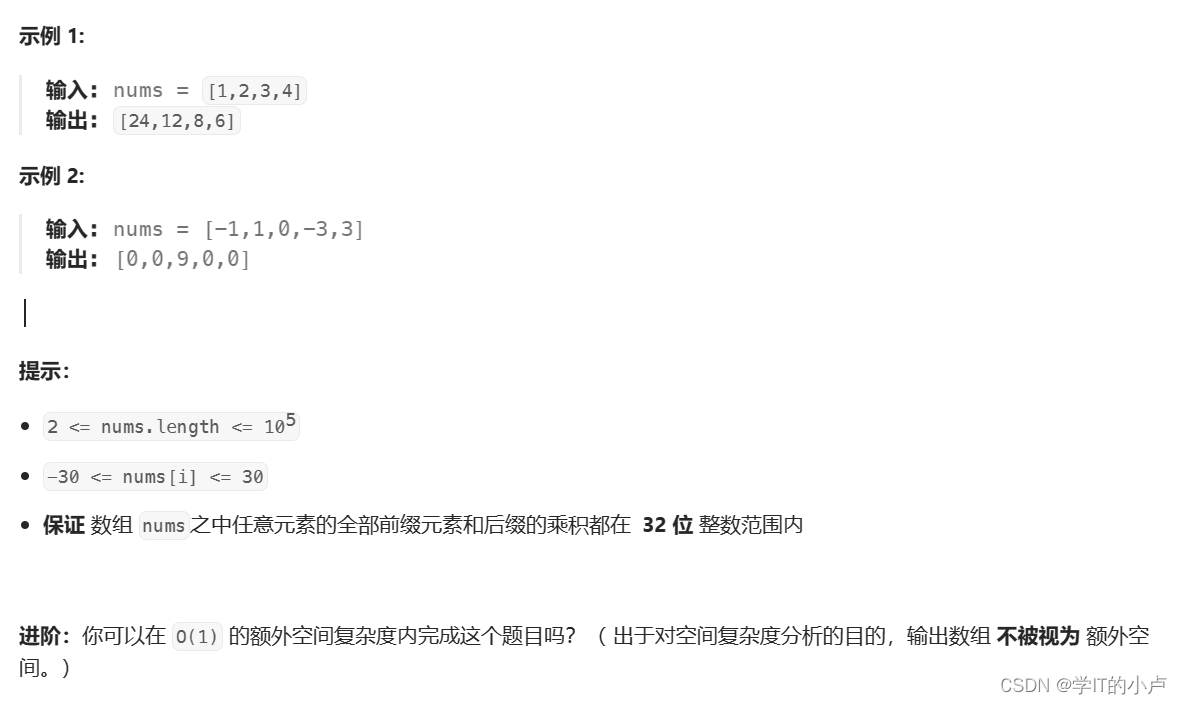

在上一篇文章中,我们深入了解了555定时器在单稳态模式下的内部工作原理。 如果您已经理解了上一篇文章,那么本文对您来说将会非常简单。 我们将研究 555 定时器的双稳态模式,这实际上是所有模式中最简单的模式。

让我们首先了解简单双稳态多谐振荡器的行为,然后我们将了解如何使 555 定时器具有与它类似的行为。

1、概述

“双稳态”这个名称是不言自明的。 双稳态多谐振荡器是具有两种稳定状态的电子器件。 这意味着电路保持在两种状态(高电平或低电平)中的任何一个,除非外部触发在它们之间切换。 在前面的教程中,我们解释了单稳态多谐振荡器在触发时如何在不稳定状态停留一定时间后自动返回到稳定状态。 然而,对于双稳态多谐振荡器,我们需要第二个触发器才能使其返回到原始稳定状态,即它不会自动返回。 这是单稳态多谐振荡器和双稳态多谐振荡器之间的主要区别。 现在我们来谈谈如何配置 555 定时器以充当双稳态器件。

555 定时器的双稳态模式通过连接到定时器外部引脚的两个上拉配置进行控制。 我们可以使用电阻器和开关轻松地进行上拉配置。

- 使用电阻器 R1 和开关 S1 构成的第一个上拉网络连接到定时器的触发引脚 (2)。

由R2和S2组成的第二个上拉网络连接到定时器的复位引脚(4)。 复位引脚是低电平有效引脚,因此只有当逻辑低电平施加到该引脚时,触发器才会复位。 - 控制引脚 (5) 通过 10nF 电容器接地。

- 我们只需将定时器的放电引脚 (7) 保持未连接状态,因为在这种操作模式下,没有任何电容器可以充电或放电。

- 在此模式下阈值引脚接地,以避免由于触发器的 R 输入导致意外复位。

2、双稳态多谐振荡器的内部运行原理

双稳态模式的工作原理非常容易理解。 最初,两个开关都打开。 因此定时器的触发引脚和复位引脚都以VCC或逻辑高电平作为输入。 这意味着下比较器或触发比较器的反相输入上的电压为 VCC,非反相输入上的电压为 1/3VCC。 因此,下比较器输出逻辑低电平,这意味着触发器的 S 输入也是逻辑低电平。

正如您在原理图中看到的,我们已将阈值引脚接地。 在这种情况下,上比较器反相输入上的固定参考电压 2/3VCC 将始终大于比较器非反相输入上的电压。 这就是为什么比较器将始终输出逻辑低电平,并且触发器的 R 输入也将始终为逻辑低电平。

因此,当两个开关最初都打开时,触发器的 S 和 R 输入上的输入均为逻辑低电平,并且触发器被称为已进入存储状态。 因此,触发器的输出为 Q(逻辑低电平)和 Q ‾ \overline Q Q(逻辑高电平)。 由于输出驱动电路是反相电路,因此我们得到逻辑低电平作为定时器的输出。

当我们关闭触发开关(S2)时,操作开始。 这使得触发引脚上的输入为逻辑低电平,因为现在触发引脚的最小电阻路径是通过触发开关通向地面。 这使得下比较器的反相输入小于非反相输入,并将比较器的输出从逻辑低电平更改为逻辑高电平。 这里需要注意的重要一点是,开关仅关闭一段时间,然后再次打开。 但这个短脉冲足以触发并改变计时器的输出。

下部比较器处的逻辑高电平设置触发器并使 Q 逻辑高电平和 Q ‾ \overline Q Q为逻辑低电平。 因此我们得到定时器的输出作为逻辑高电平信号。

由于开关在施加信号后立即重新打开,因此下部比较器将输出更改回逻辑低电平。 这使得触发器进入存储器状态,定时器的输出为逻辑高电平。 即使在这种情况下我们再次关闭触发开关(S2),也不会改变定时器的输出。 输出将保持高电平状态,直到我们关闭复位开关 (S1)。

此时,当复位开关(S1)短暂闭合时,定时器的复位引脚会短路到地。 这在复位引脚上提供了逻辑低电平。 如前所述,因为复位引脚是低电平有效引脚,所以闭合开关会复位触发器,并且触发器的输出Q变为逻辑低电平并且 Q ‾ \overline Q Q变为逻辑高电平。 因此定时器的最终输出重置回逻辑低电平。 定时器现在再次达到初始稳定状态,准备下一次输入。

下图表示555定时器双稳态模式的完整输出波形。 您可以在图中看到,当触发器拉低时,输出切换为高电平,当复位引脚拉低时,输出切换回低电平。

就是这样! 现在你了解了555定时器的另一种模式。 我们希望您喜欢阅读它。 在下一个教程中,我们将了解 555 定时器最有趣和最有用的配置:非稳定模式。

![[代码随想录]二叉树篇](https://img-blog.csdnimg.cn/d4219b2c993f482595477b43219d2ae9.png)