通用串行总线(USB)完全取代了PC上的UART,PS2和IEEE-1284并行接口,现在已在嵌入式开发应用程序中得到广泛认可。嵌入式开发系统使用的大多数I / O设备(键盘,扫描仪,鼠标)都是基于USB的。

由于USB是USB联盟所保证的明确定义的标准,因此任何供应商提供的经过USB认证的设备都可以即插即用的方式与任何其他供应商提供的经过USB认证的设备一起使用。

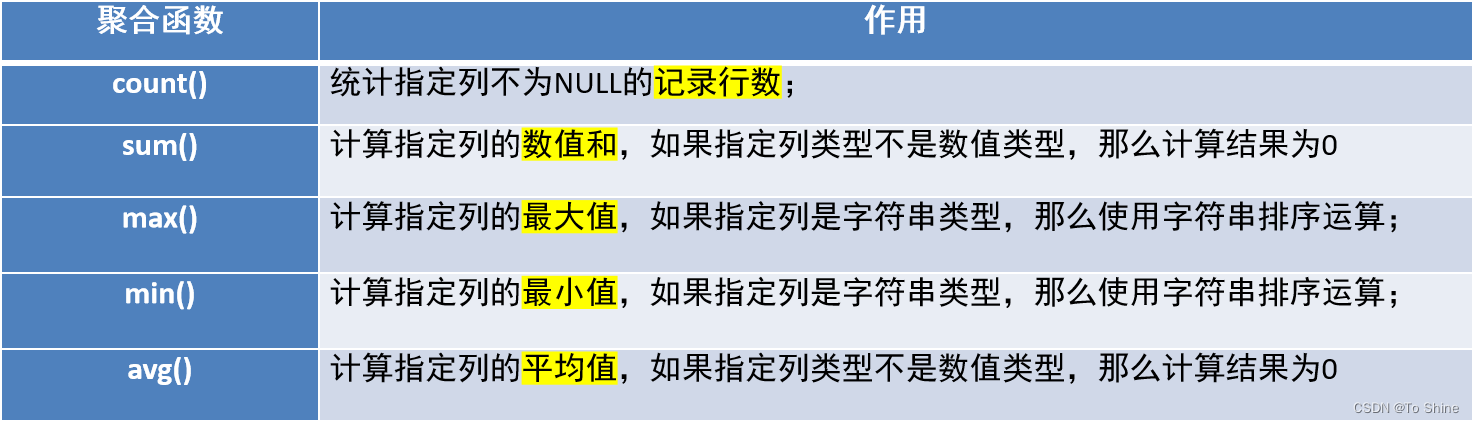

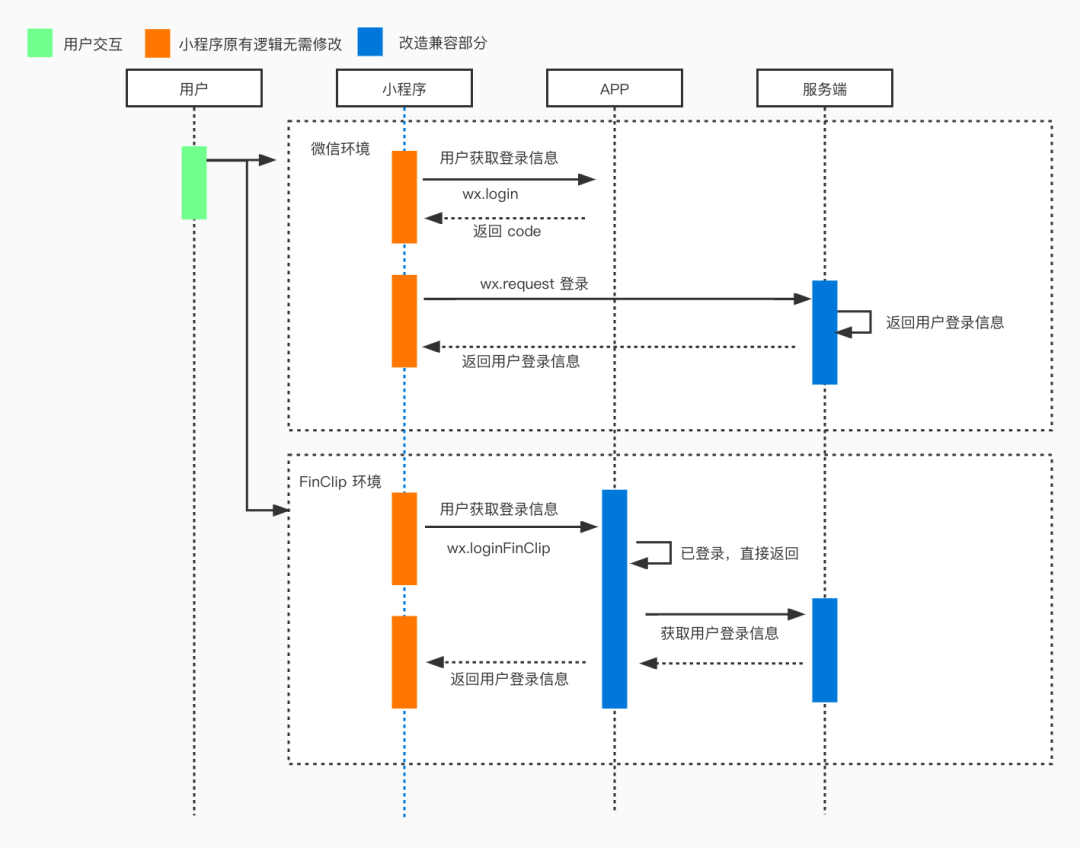

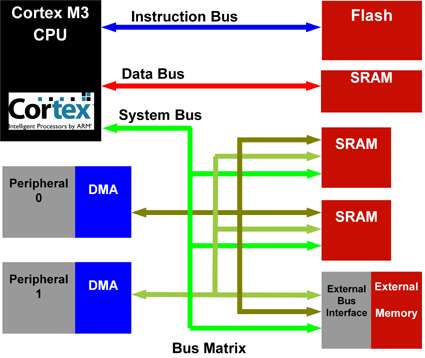

多个设备可以在同一总线上运行,而互不影响。绝大多数32位闪存MCU和MPU供应商都提供某种形式的USB接口作为标准外设一点也不奇怪,USB主机,USB设备,USB OTG通常限于“全速”规格,即12 Mbps(下图1)。

图1. USB框图

现在,USB标准旨在解决嵌入式开发系统的另一个问题:数据速率的指数级增长。五年前,人们认为10 Mbps的数据速率很高。12 Mbps全速USB,10 Mbps SPI或400 kps I2C接口可以满足几乎所有嵌入式应用程序的数据需求。

但是,如今,随着日志文件大小的不断增加以及用户界面的日益复杂化的出现,甚至数十Mbps的数据速率也不足以提供足够的用户体验。千兆字节的日志文件必须在10秒钟内在系统之间传输,并且将从系统内不同PCB收集的信息传输到图形显示单元。

输入“高速” USB。凭借480 Mbps的带宽,高速USB可以满足当今对数十Mbps的需求,以及未来对百Mbps的需求。它提供了一种易于理解且易于使用的工具,可以处理系统之间以及系统内部的印刷电路板(PCB)之间的大量数据和互连。

毫无疑问,它将很快用于单个PCB上的芯片间通信,从而绕开了物理层并消除了对电缆连接的需求。预计支持该技术的系统将于2009年投放市场。

显然,微控制器将必须增加USB HS支持以跟上市场发展。但是问题是:如何构建一个微控制器,可以处理来自480 Mbps USB接口的数据负载,同时又能满足嵌入式系统的功耗和实时限制。

在一个400MHz的基于ARM9的微处理器中保持480 Mbp的数据速率,并且将片上高速缓冲存储器连接到单个平面高速外部存储器非常容易。在相对较慢的闪存上运行的,在100 MHz Cortex M3闪存MCU上运行它是另外一回事。

Cortex-M3是否可以在运行诸如数据处理算法,文件系统和通信协议之类的过程密集型任务时处理所有这些数据传输?

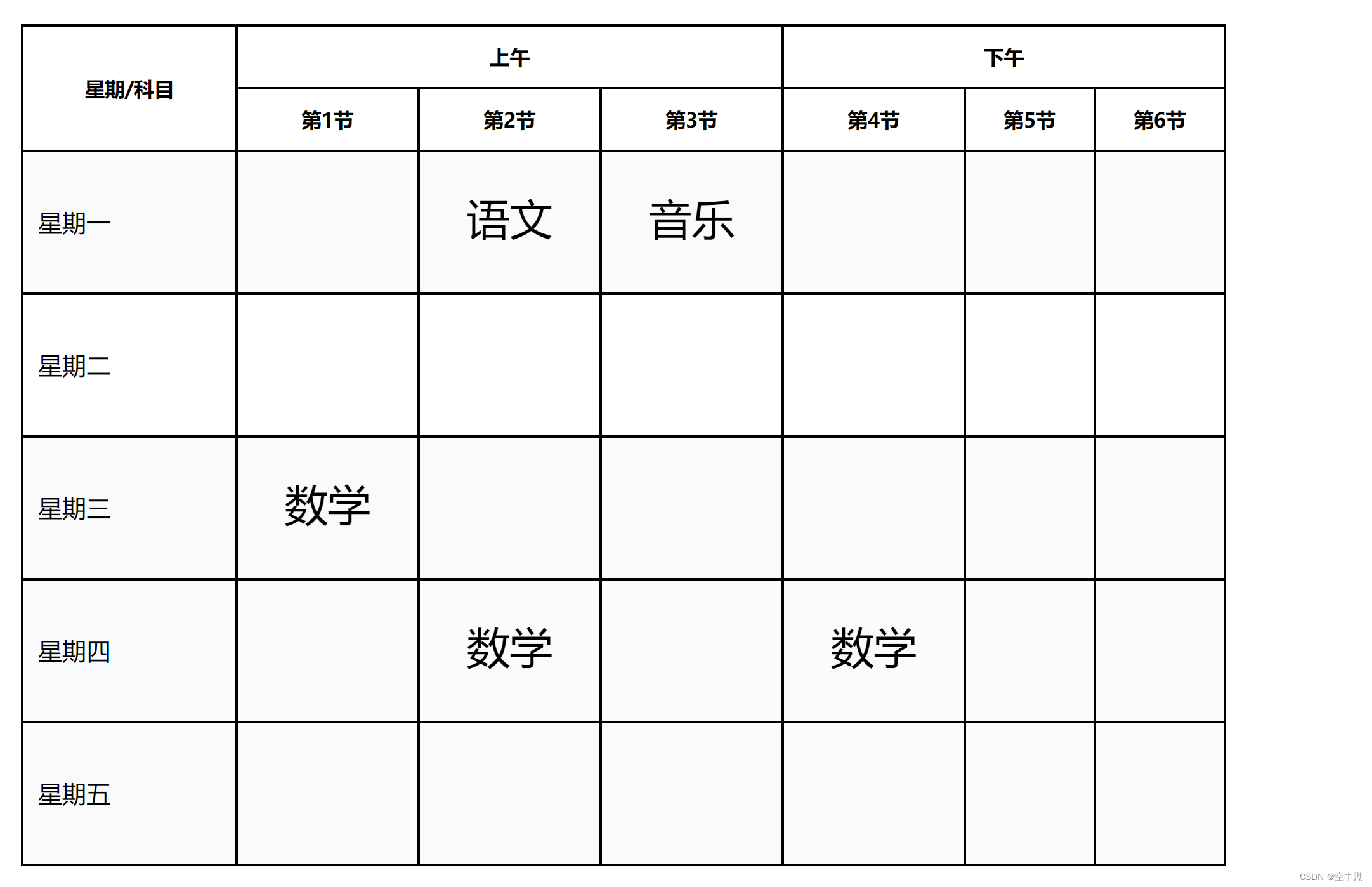

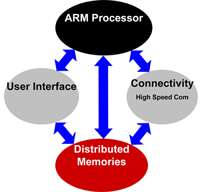

解决此问题的方法是将ARM9微处理器中使用的多层总线体系结构(下面的图2)适应Cortex M3,并将存储器空间分为多个分布在体系结构内的块,以确保高速时的实时关键处理。数据通过DMA并行传输。

图2.高数据速率架构。

直接内存访问(DMA)至关重要。使用CPU进行传输会导致CPU过载,可能会阻止CPU处理应用程序和实时控制任务。理想情况下,必须将三种类型的DMA连接到所有低速和高速外设,以最大程度地减少总线和存储器上的数据传输负载,并使处理器腾出空间进行数据处理和系统控制任务。

带有内置缓冲区的DMA相对较大,仅保留给最高速度的接口,以提高对总线等待时间和突发传输的耐受性以及对链表的支持。

它们提供了高度的CPU独立性和最低的总线使用率。由于每个通道的成本较高,因此无法在每个片上外设上全局使用这些功能齐全的DMA。

多种DMA实现方案在成本和性能之间取得了平衡,并结合了外围DMA控制器(PDC),该控制器以最低的复杂度和最简单的使用方式直接将低数据速率的外围设备链接到存储器,并专门针对并优化了经过调谐的DMA控制器用于最高带宽的外围设备,以及针对存储器到存储器和存储器到高速外围设备块传输进行了优化的中央DMA。

由于DMA控制器完全独立于处理器运行,因此消除了中断开销,并大大减少了数据传输所需的时钟周期数。

降低成本的DMA实现是外围DMA控制器或PDC,它紧密集成在外围编程器的空间中。PDC带来了整体系统性能,成本和易于编程的优势。

PDC通道的用户界面集成在每个外设的存储空间中。它包含一个32位存储器指针寄存器,一个16位传输计数寄存器,一个用于下一个存储器指针的32位寄存器以及一个用于下一个传输计数的16位寄存器。

当外设接收到外部字符时,它会向PDC发送一个接收就绪信号,然后请求访问系统总线。授予访问权限后,PDC开始读取外设接收保持寄存器(RHR),然后触发对存储器的写操作。

每次传输后,相关的PDC内存指针都会增加,剩余的传输次数将减少。当达到存储块大小时,下一个块传输将自动开始,或者将信号发送到外围设备,然后传输停止。相反,遵循相同的过程进行传输传输。

当传输第一个编程数据块时,相应的外设会产生传输结束中断。第二个块的数据传输会自动开始,并且第一个块的处理可以由ARM处理器并行执行,从而消除了用于更新处理器上DMA内存指针的繁重的实时中断约束,并维持了15至20Mbps的速度任何外围设备上的数据传输。

如果在相同的外围设备上同时发生相同类型的请求(接收器或发送器),则优先级由外围设备的编号确定。如果传输请求不是同时发生的,则将按照发生的顺序对其进行处理。首先处理来自接收方的请求,然后处理发送方请求。

高于10 Mbps时,访问内部总线和内存的时间变得至关重要,并且两级深度的接收和发送缓冲区不再足以维持连续传输。需要具有更深缓冲区并能够突发数据传输的中央DMA。

该中央DMA具有内置FIFO,可提高对总线延迟的容忍度,可编程长度突发传输,可优化每次传输,分散,收集和链接列表操作的平均时钟周期数。它可以编程用于存储器到存储器的传输或存储器到外设的存储器,例如48Mbps SPI,4位192 Mbps SDIO / SDCard 2.0或8位384 Mbps MMC 4.3主机接口。

每个专用DMA在总线矩阵上都有自己的层,从而消除了任何总线访问延迟。这些DMA针对诸如高速USB接口,以太网MAC或LCD控制器之类的高速外围设备进行了优化,以在最短的时间内最大化数据传输。

对于7端点高速USB设备接口,此类DMA将集成4kB DPRAM存储器以存储完整的数据包有效负载并防止缓冲区下溢和溢出。该DMA由几个通道组成,每个通道专用于一个端点。DMA通道将在DPRAM和USB控制器内的多个存储体之间传输数据。

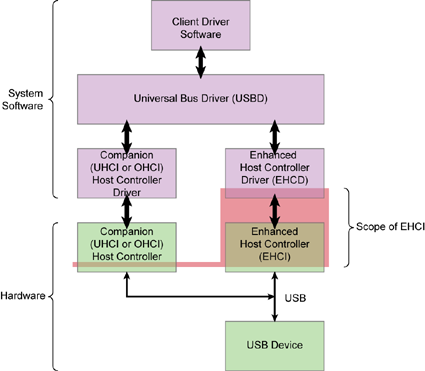

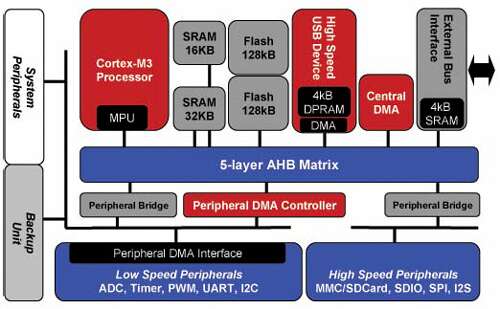

图3. SAM3U框图

最多3个存储体应分配给单个端点以存储微帧。在带有5层总线矩阵和两个中央SRAM存储器的96MHz的Cortex M3 MCU上的这种高速USB实现(上图3)可以维持480 Mbps的最大带宽。

回忆。 Cortex M3处理器具有三个内存总线:指令总线(I),数据总线(D)和系统总线(S)。M3上的此总线体系结构与单总线ARM7体系结构有很大不同。除了在S总线上提取指令外,所有其他总线都为处理器提供单周期内存访问。

有两种选择可从Cortex M3获得最高的指令取回速度并克服闪存的访问时间限制:在I总线上连接单周期访问SRAM或增加闪存的宽度以支持多条指令读取和因此,顺序指令提取加速。

只有SRAM的速度足以匹配Cortex M3处理器的最大96 MHz工作频率。但是,通过将多个片上SRAM存储器用于指令和数据存储来优化性能会增加成本和待机功耗。使用价格便宜,低泄漏的非易失性闪存会带来另一个问题:闪存无法以与Cortex M3处理器相同的频率运行。

典型的闪存访问时间在35至50ns的范围内,而Cortex M3时钟周期约为13 ns。为了补偿较长的闪存访问时间,可以将闪存的宽度增加到64位或128位,分别对应于四个和八个指令(拇指2)。

这种方法允许在每个周期读取多个顺序指令,将其存储在寄存器中,然后以完整的96 MHz时钟速率执行,而没有任何等待状态。

SRAM还应用于存储数据并用作暂存器。为了最大化性能,需要将SRAM存储器分为多个块,以允许处理器和外设通过多总线体系结构的并行总线将数据移入和移出。这样的模块可以直接集成在高带宽外围设备中,或在软件控制下用作分配给CPU和外围设备的中央存储器。

连接到Cortex M3 D总线的数据存储器不与其他片上外设或DMA共享。这带来了一个难题:1)如果数据存储器在S总线上共享,并且因此放弃一些原始性能以换取允许DMA在没有CPU干预的情况下将数据加载和存储在存储器中,或者2)如果数据存储器连接到D总线并使用处理器移动数据。

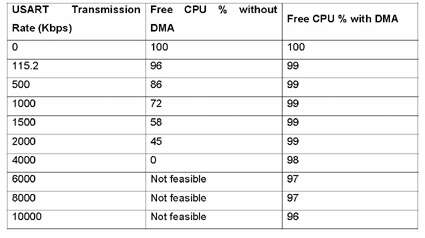

下表1中的PDC基准 运行在SAM7X处理器上,清楚显示了在具有多个通信通道的微控制器中,最大程度地提高数据传输的DMA使用率的好处。

表1:在SAM7X闪存微控制器上以Thumb模式从55MHz的闪存读取基准测试

具有高速USB接口的Cortex M3微控制器通常将在芯片上具有其他高速通信或存储接口。为了在这些接口之间维持较高的数据传输速率并进行协议转换,应并行,多个共享的SRAM块实现数据处理和系统控制功能,以实现最佳的系统性能。

DMA和处理器S总线可以作为总线主控器连接到片上多层总线矩阵,并可以直接访问共享存储器的块。

如果目标是创建数字处理器并传输有限数量的数据,则必须将SRAM放在I&D总线上。在这种情况下,性能关键代码的一部分应在连接到I总线的SRAM中被遮蔽,以在100MHz操作下释放完整的1.25 DMIPS / MHz。

当程序和数据存储需要片外存储器时,通常使用Cortex M3 S总线,因为它结合了指令和数据提取功能,从而将外部总线限制为一条总线。这种折衷导致性能从1.25 IPSIPS / MHz突然下降到0.9 DMIPS / MHz,这是由于S总线上的指令提取要比I总线多一个周期。

内部总线体系结构和外部存储器总线控制器实现的效率决定了在外部存储器中执行时获得的最终性能。

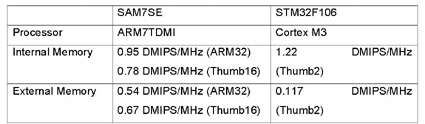

表2:最高性能基准,Dhrystone 2.1,RVCT编译器和链接器,性能优化,零等待状态内存

上面的表2 比较了具有外部总线接口(EBI)的ARM7和Cortex M3 MCU的实现。基于ARM7的EBI可以维持0.54至0.67 DMIPS / MHz,而Cortex M3器件上的EBI仅限于0.117 DMIPS / MHz。对于微控制器的选择过程,显然需要考虑对外部存储器的执行进行基准测试。

多层总线。 数据密集型应用面临的另一个问题是片上总线带宽。当多个DMA控制器和处理器通过一条总线推送大量数据时,总线可能会变得过载,并降低整个系统的速度。时钟频率为48 MHz的32位总线的最大数据速率为每秒15亿位(Gbps)。

尽管听起来很多,但是在数据密集型应用程序中,可能有太多数据,总线本身就成为了瓶颈。USB高速SDIO网关就是这种情况,每个网关的数据速率都超过100 Mbps。使用优化数据传输的DMA,几乎没有带宽留给处理器访问共享数据存储器。

通过提供多个并行的片上总线(也称为多层总线矩阵)可以避免这种情况。与仅支持单层ASB总线的ARM7相比,Cortex M3处理器具有对多层总线的本机支持。因此,Cortex M3是具有高速USB的微控制器的更好处理器。

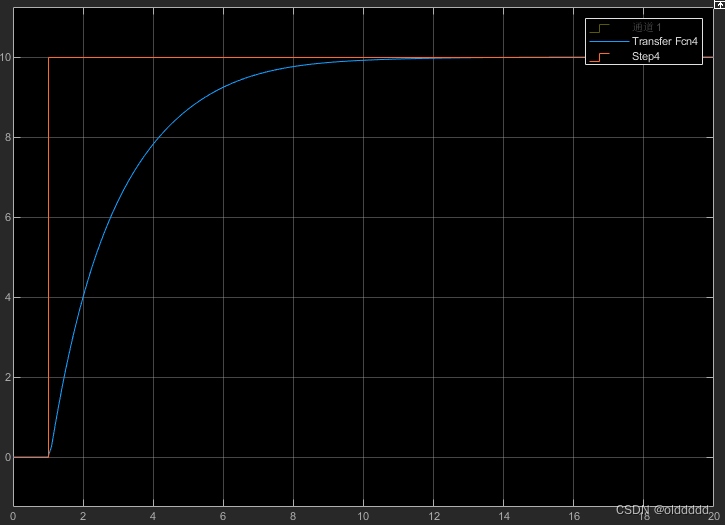

在多层(AHB)总线上(下面的图4),处理器和芯片中的不同DMA控制器在总线上都有各自的专用层。

图4. SAM3U多层总线和内存

当多个外设共享一个DMA通道或共享存储器时,仲裁器设置优先级。使用的仲裁策略示例为固定优先级主机,无默认主机,上次访问的默认主机或固定默认主机的循环仲裁。

AHB总线相对于ASB总线

的优势AHB总线相对于ASB总线具有主要优势,因为它是为并行数据传输而设计的。可以将可配置数量的总线并行路由到连接到处理器的主总线。

直接内存访问控制器(DMA)应该使用这些附加总线之一将数据从外设传输到内存或从内存传输到内存,而无需处理器的干预。在ARM7 ASB架构上,DMA将窃取处理器的总线,并阻止其从片上和片外存储器中获取指令或数据。

最后,通过增加控制器中易失性存储块的数量,可以减少对共享存储器的访问冲突,并消除了另一个性能瓶颈。存储块可以直接集成在高带宽外围设备中,或在软件控制下用作分配给处理器或外围设备的中央存储器。

因此,可以创建基于Cortex-M3的实现,该实现可以在最高1.8 MHz的96 MHz和1.62 V的84MHz的最大时钟速率下达到480 Mbps的数据传输速率,单周期为1.25 DMIPS / MHz乘除。

实现这一壮举的关键是在总线接口中采用低门数,高效的多通道DMA架构,该架构采用低门数,易于使用的DMA,能够在每个通道的每个通道上维持高达20 Mpb的速率。中低端数据速率外设。

此外,应使用中央DMA通道和专用的USB高速DMA来支持每个外设几百Mbps的更高数据速率。使用此设置,处理器只会干预以开始每次数据传输,并且在传输完成时会被中断提醒。

这种安排几乎减轻了处理器的全部数据传输负担,从而使处理器能够确定控制和数据处理任务的优先级。Cortex M3中断控制器确定性地在最多12个指令周期内处理中断。如果使用尾链链接,中断等待时间将降至6个周期,从而进一步减少了切换任务时的处理器开销。

最后,USB 2.0高速(480 Mbps)提供的更高速度使其比绝大多数其他接口更快,从而可以在最短的时间内传输大量数据,从而改善了系统的用户体验。

DMA和存储器的正确组合可以增加确定性Cortex3 MCU的资源,以轻松处理高速USB,从而为微控制器中当前和将来的数据需求提供了有效的解决方案。