文章目录

- 1.1 DMC-400 简介

- 1.1.1 DFI(DDR PHY Interface)

- 1.1.2 DFI 接口组

- 1.1.3 DMC-400 兼容协议

- 1.1.4 DMC-400 特性

- 1.1.5 DMC-400 Interface

1.1 DMC-400 简介

DMC-400是一个由ARM开发、测试和授权的动态内存控制器,同时 DMC-400也是一个符合高级微控制器总线结构(AMBA)的片上系统(SoC)外设。它是一个高性能、区域优化的内存控制器,与 AMBA ACE-Lite 协议兼容。

它支持以下内存设备:

-

双倍数据速率2(DDR2)同步动态随机存取存储器(SDRAM);

-

低功耗双倍数据速率2(LPDDR2)-S2 SDRAM;

-

LPDDR2-S4 SDRAM;

-

双倍数据速率3(DDR3)SDRAM;

-

低电压 DDR3 SDRAM。

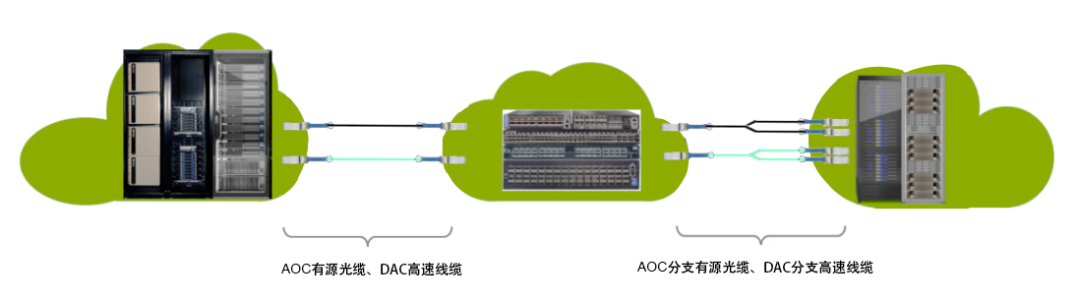

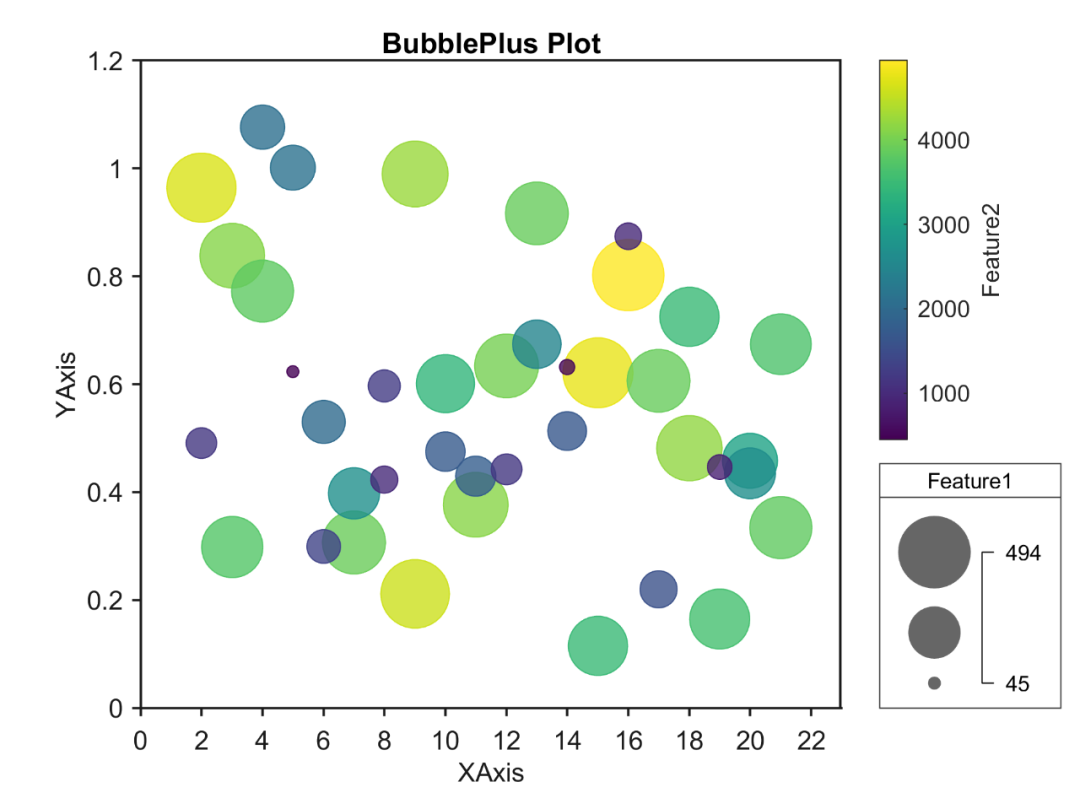

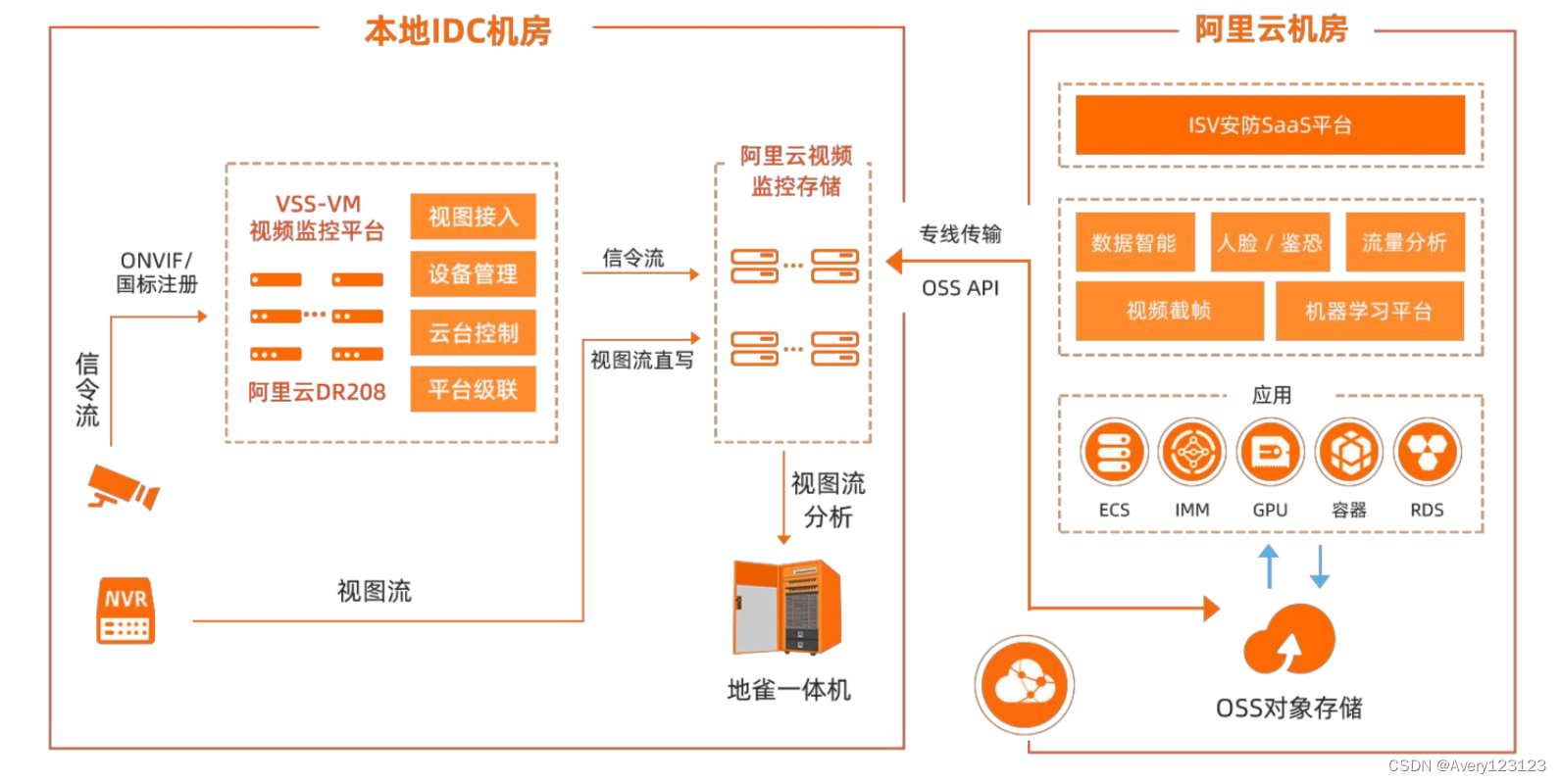

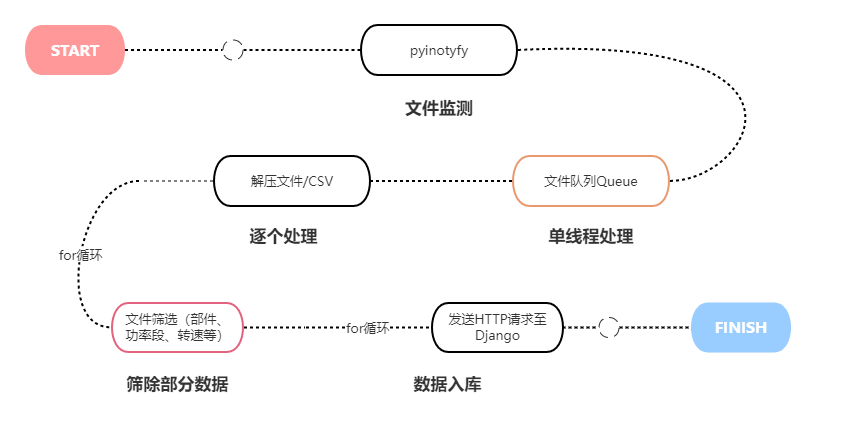

下面是 DMC-400 系统连接示例图:

DMC-400 实现了 SoC 和芯片外部 DRAM 设备之间的数据传输。它通过一个或多个 ACE-Lite 接口连接到片上系统。它通过其存储器接口块和 DFI 接口 连接到 DRAM 设备。

1.1.1 DFI(DDR PHY Interface)

现代电子系统设计中,经常将DDR内存接口分成内存控制逻辑(MC,Memory Controller)和物理层接口(PHY,Physical Interface)两个部分。这两个部分侧重点不同,往往需要不同的设计技巧和设计经验。

随着IP(intellectual property)厂商的发展,越来越多的工程师选择在设计中采用第三方的IP核,来加速项目进度。这就带了问题,由于MC和PHY两部分的设计者往往并不相同,为了能够实现两者之间的标准互联,需要一种 MC 与 PHY 之间的标准通信接口。而DFI就是这样的一种规范。DFI标准的提出旨在定义一个MC与PHY之间的通用接口,以提高独立模块(IP核等)的复用率,进而降低成本,缩减项目周期。

一般来说,DRAM 是一个焊接在 PCB 上的独立芯片,CPU 向 MC 发出读写命令时,其中的地址使用的是逻辑地址,MC 再将逻辑地址转换为物理地址后向 PHY 发出,MC 与 PHY 之间采用标准化接口 DFI 进行通信,PHY 将 MC 的命令转换为具体的底层信号,驱动 DRAM 的物理 IO 接口。

1.1.2 DFI 接口组

DFI 接口组共有:

- Command(发送地址命令),

- write data,

- read data,

- updata(请求更新,启动dfi总线idle),

- status(系统初始化,Feature支持与否, mc给到dram的时钟有效性),

- phy master(phy 请求控制dfi总线,发起主动能力),

- Disconnect(传输过程中允许握手打断),

- error(事务中的错误信息传递给MC),

- 2N mode(将dram的传输速度减速),

- Low Power Control(PHY 进入低功耗功能),

- MC TO PHY MESSAGE(将定义的信息内容从mc传递到phy),

- WCK Control(控制DRAM 用的WCK时钟开关是否toggle, 以及 同步计时功能)。

DFI 中定义的信号,都是由寄存器配置完,在时钟上升沿驱动起来的。dfi bus上执行命令的时候, 相关时序参数必须一致保持。必要的时候, 比如 频率改变, bus 执行到 idle状态等, 时序参数也可改变。

1.1.3 DMC-400 兼容协议

它实现了与以下协议的兼容:

-

ACE-Lite协议;

-

AMBA3 APB协议;

-

JEDEC LPDDR2 JESD209-2标准;

-

JEDEC DDR3 JESD79-3D标准;

-

JEDEC DDR2 JESD79-2E标准;

-

DFI v2.1.1规范。

1.1.4 DMC-400 特性

DMC-400有以下特性:

-

可在 Verilog 中使用的软宏单元;

-

可配置的硬件,支持面积和性能优化;

-

多个ACE-Lite系统接口;

-

多个未完成的交易;

-

系统服务质量(QoS)和请求仲裁,以实现低延迟传输和内存带宽的最佳利用;

-

对交易障碍的保护;

-

ACE-Lite系统接口的可配置位宽;

-

独立的读接受能力和写接受能力

-

AMBA ACE-Lite独占访问传输

-

ACE-Lite和APB接口之间的同步 n:1 时钟连接;

-

多个内存接口(multiple memory interfaces);

-

优化使用外部存储器总线(optimal use of the external memory bus);

-

DRAM省电(DRAM power saving);

-

可编程的外部存储器宽度(programmable external memory width);

-

每个内存接口的可配置的内存芯片选择数量;

-

用于64位和32位SDRAM的内存纠错码(ECC);

-

使用 DFI 2.1.1接口的物理层(PHY)接口。

1.1.5 DMC-400 Interface

The DMC-400 provides the following interfaces:

• APB3 interface

• ACE-Lite interface

• PHY interface

• Clocks and resets

• Debug and profile interface

• Hardware power control interface(s)

推荐阅读:

https://zhuanlan.zhihu.com/p/514892042