1. IP核简介

直接编写DDR2/DDR3的逻辑工作量不太大,但是涉及到双边延、高速率的读取,时序很复杂。因此一般抖采用IP核实现。紫光的SDRAM IP核为HMIC_H IP。

HMIC_H IP 包括了 DDR Controller、DDR PHY 和 PLL,用户通过 AXI4 接口实现数据的读写,通过APB 接口可配置 DDR Controller 内部寄存器.(在初始化阶段,IP 将配置 DDRC 内部的

配置寄存器,如果用户需要读写 DDRC 内部寄存器,需要在初始化完成后进行操作,但一般不建议随意配置)。

在生成IP核时,需要选择IP核在IC的位置。因为 HMIC_H IP是硬核,位置固定不可变动。

2. 程序框架

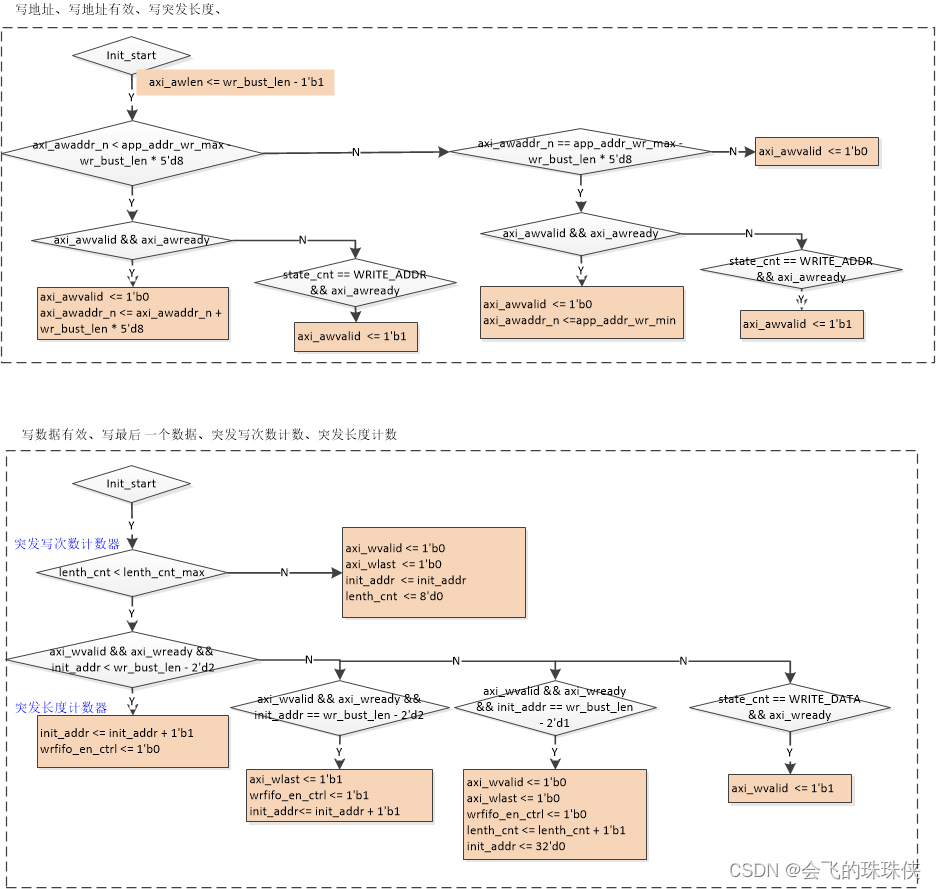

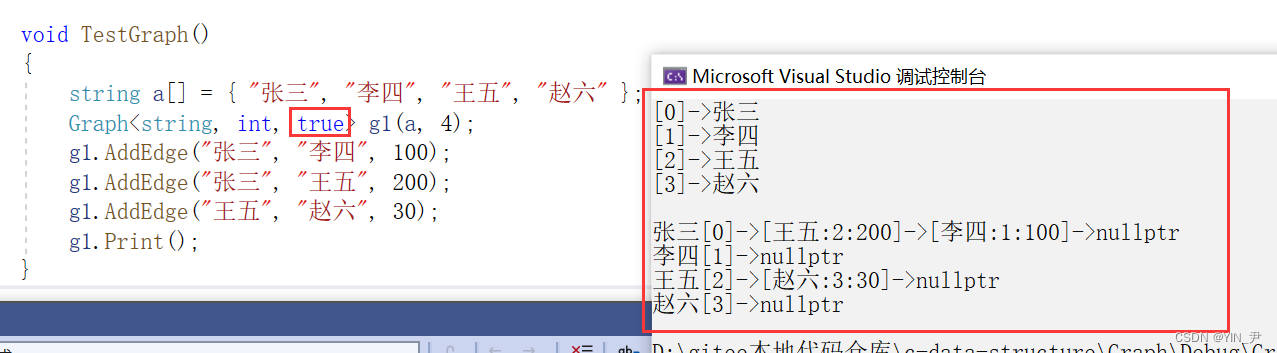

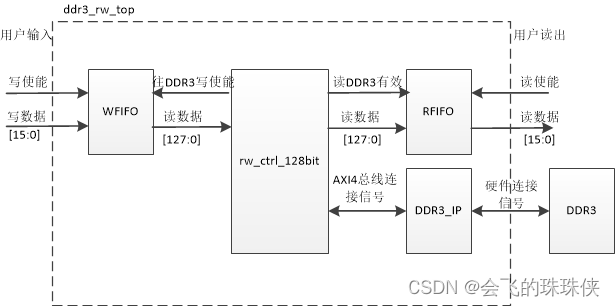

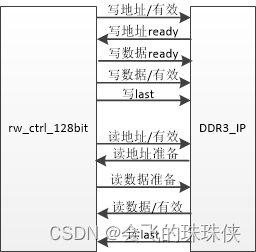

用户输入写使能信号和写数据,传输入WFIFO。然后在写完成后,产生读使能信号。如下图所示,其中DDR3的IP使用的的AXI4标准接口协议。128位和64位可选,本设计是128位数据线传输。rw_ctrl_128bit模块连接FIFO与DDR3_IP,负责产生将FIFO写入和读出的数据转换成AXI4协议传输给DDR3_IP。

关键信号1:从WFIFO读使能/往DDR3写使能:wfifo_rden = axi_wvalid && axi_wready && (~wrfifo_en_ctrl) ;axi_wready是DDR3准备好后发出的,然后rw_ctrl_128bit进行写准备并输出axi_wvalid。当wfifo的wfifo_rcount达到64个(一个128bit,即一共输入512个16bit的数据),就开始往ddr3中写入。

关键信号2:同上,当RFIFO中写入的数据小于64个(128bit),就产生读DDR3使能。

关键信号3:axi_awaddr_n=axi_awaddr_n+wr_bust_len*8。axi_awaddr为写入ddr3的地址,一般一个地址对应一个字节。而_n是程序内部使用的对应16Bit一个字的地址。访问DDR3 IP的地址一次突发长度wr_bust_len变更一次,且一次写入128位(8个字)。

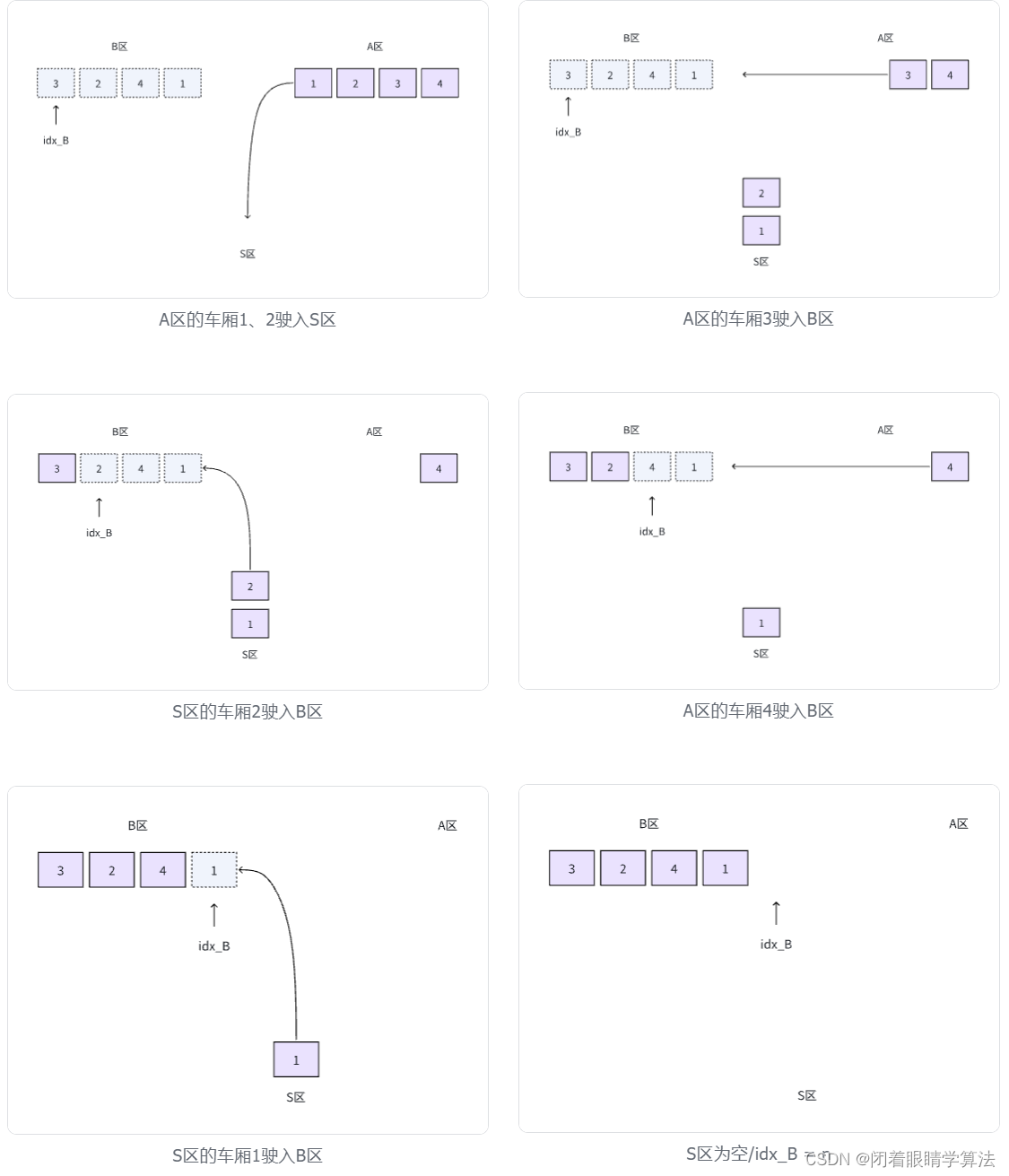

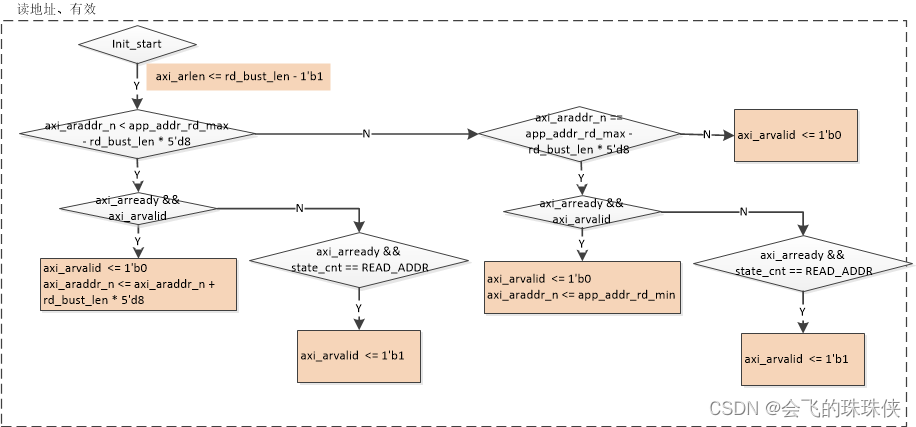

rw_ctrl_128bit访问DDR3的状态过程:

3. 信号时序

读过程:

用户拉高 arvalid信号后等待 arready 拉高,当 arvalid和 arready 信号同时为高时,表示读地址有效,此后在读数据通道上发生数据的传输。

同理用户拉高 rready 信号后等待 rvalid 拉高,当 rready 和 rvalid 信号同时为高时,表示读数据有效。当 rlast拉高时,表示在告诉用户当前为此次读操作的最后一个数据。

写过程:

用户拉高 awvalid信号后等待 awready 信号拉高,当 awvalid 和 awready 信号同时为高时,表示写地址有效。

同理用户拉高 wvalid 信号后等待 wready 信号拉高,当 wvalid 和 wready信号同时为高时,表示写数据有效。当用户拉高 wlast 信号时,表示当前为此次写数据操作的最后一个数据。

当从设备接收完所有的数据时,从设备返回给主设备一个写响应标志本次写操作的结束。