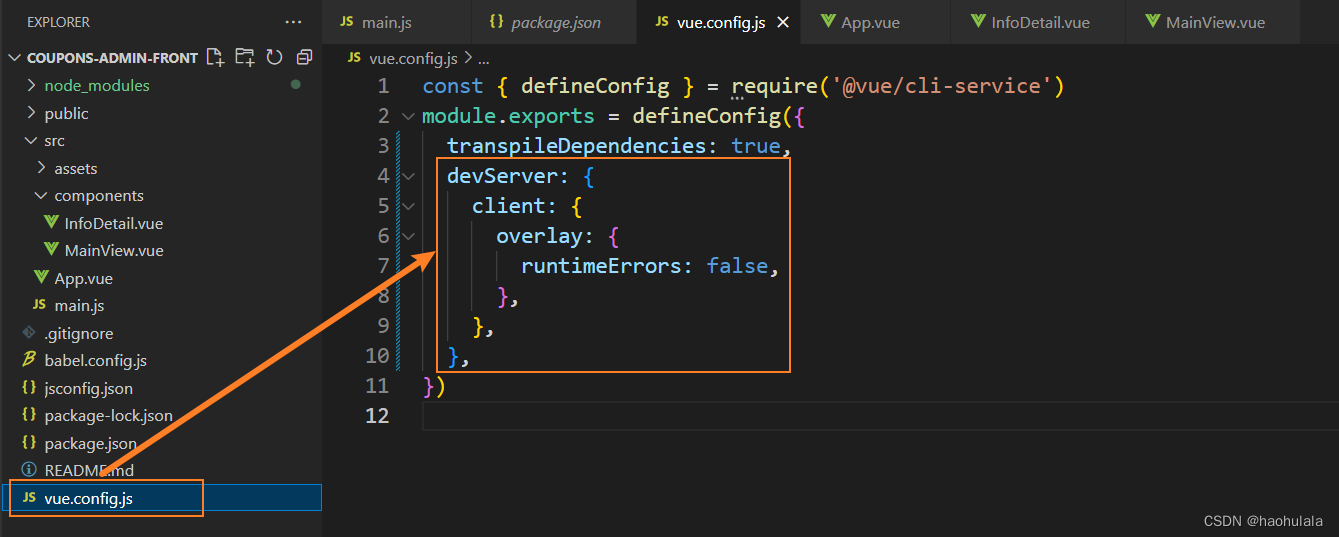

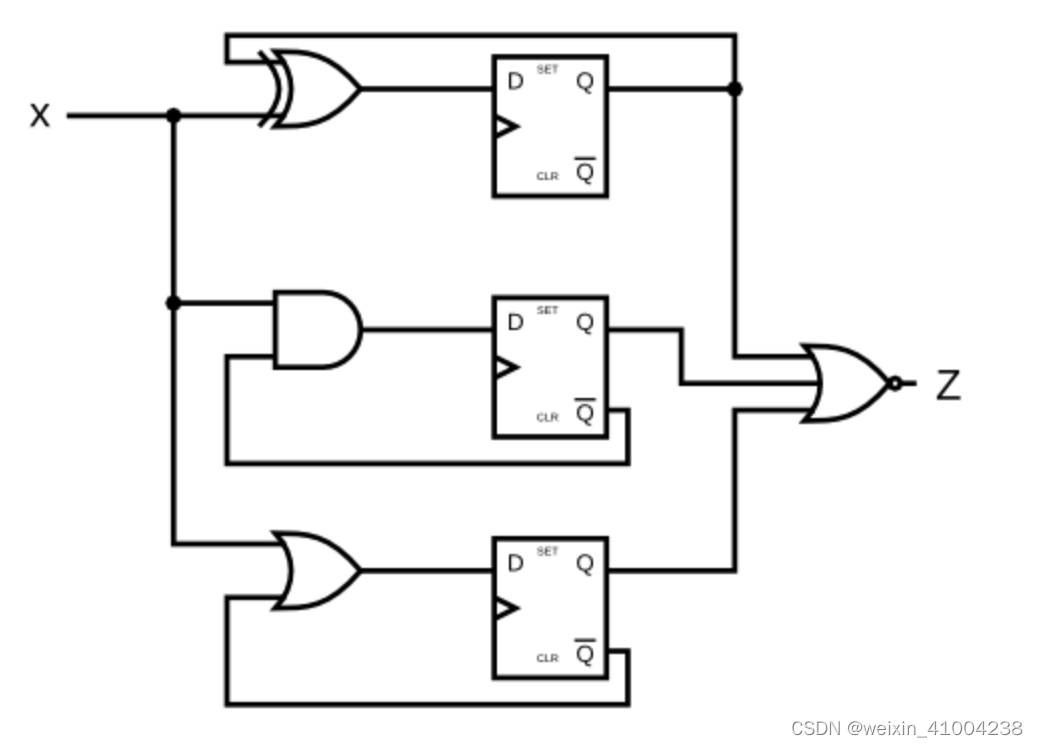

module top_module (

input clk,

input x,

output z

);

reg [2:0] Q;

always@(posedge clk)

begin

Q[0] <= Q[0] ^ x;

Q[1] <= (~Q[1]) & x;

Q[2] <= (~Q[2]) | x;

z <= ~(| Q[2:0]); //错误!!!!

end

endmodule正确答案:

module top_module (

input clk,

input x,

output z

);

reg [2:0] Q;

assign z = ~(| Q[2:0]);

always@(posedge clk)

begin

Q[0] <= Q[0] ^ x;

Q[1] <= (~Q[1]) & x;

Q[2] <= (~Q[2]) | x;

end

endmodule