文章目录

- 前言

- 一、步骤 1:用 M-Code 建模控制

- 1、引言

- 2、目标

- 3、步骤

- 二、步骤 2:用 HDL 建模模块

- 1、引言

- 2、目标

- 3、步骤

- 三、用 C/C++ 代码建模块

- 1、引言

- 2、目标

- 3、步骤

- 4、第 1 部分:从 Vivado HLS 创建一个系统生成器包

- 5、第 2 部分:在 System Generator 设计中包含一个 Vivado HLS 包

- 总结

前言

本节讲解如何讲讲代码(Matlab、HDL、C/C++)导入到 System Generator 并使用。

一、步骤 1:用 M-Code 建模控制

1、引言

在这一步中,你将使用 MCode 块创建一个简单的有限状态机(FSM)来检测二进制值 1011 的序列。FSM 也需要能够检测到多个传输,例如 10111011

2、目标

完成本实验后,你将能够使用 System Generator 中的 MCode 块创建有限状态机。

3、步骤

在本练习中,你将使用 M-code 为有限状态机创建控制逻辑。然后,你将模拟最终设计以确认正确的操作

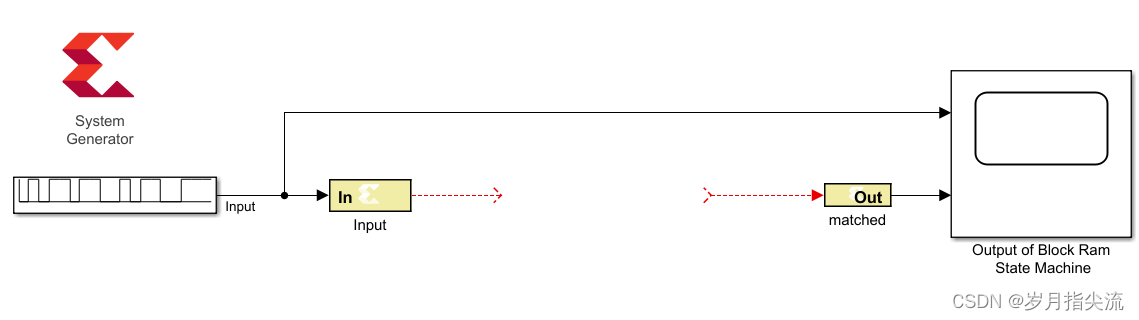

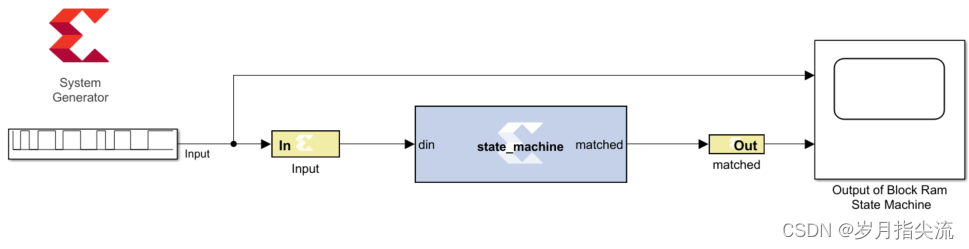

①、启动 System Generator 并打开 Simulink 将 Lab2\M_code\Lab2_1.slx 打开,您可以看到下面这个不完整的图表

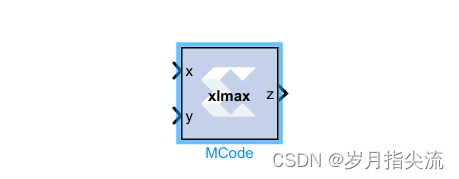

②、从 Xilinx Blockset/Index 库中添加一个 MCode 块。

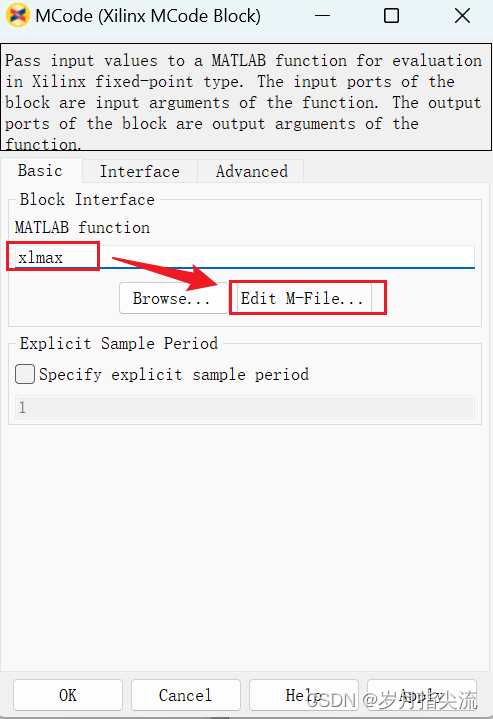

③、双击 MCode 块,单击 “编辑m文件”,如下图所示

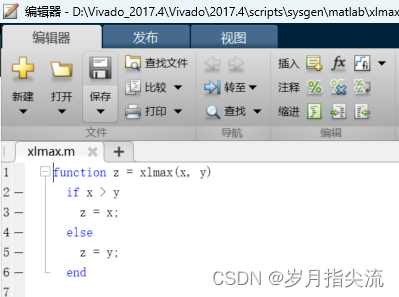

下图显示了 MATLAB 文本编辑器中的默认 m 代码

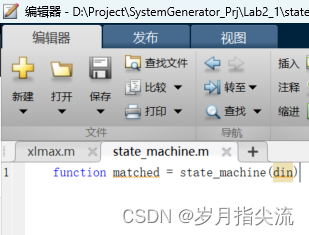

⑤、新建 state_machine.m 文件,使其包含函数名 state_machine 以及匹配的输入和输出。

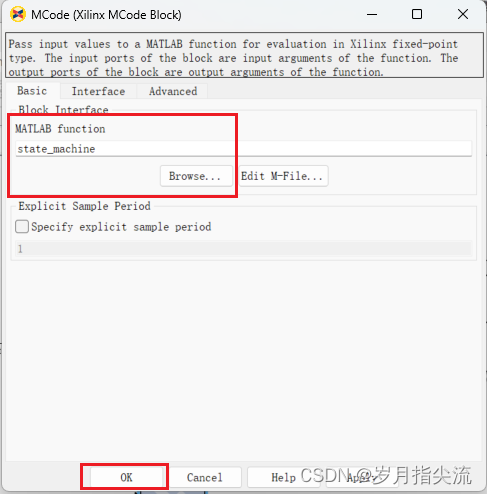

⑥、编辑完成后,使用另存为将 MATLAB 文件保存为 state_machine.m 到 Lab2_1 文件夹。在 MCode 属性编辑器中,使用 Browse 按钮确保 MCode 块引用了本地的 M-code 文件(state_machine.m)。

⑦、在 MCode 属性编辑器中,单击 OK。您将看到 MCode 块使用了新的端口和函数名,现在将 MCode 块连接到下图中:

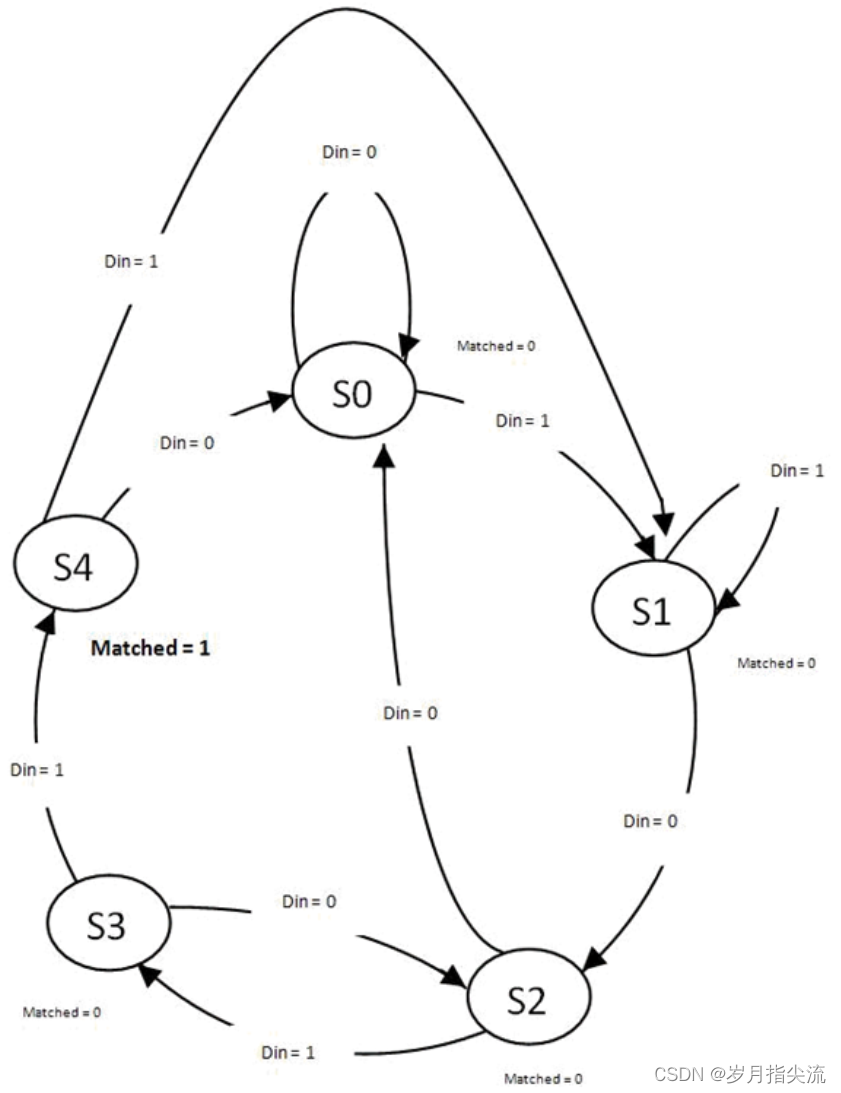

现在可以开始对状态机进行编码了。这个状态机的气泡图如下图所示。该 FSM 具有五种状态,能够连续检测两个序列

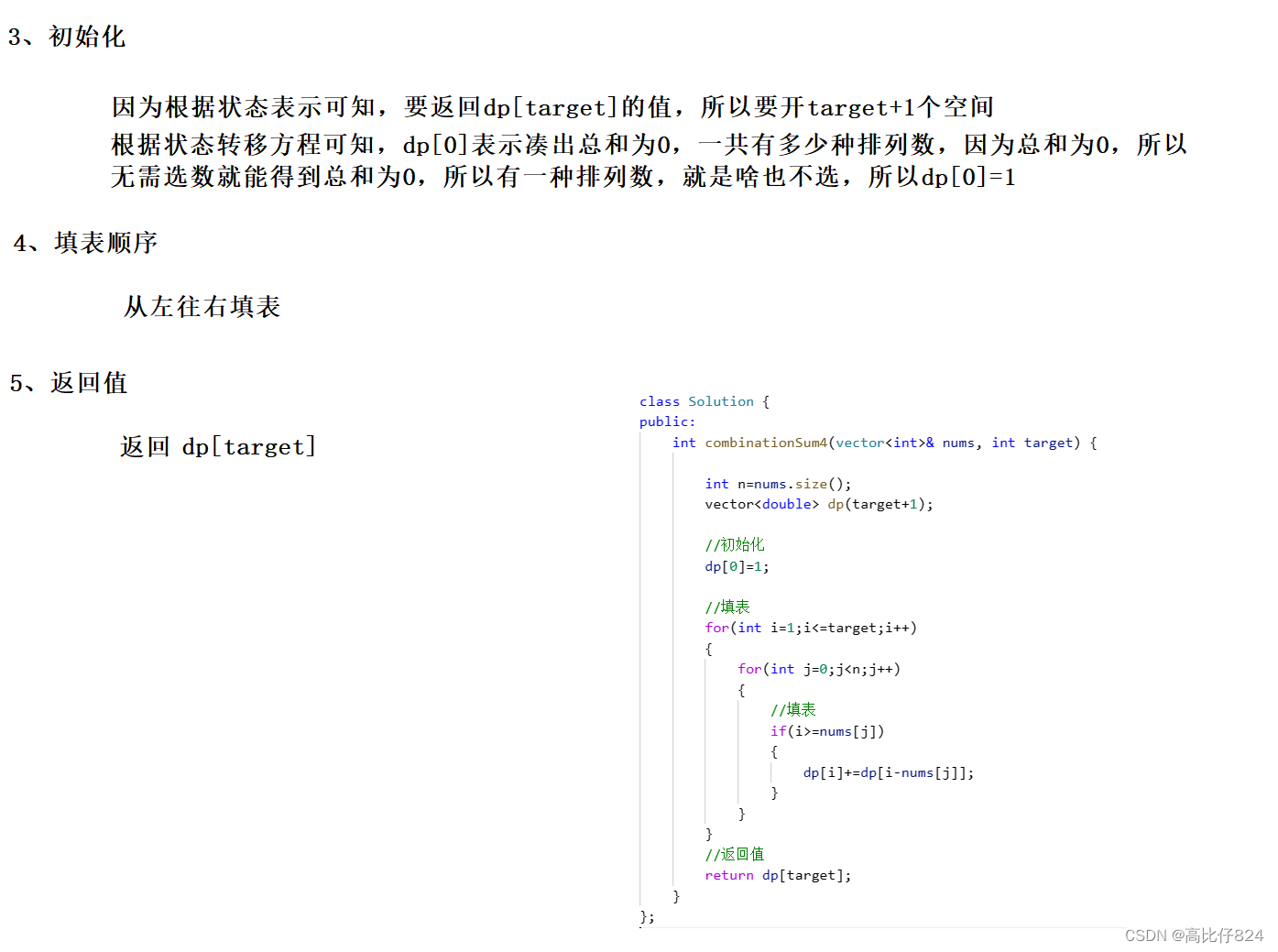

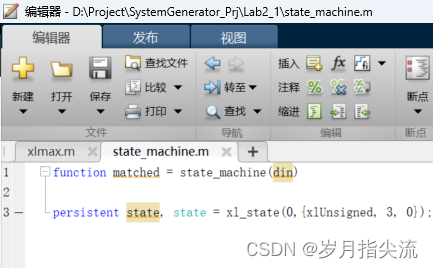

⑧、编辑 M-code 文件 state_machine。使用 Xilinx xl_state 数据类型定义状态变量,如下所示。这要求你将变量声明为持久变量。xl_state 函数需要两个参数:初始条件和一个定点声明。因为你需要数到 4,你需要 3 位

persistent state, state = xl_state(0,{xlUnsigned, 3, 0});

这部分的代码使用 persistent 将 state 在该 M 文件中做了一个变量的声明,可以在该 M 文件中进行使用,xl_state()这个则是对state进行赋值;

该函数的简单用法就是:xl_state(init, precision)

第一个 init 就是初始化的值,precision 就是其精度;

而代码中的{xlUnsigned, 3, 0}属于一个单元阵列,其中 xlUnsigned 代表数据类型是无符号的定点数;3代表数据的位宽,因为代码中的 state 需要达到4,所以至少要 3bit 的位宽;0 代表的是二进制点的位置,该部分代码不需要有小数,所以直接设置为 0。xl_state 以及 Percision 也都还有其他用法,可以自行对 MCode 使用 help 进行研究。

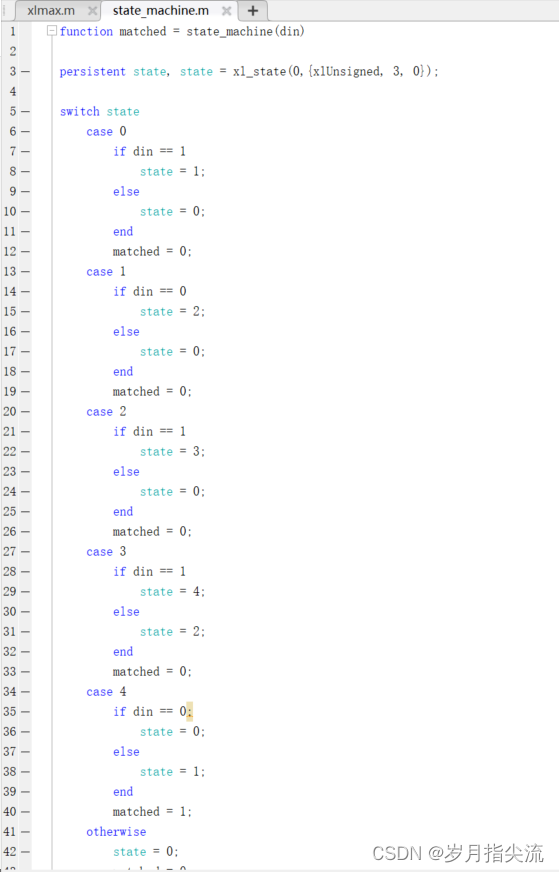

⑨、使用 switch-case 语句定义所显示的 FSM 状态。下面提供了一个小示例来帮助您入门

注意:你需要一个 otherwise 语句作为最后一个 case

switch state

case 0

if din == 1

state = 1;

else

state = 0;

end

matched = 0;

case 1

if din == 0

state = 2;

else

state = 0;

end

matched = 0;

case 2

if din == 1

state = 3;

else

state = 0;

end

matched = 0;

case 3

if din == 1

state = 4;

else

state = 2;

end

matched = 0;

case 4

if din == 0;

state = 0;

else

state = 1;

end

matched = 1;

otherwise

state = 0;

matched = 0;

end

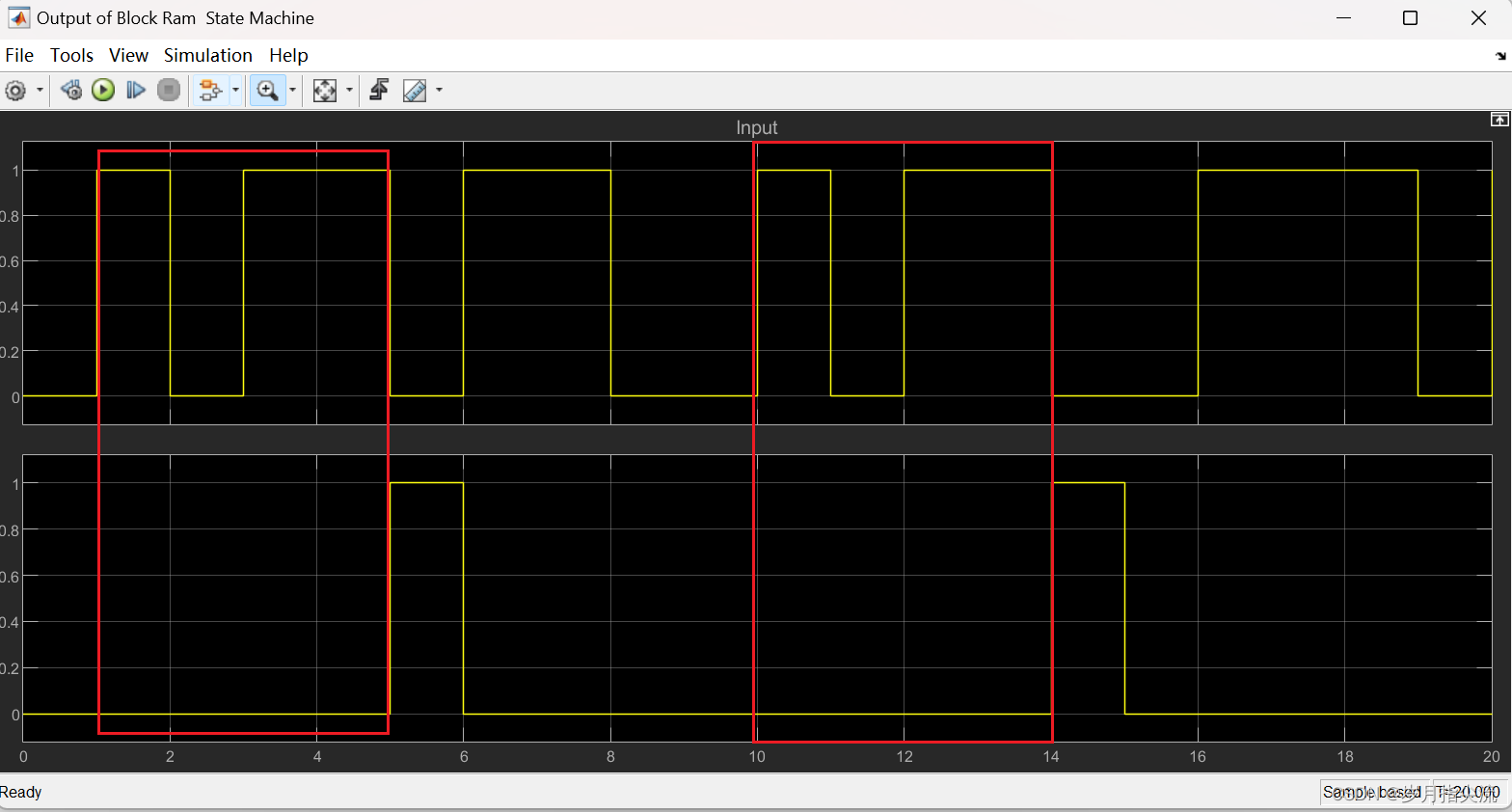

⑩、保存 M-code 文件并运行仿真。波形应该如下图所示。

可以看到只要出现了 “1011” 的序列,输出检测就会置 1,反之保持为 0。

二、步骤 2:用 HDL 建模模块

1、引言

在本实验练习中,您将把 RTL 设计作为黑盒导入 System Generator。黑盒子允许将设计导入 System Generator,即使描述是硬件描述语言(HDL)格式

2、目标

完成此步骤后,你将能够:

- 将 RTL HDL 描述导入到 DSP 的 System Generator 中

- 配置黑盒以确保设计能够成功模拟

3、步骤

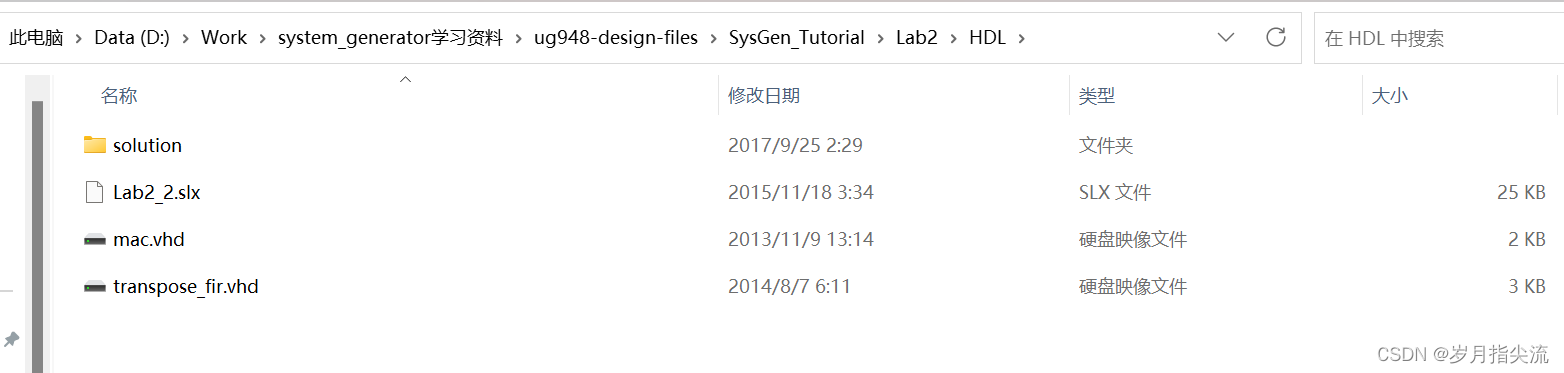

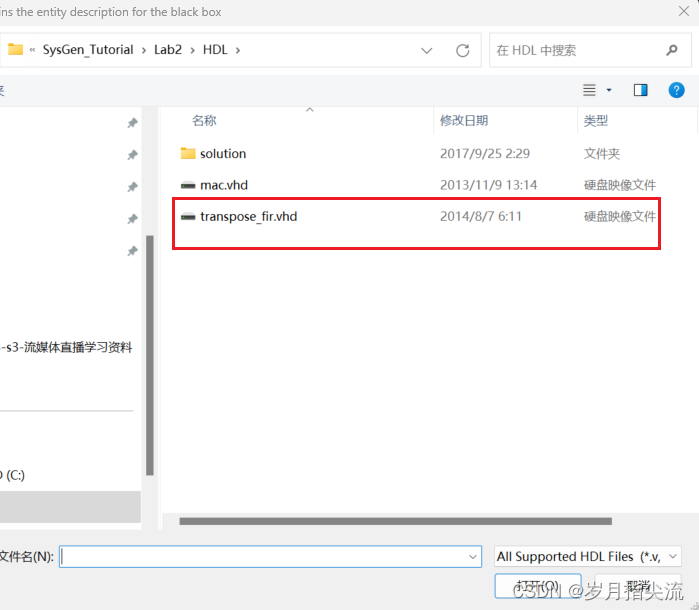

①、我们将用到下面目录中的文件 D:\Work\system_generator学习资料\ug948-design-files\SysGen_Tutorial\Lab2\HDL

以下文件位于此目录中:

- Lab2_2.slx:一个包含黑盒示例的 Simulink 模型

- transpose_fir.vhd。顶级 VHDL 的转置形式的 FIR 滤波器。该文件是与黑盒相关联的 VHDL

- mac.vhd:用于构建转置 FIR 滤波器的乘法和加法器组件。

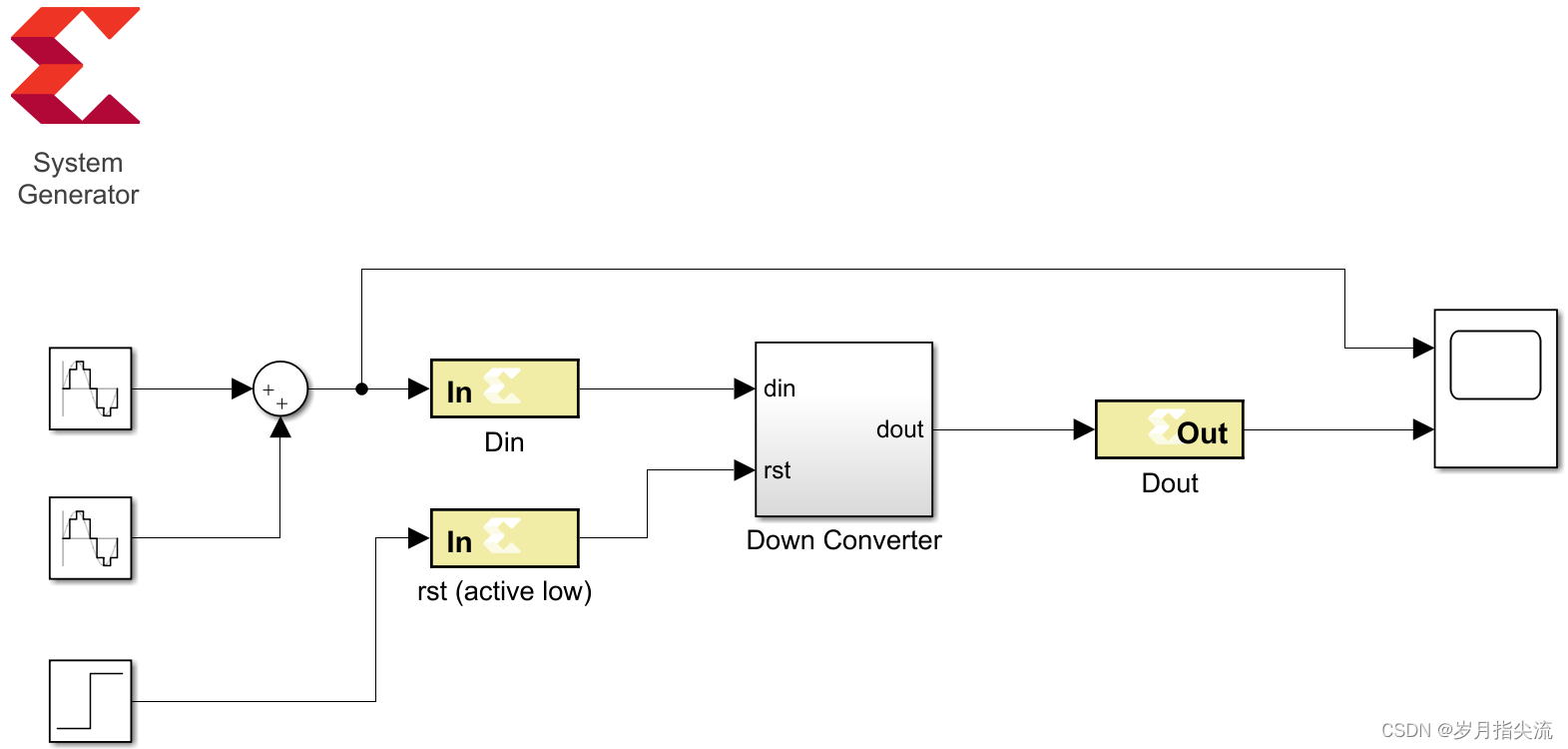

②、启动 System Generator 并打开 Simulink 将 Lab2\M_code\Lab2_2.slx 打开

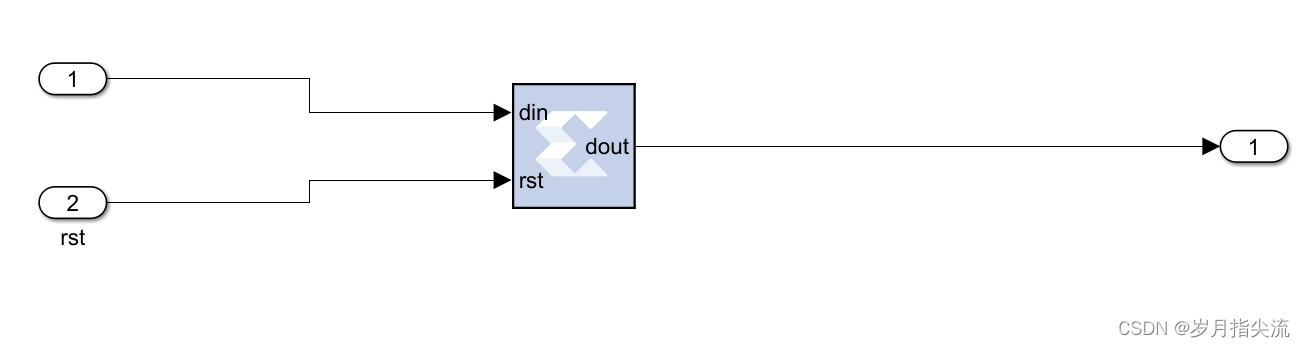

②、打开名为 Down Converter(下变频器)的子系统,打开名为 Transpose FIR Filter Black Box 的子系统。此时,子系统包含两个输入端口和一个输出端口。你将向这个子系统添加一个黑盒。此时,子系统包含两个输入端口和一个输出端口。你将在这个子系统中添加一个黑盒:

③、右键单击设计画布,选择 Xilinx BlockAdd,并向该子系统添加一个 Black Box 块。打开一个浏览器窗口,列出可以与黑盒关联的 VHDL 源文件。从这个窗口中,选择顶级 VHDL 文件 transpse_fir.vhd。如下图所示:

关联的配置 M-code 为 transpose_fir_config 在编辑器中打开以进行修改

④、关闭编辑器,将黑匣子的端口连接到相应的子系统端口并保存设计

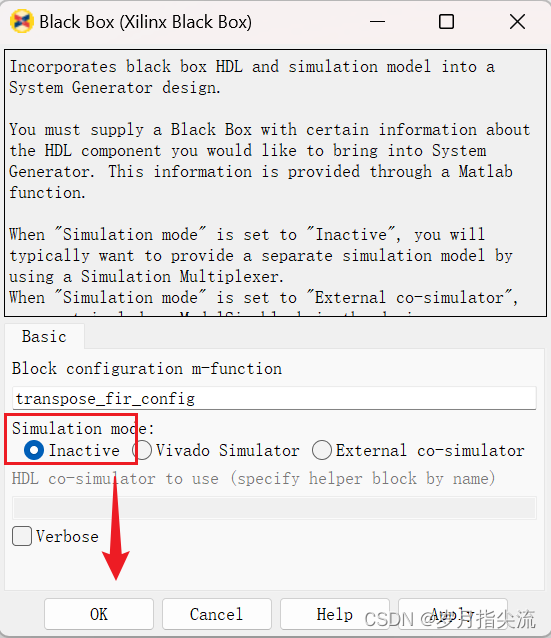

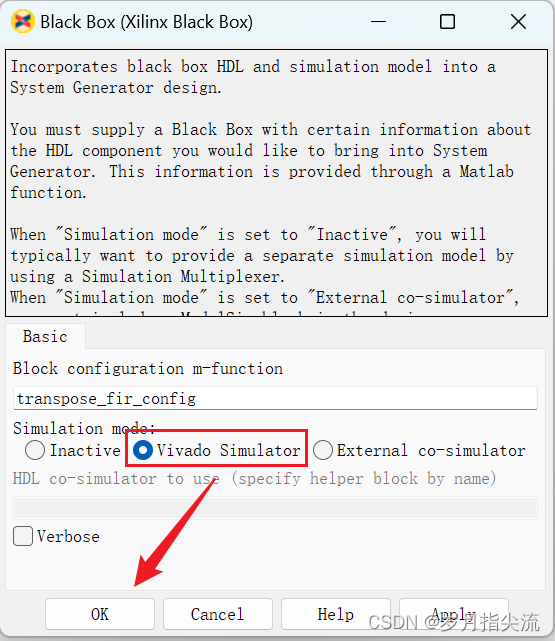

⑤、双击 Black Box 以打开此对话框

以下是对话框中的字段:

- Block configuration m-function:这为黑匣子指定配置 m 函数的名称。在本例中,该字段包含由 Configuration Wizard 生成的函数的名称。默认情况下,黑盒使用向导生成的函数。但是,你可以替换你自己创建的一个。

- Simulation mode:有三种模拟模式

- Inactive: 当模式为 Inactive 时,黑盒通过忽略其输入并产生零来参与模拟。此设置通常用于当一个单独的仿真模型可用于黑盒,并且该模型使用仿真多路复用器与黑盒并行连接时。

- Vivado Simulator:当模式为 Vivado Simulator 时,对与黑盒相关的 HDL 进行联合仿真,生成黑盒的仿真结果

- External co-simulator:当模式为外部协同模拟器时,需要在设计中添加 ModelSim HDL 协同仿真模块,并在 HDL 协同模拟器使用字段中指定 ModelSim 模块的名称。在该模式下,使用 HDL 协同仿真对黑盒进行仿真。

将模拟模式设置为 Inactive(非活动),然后单击“确定”关闭对话框

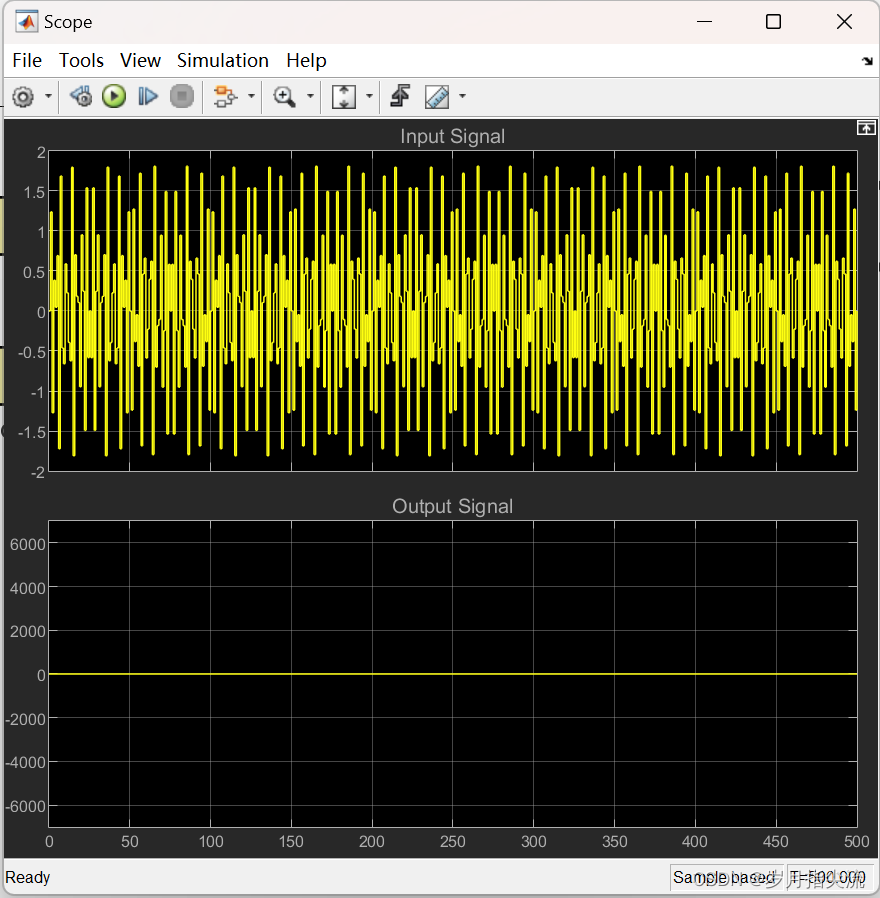

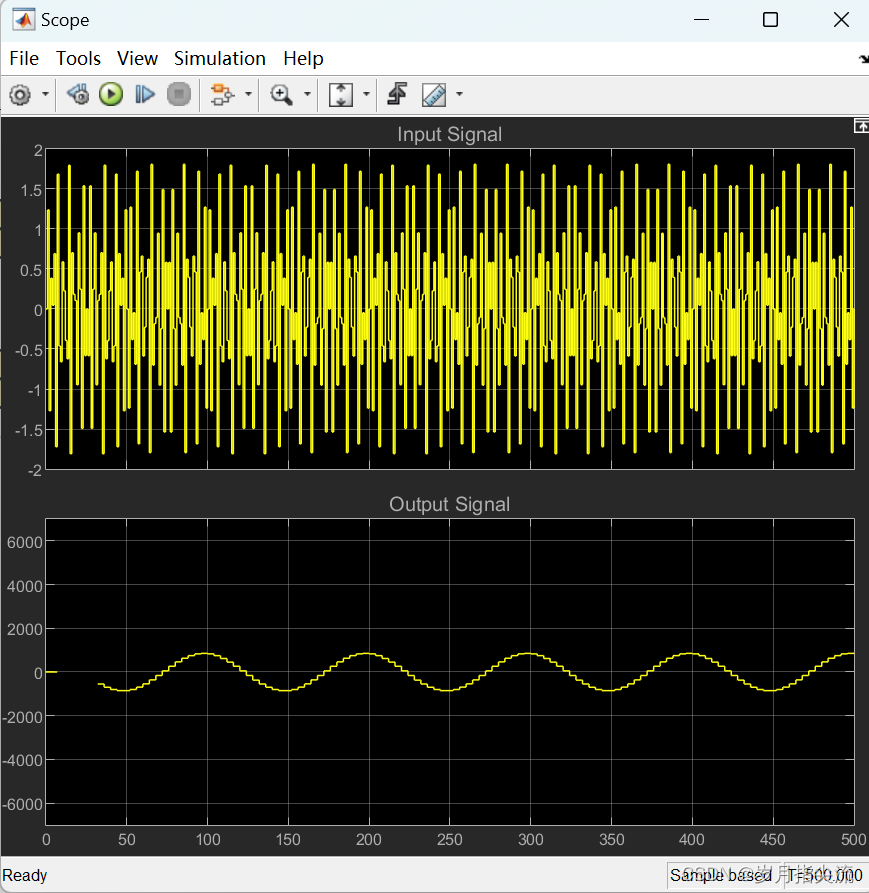

⑥、移动到设计的顶层,点击 run simulation 按钮运行仿真;然后双击 Scope 块。

注意,output Signal 作用域中显示的黑箱输出为零。这是预期的,因为黑盒在模拟期间被配置为 Inactive

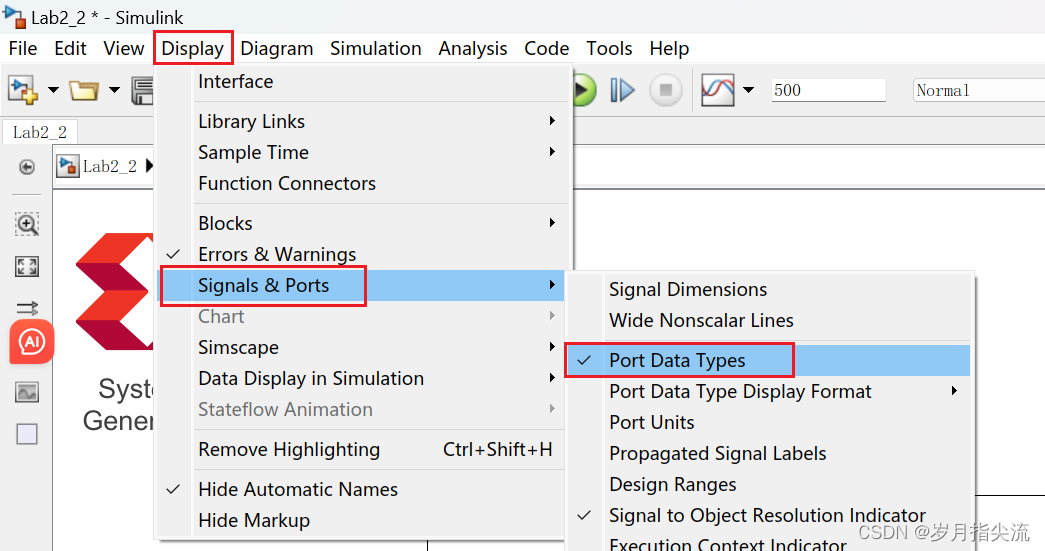

⑦、从 Simulink 编辑器菜单中,选择 Display > Signals & Ports > Port Data Types 显示黑匣子的端口类型

⑧、编译模型(Ctrl-D)以确保端口数据类型是最新的。注意,黑匣子端口输出类型是 UFix_26_0。这意味着它是无符号的,26 位宽,并且在最低有效位的左边有一个二进制点 0

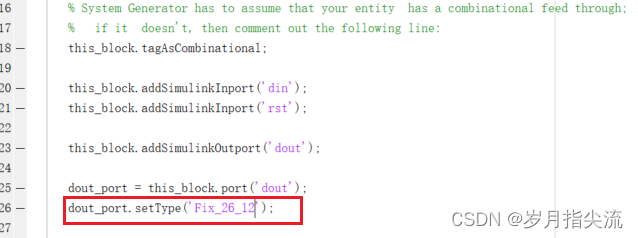

⑨、打开配置 M-function transpose_fir_config。将输出类型从 “UFix_26_0” 修改为 “Fix_26_12”。修改后的行(第 26 行)应该是这样的

dout_port.setType('Fix_26_12');

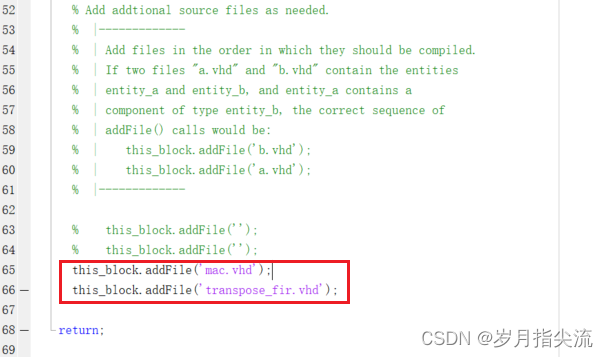

继续执行以下步骤,编辑配置 m-函数,将另一个 HDL 文件与黑盒关联起来,定位第 65 行:

this_block.addFile('transpose_fir.vhd');

在这行代码的上方,添加以下代码:

this_block.addFile('mac.vhd');

保存对配置 m-函数 的更改并关闭该文件

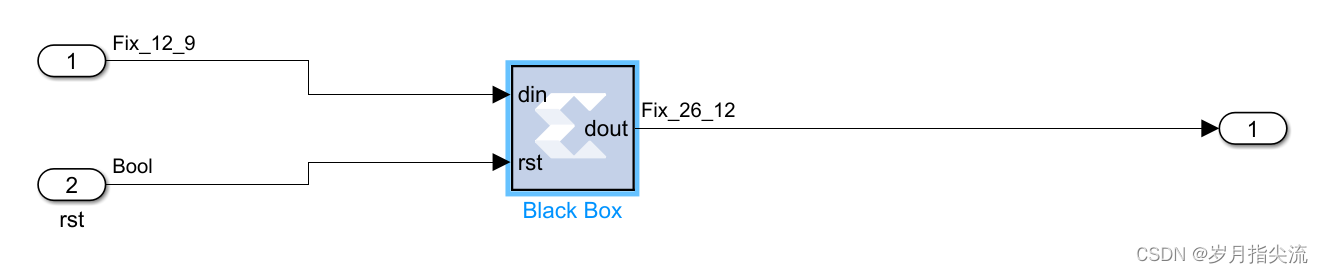

⑩、单击设计画布并重新编译模型(Ctrl-D),你的转置 FIR 滤波器黑盒子系统应显示如下:

在 “黑匣子” 块参数对话框中,将 “模拟模式” 字段从 “非活动” 更改为 “Vivado 模拟器”,然后单击 “确定”

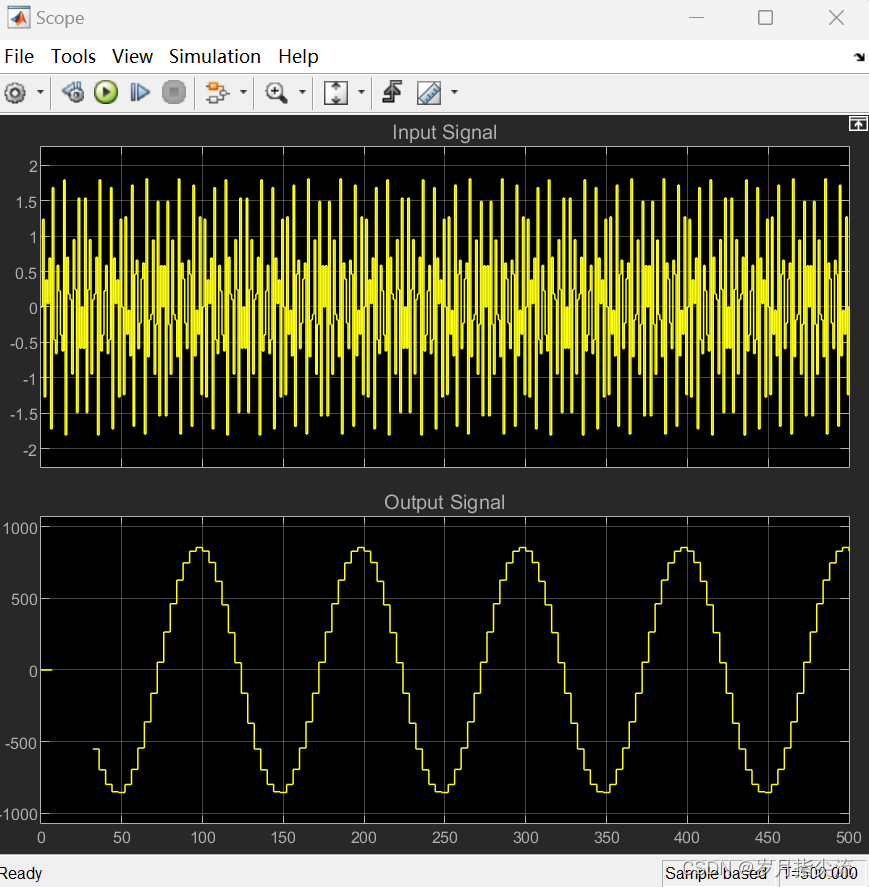

⑪、移到设计的顶层并运行模拟,在模拟完成后检查范围输出。注意波形不再为零。当模拟模式为非活动时,输出信号范围显示恒定零。现在,输出信号显示一个正弦波作为 Vivado 模拟的结果。

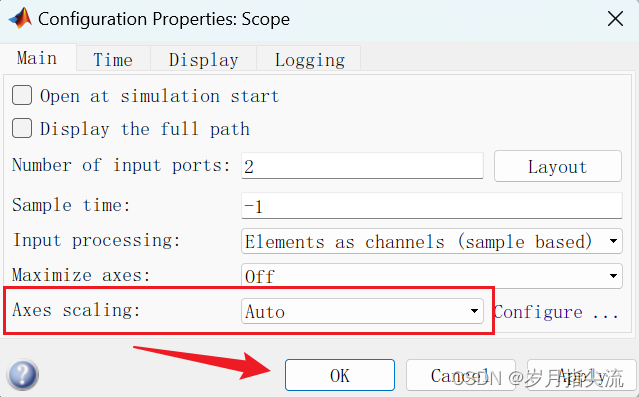

右键单击 Output Signal 显示并选择 Configuration Properties。在 Main 选项卡中,将轴缩放设置为自动设置。

你应该看到类似于下面所示的显示

三、用 C/C++ 代码建模块

1、引言

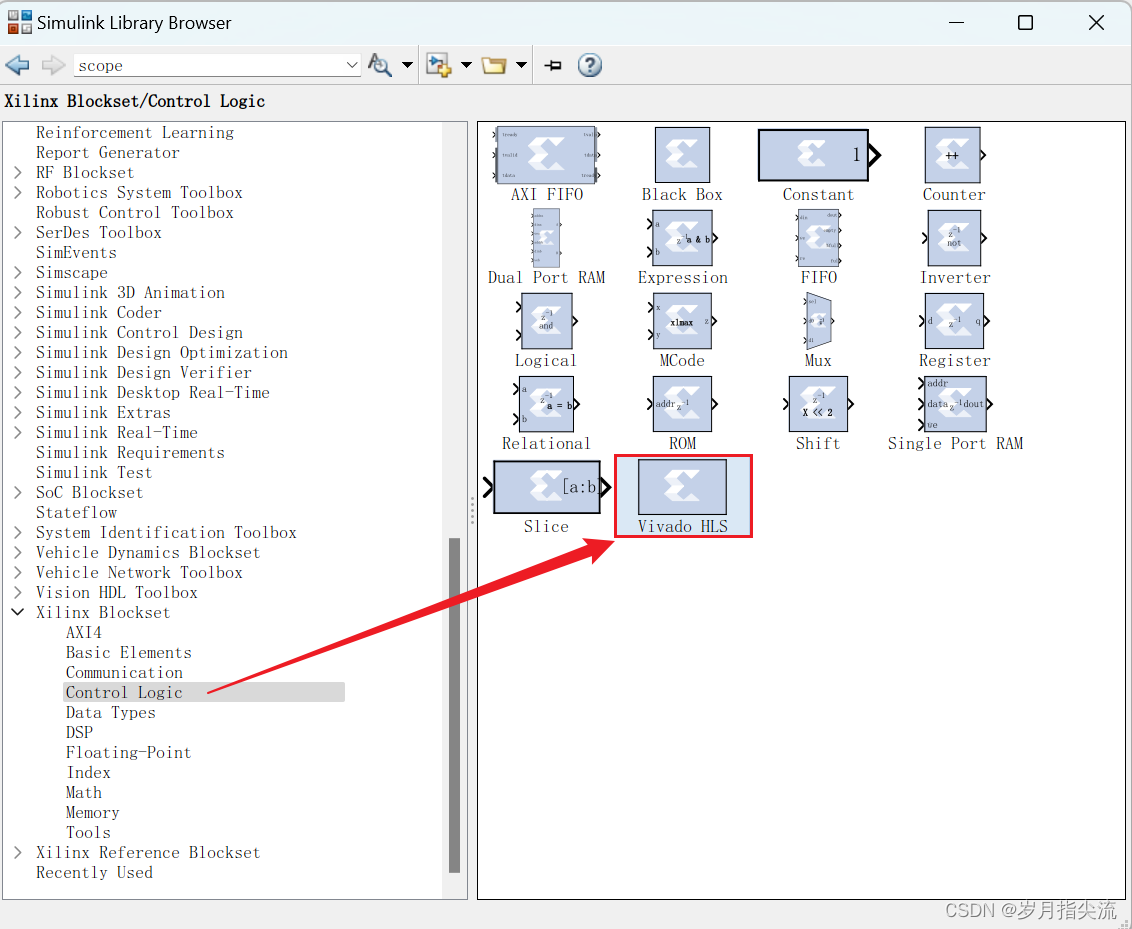

Vivado 设计环境的系统版包括 Vivado HLS 功能,它具有将 C/C++ 设计源转换为 RTL 的能力。System Generator 在 Xilinx Blockset/Control Logic 和 Xilinx Blockset/Index 库中有一个 Vivado HLS 块,使你能够将 C/C++ 源文件引入到 System Generator模型中。

2、目标

完成本实验后,您将能够使用 Vivado HLS 将 C,C++ 或 SystemC 合成的设计作为块合并到你的 MATLAB 设计中

3、步骤

在这一步中,将首先使用 Vivado HLS 合成一个 C 文件。你将在 Vivado DSP 设计项目中操作,使用 MATLAB 中的设计文件以及相关的 HDL 包装器和约束文件。在第 2 部分中,你将把 Vivado HLS 的输出合并到 MATLAB 中,并使用 MATLAB 丰富的仿真功能来验证 C 算法是否正确地过滤了图像。

4、第 1 部分:从 Vivado HLS 创建一个系统生成器包

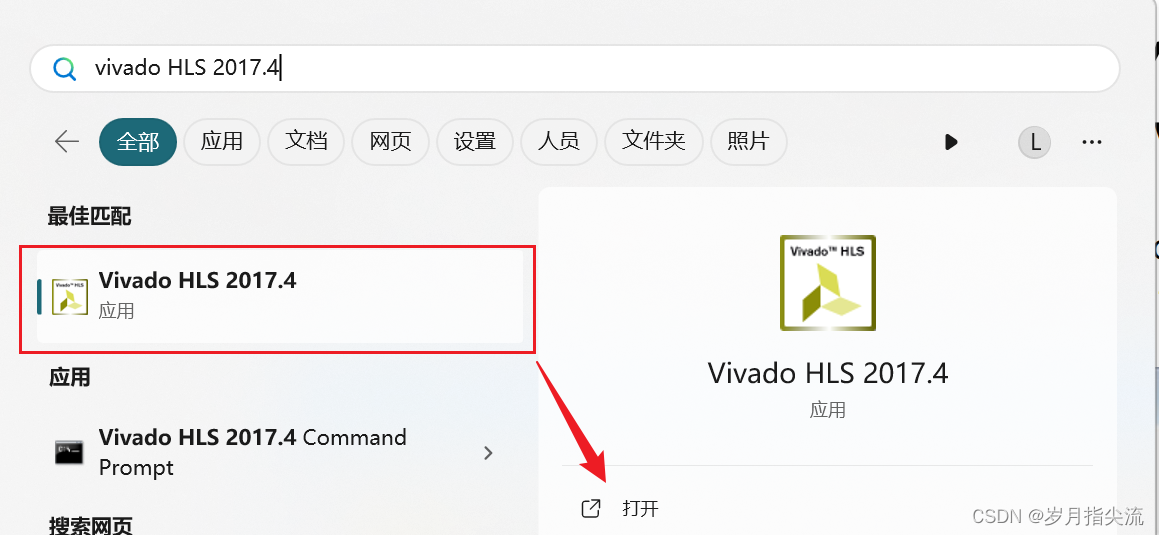

①、打开 Vivado HLS 2017.4

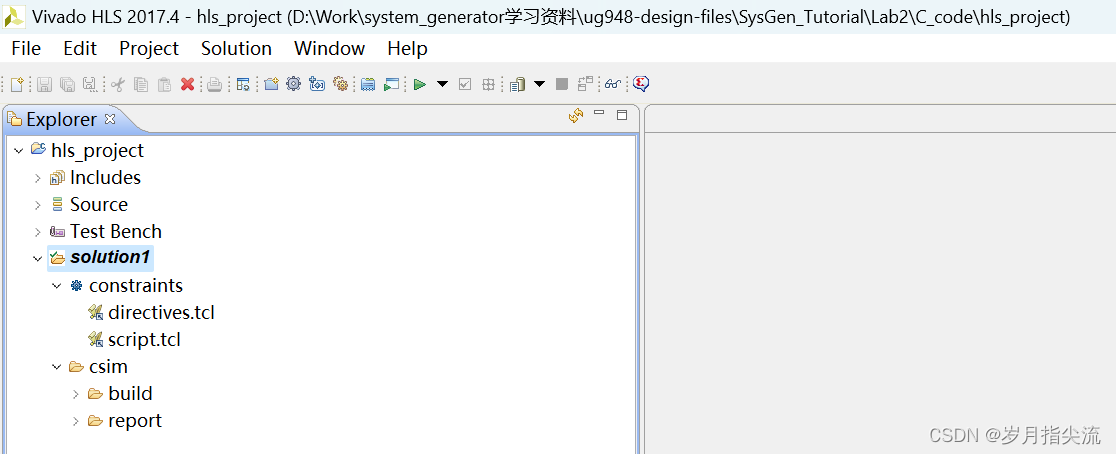

②、在欢迎界面中选择 Open Project,然后导航到 Vivado HLS 项目目录 D:\Work\system_generator学习资料\ug948-design-files\SysGen_Tutorial\Lab2\C_code\hls_project,如下图所示

③、展开 Explorer 窗格中的 Source 文件夹(左侧)并双击文件 MedianFilter.cpp,以查看 C++ 文件的内容,如下图所示

这个文件在 3x3 窗口大小上实现了一个二维中值过滤器

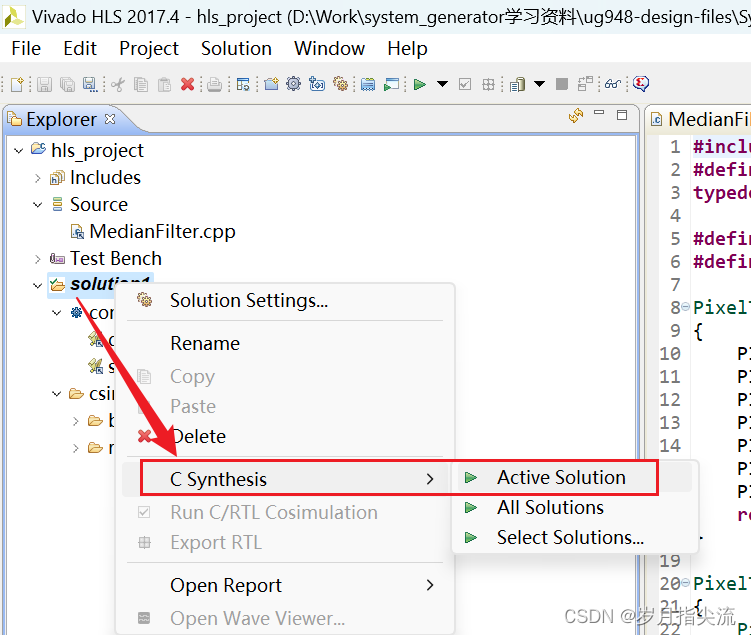

④、通过右键单击 solution1 并选择 C Synthesis > Active Solution,如下图所示

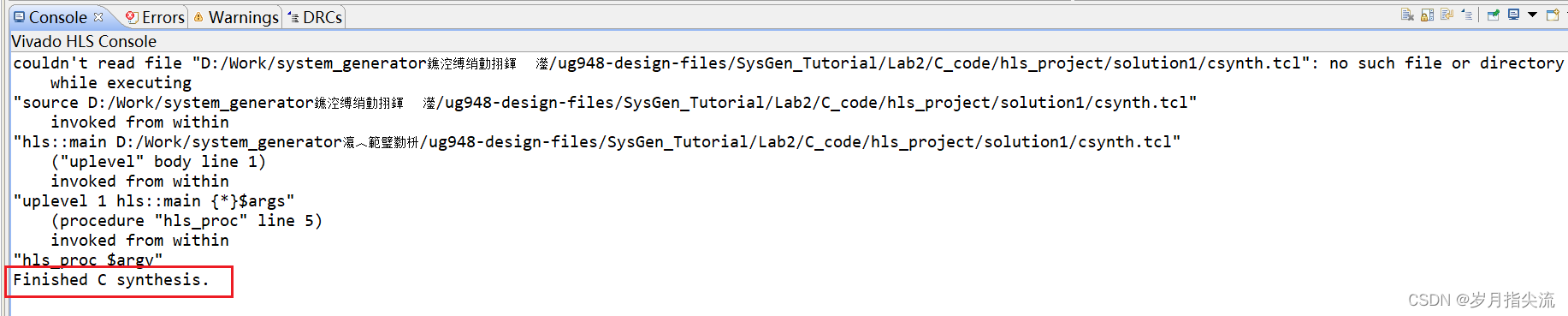

当合成完成时,Vivado HLS 显示这个消息:完成 C 合成。现在将源代码打包,以便在 System Generator 中使用

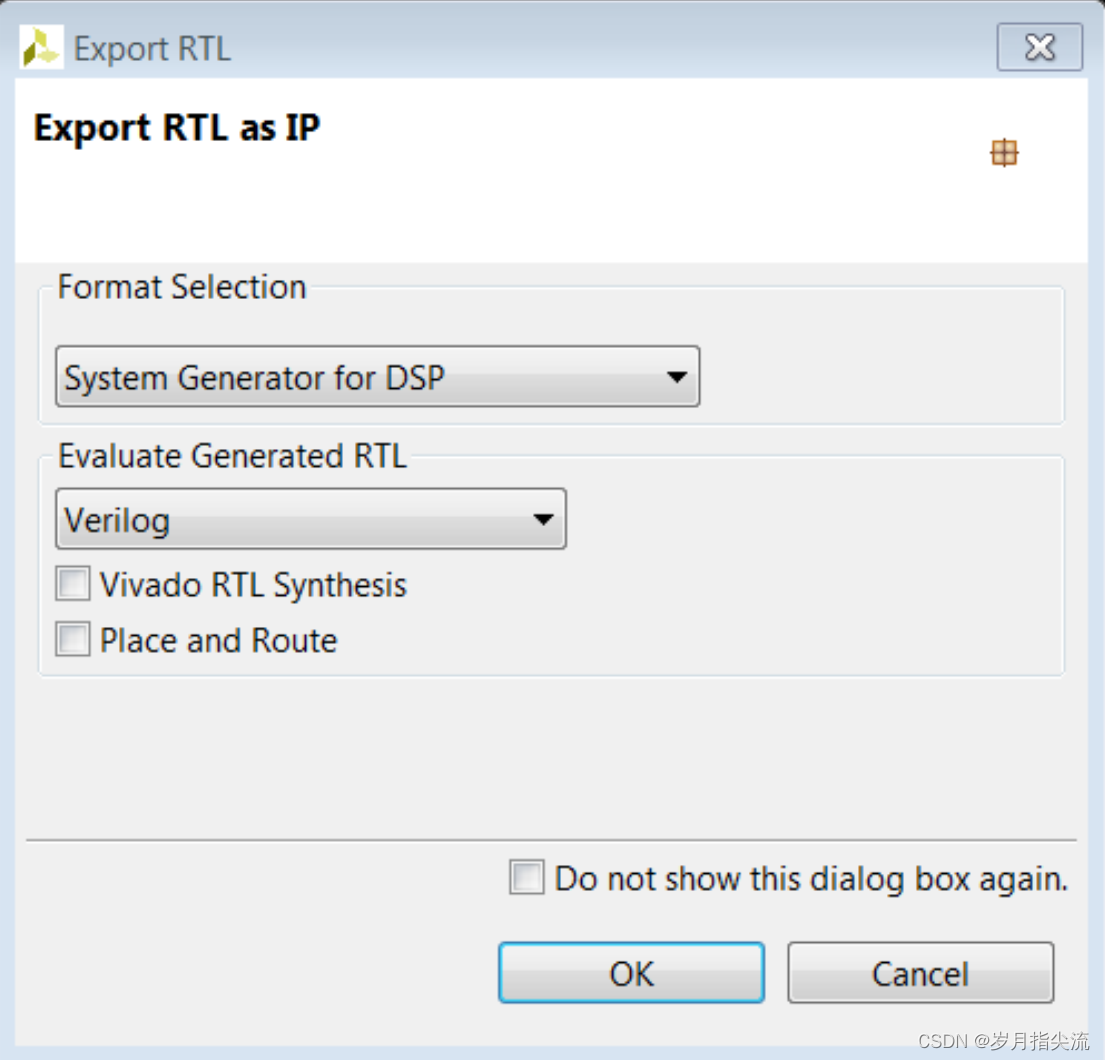

⑤、右键单击 solution1 并选择 Export RTL,如下图所示,选择 “Format Selection” 为 “System Generator for DSP”,单击 “OK”

当导出 RTL 过程完成时,Vivado HLS 显示此消息:Finished export RTL.

5、第 2 部分:在 System Generator 设计中包含一个 Vivado HLS 包

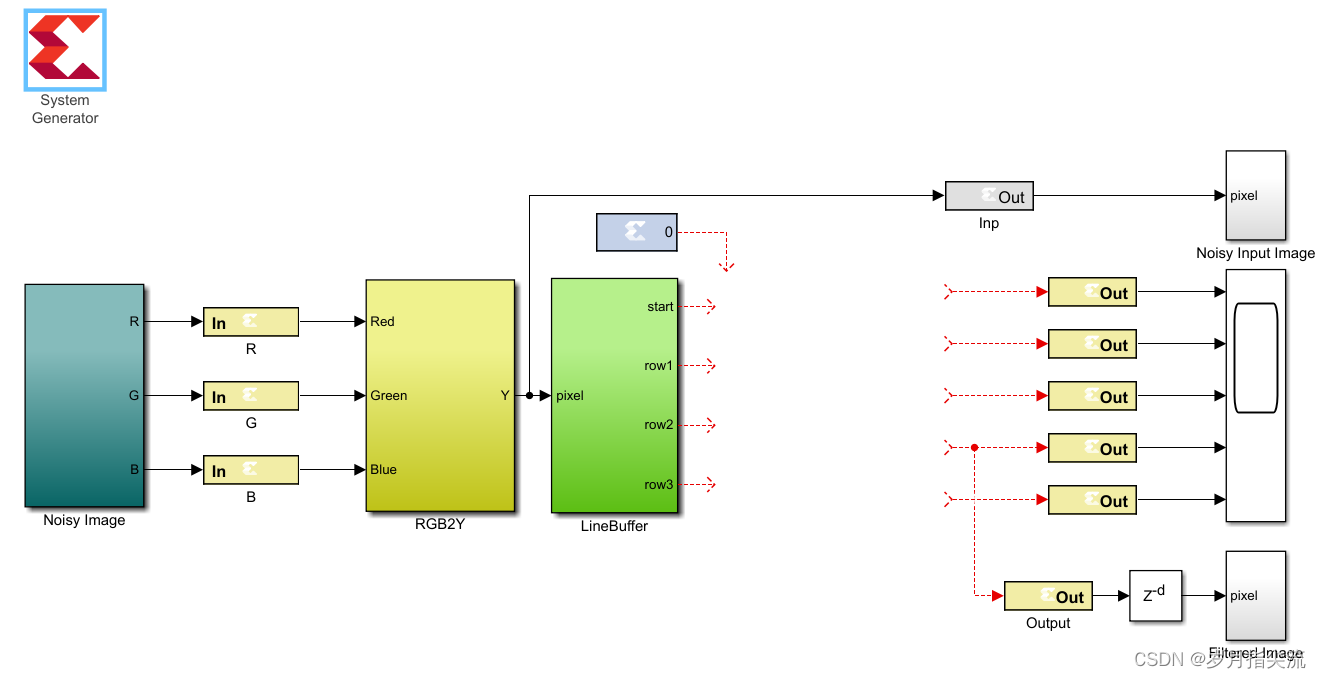

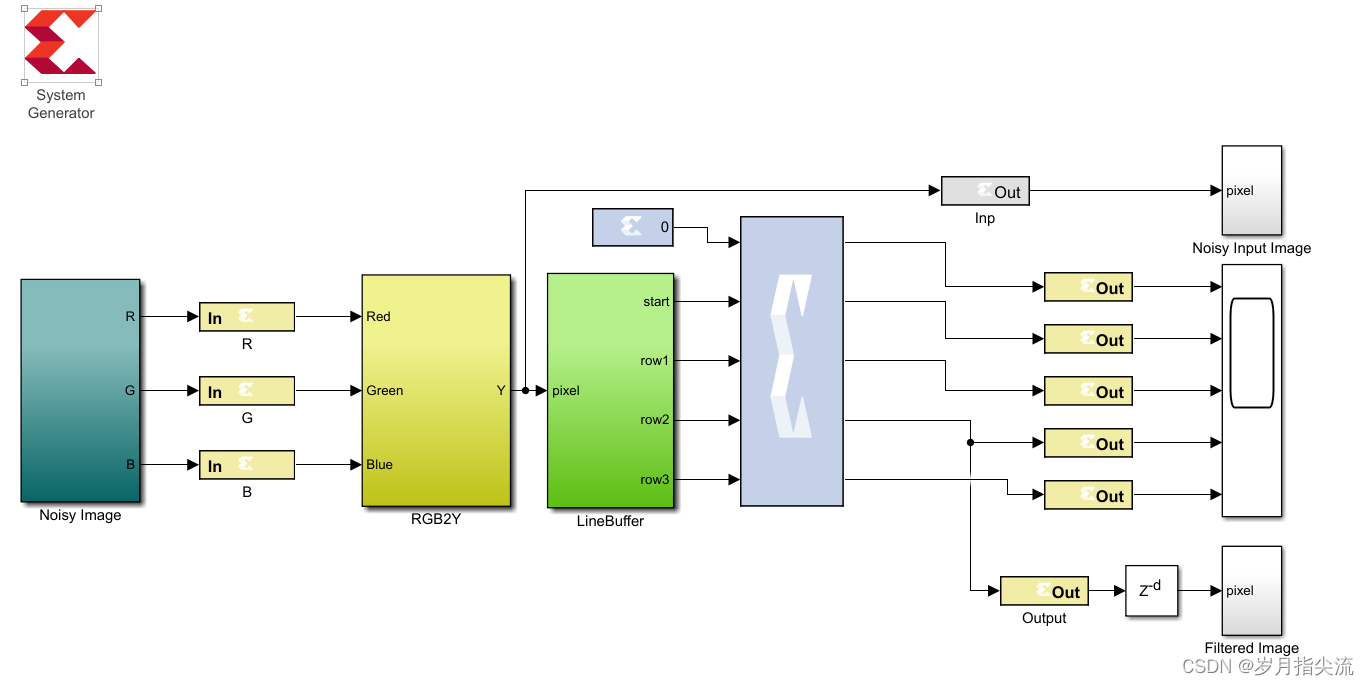

①、启动 System Generator,打开 Lab2_3。Lab2/C_code 文件夹下的 Lab2_3.slx 文件。这将打开模型,如下图所示:

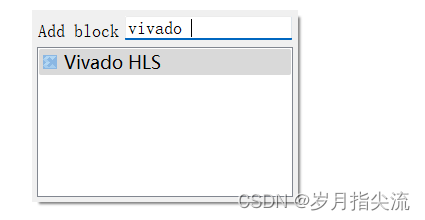

②、通过右键单击画布工作区上的任何位置来添加一个 Vivado HLS 块

- 选择 Xilinx BlockAdd

- 在 “添加块” 对话框中输入 Vivado HLS

- 选择 Vivado HLS,如下图所示

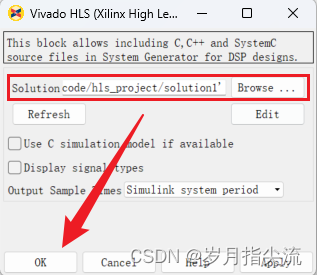

③、双击 Vivado HLS 块打开属性编辑器,使用 Browse 按钮选择 Vivado HLS 在第 1 部分 中创建的解决方案,位于D:\Work\system_generator学习资料\ug948-design-files\SysGen_Tutorial\Lab2\C_code\hls_project\solution1,如图所示:导入 Vivado HLS IP,单击 “确定”,导入 Vivado HLS IP

④、连接模块的输入输出端口,如下图所示:

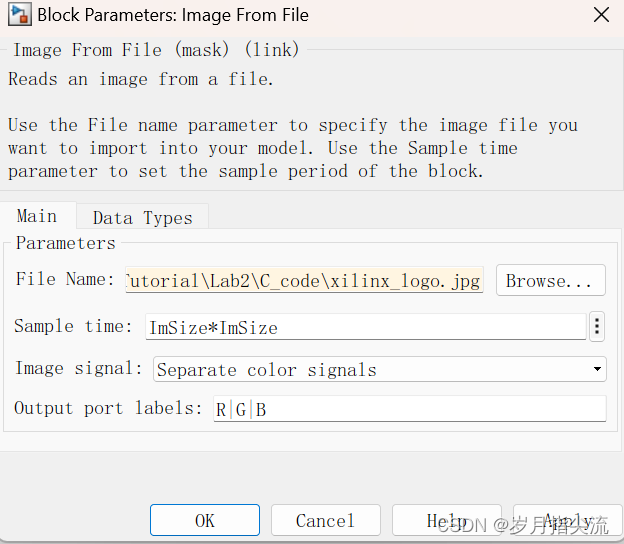

⑤、导航到噪声图像子系统,双击来自文件的图像块 xilinx_logo.png,打开源块参数对话框,使用 Browse 按钮确保文件名正确指向文件 xilinx_logo.jpg,如下所示

单击 “确定”,退出 “源块参数” 对话框。

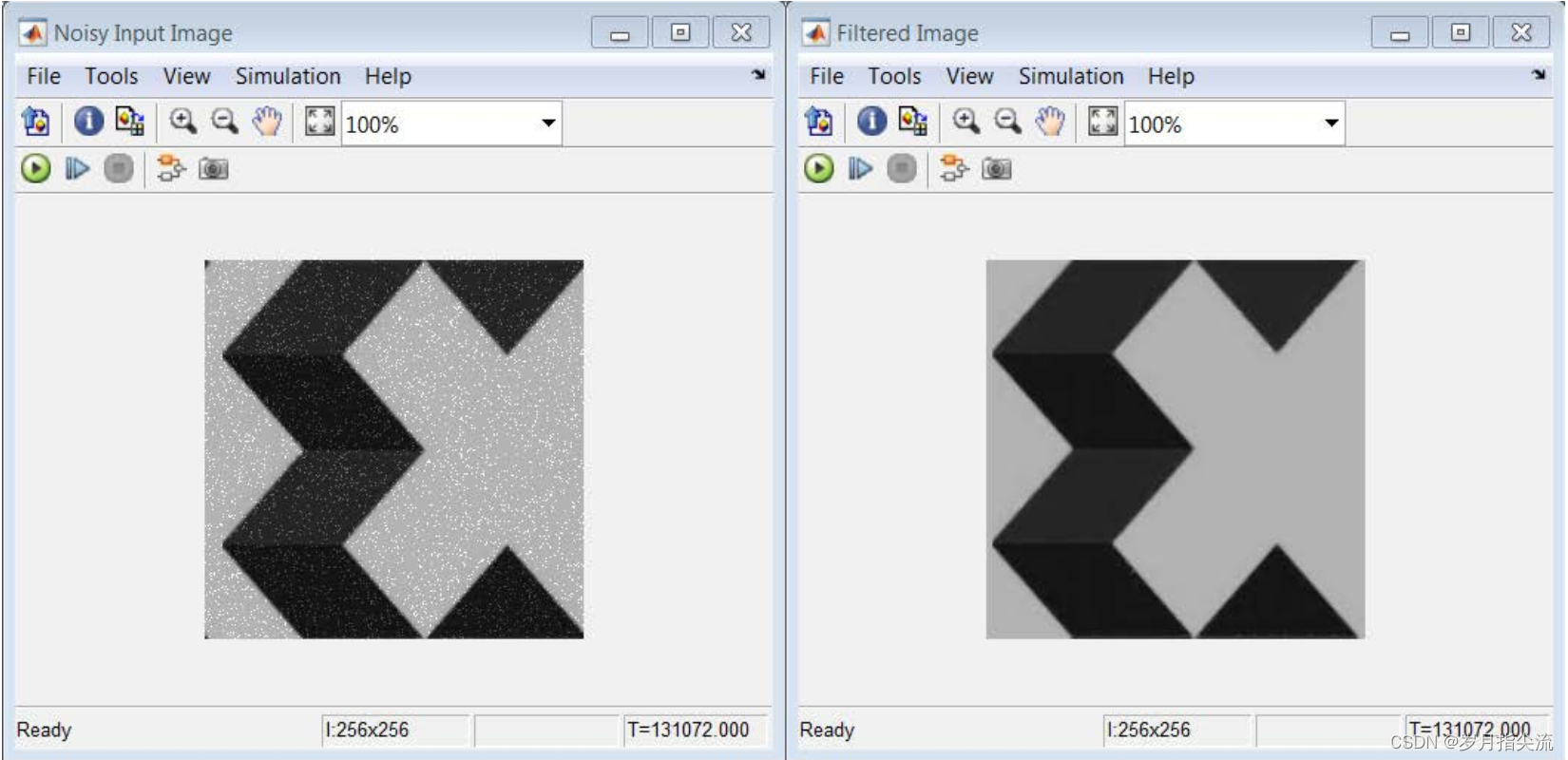

⑥、使用 “向上至父级” 工具栏按钮可返回到顶层,仿真设计并验证图像被过滤,如下图所示

总结

在这个实验室里你学到了

- 如何使用 M-Code 创建控制逻辑。最终的设计可用于创建 HDL 网络列表,与使用 Xilinx Blocksets 创建的设计相同

- 如何通过结合现有的 VHDL RTL 设计来使用 HDL 在 System Generator 中建模块,以及将 System Generator 模型的数据类型与 RTL 设计的数据类型匹配的重要性,以及如何在 System Generator 中模拟 RTL 设计

- 如何将用 C++ 编写的滤波器,用 Vivado HLS 进行合成,并将设计融入到 MATLAB 中。这个过程允许您使用任何 C,C++ 或 SystemC 设计,并创建一个自定义块用于您的设计。本练习向您展示了如何导入由 Vivado HLS 生成的 RTL 设计并在 MATLAB 中使用该设计

我的qq:2442391036,欢迎交流!