通用仪器指的是电子测试技术中涉及的仪器仪表,如:万用表,示波器,信号发生器,波形发生器,频谱分析仪,功率计,电源,等…… 用于测量,测试,控制,监测。

【FPGA应用场景】

通用仪器产品对于FPGA芯片算是高度依赖,涉及数据采集,传输,信号处理,协议转换,信号生成模拟,数据显示等相关技术。

拿我了解的一家国内龙头示波器厂商为例,主要是示波器用得最多(一半以上),然后是任意波形发生吕,射频仪器(频谱仪,网络分析仪),射频源,还有一些像万用表一类的测量装置会用到FPGA。会用到各个档次的FPGA,从几K 到 几百K的FPGA容量都有涉及,

数据采集:

FPGA与AD/DA 配合使用,这个很好理解,将模拟信号转成数字信号后,就交给FPGA来处理,或转换或加工或显示,还有将数字信号转为模拟信号用于控制和输出。这个对于FPGA的在线处理能力要求很高,需要有高速,高带宽,高算力,当然,这和具体的设备要求有关。不同要求使用不同档次的FPGA。各个档次FPGA,,最小有用到几K规模,最大的是,跨度很大。

数据运算:

数据要显示成各种波形或者数值,或者针对不同的通讯协议的数据进行解析或者封包,需要有大量的运算,这里涉及到不同的算法。如果数据需要实时显示,这时处理速度和数据支持的带宽非常重要。大量使用到的资源,一般会是DSP,DSP的运算能力和仪器的要求有关,按照国内某家中低端示波器的厂商,认为他们 一般是 12 * 12,或者 12 * 16 即可,更高位的运算实际上对他们是一种浪费。而对于这种乘法器的使用量,他们反馈,多多益善,在使用X厂商的V5P,会有3500个左右的DSP。他们都可以完全用完。当然,还有可能用到RAM,一般使用 Block RAM。对于示波器,会提供大量的算法,一些用硬件来实现,一些使用FPGA的软核来实现。

数据缓存:

如果数据的处理并非实时,数据量又是巨大的,无法及时处理,这时往往需要有缓存,一般是使用DDR。在DDR写满后再慢慢的进行读处理。

IO封装:

对于I/O的封装,需要尽量多的I/O,保证并行的性能和可扩展性。

多片协同:

示波器是多通道的,所以存在多片FPGA配合协同使用场景(各自负责不同通道)。·

渲染/显示

有时也会使用FPGA来完成刷屏,一般使用BlockRAM作为显存。这些显示比较初级,小的逻辑就可以搞定。

配合处理器CPU(Soc)

有时会配合CPU来使用,但经常并不是使用SoC,而是通过PCIe和ARM CPU进行配合使用,操作系统使用linux,少量使用X86,主要使用ARM。实际上,通用仪器行业对于Soc的需求并不大,因为他们认为SoC会带来不灵活,被绑定,他们宁愿自已搭配处理器来完成,因为他们对于设备的体积没什么要求。

【客户产品】

换一个角度来看仪器行业,把客户产品分为两种类型,接收型设备(万用表、示波器、网络分析仪)和发射型设备(任意信号发生器、射频源)。

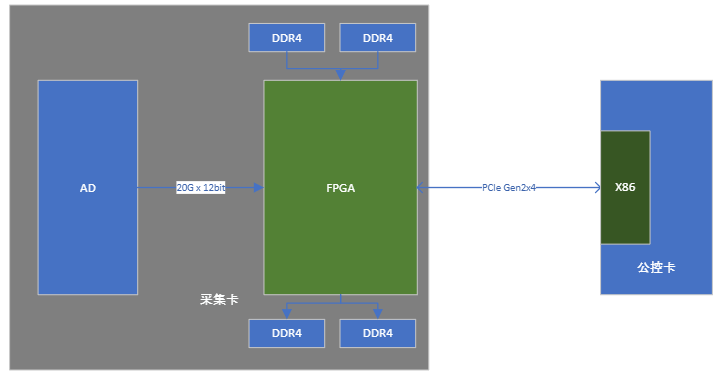

接收型设备:由采集卡(AD +FPGA)+ 公控板(处理器ARM或X86)组成系统,FPGA在采集卡上,负责处理AD的数字信号,进行数字信号处理工作卸载,将处理结果通过PCIe传输给工控板。发射型设备:射频源由发送卡(FPGA + DA) 完成。

总之,FPGA是在通用仪器应用是偏向数字信号处理。同一台设备中有可能用多片FPGA,比如高端的4通道示波器,会用2片FPGA,每片负责2个通道,再做一些互通、通道对齐的操作。

【板级框图】

以示波器为例:

【外围互联】(以某国内示波器厂商为例)

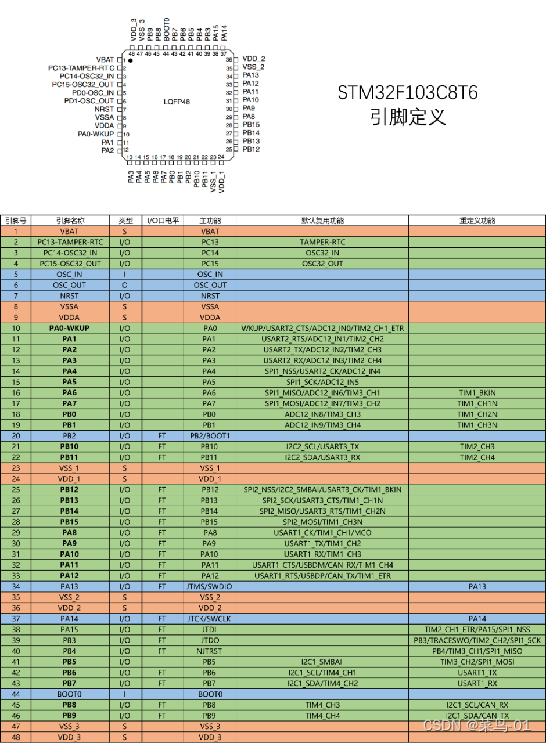

FPGA外围互联主要是和ADDA的JESD204B/C高速SerDes接口,以某国内厂商为例,目前最高是20Gbps x 12bit共计240Gbps的吞吐率。

和公控卡的CPU互联是PCIe Gen2x4,这个因为FPGA已经将数字信号处理卸载,和CPU通讯需要的带宽不高。另外因为AD数据量太大,无法做到实时处理,特别需要DDR外挂。最多的VU5P外挂了4组64位DDR4作为buffer。未来因为带宽需求更大,外围DDR已经没法满足需要,或者说对单板设计造成了过大的压力,已经在考虑用VU37P集成HBM的做产品。

【国内客户痛点】

AD高吞吐率和FPGA实时处理性能的矛盾,需要外挂DDR解决,所以需要的都是大封装器件。甚至会考虑HBM器件。

DSP资源几乎耗尽,目前鼎阳的AD分辨率都是12bit,因此乘法器只需要12x12 = 24bit。高宽度的DSP乘法器如不能拆分,使用起来很浪费。按照未来要求看,如果能将·27x27的乘法器拆分成2个比如12x16的乘法器,则会极大程度的改善DSP的资源紧张程度,成为FPGA器件核心竞争力。

对于这个行业理解不深,写得比较杂乱,后续有时间再深入。

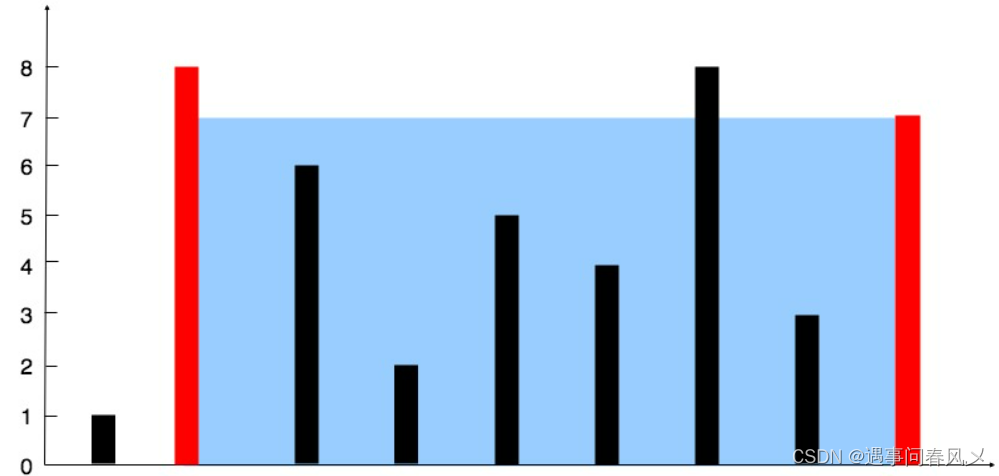

![排序---P1012 [NOIP1998 提高组] 拼数](https://img-blog.csdnimg.cn/6a4a35c6eaaf4767807c6c4c1b1f8c15.png)