利用DMA的触发循环实现对eTMR的PWM周期计数

文章目录

- 利用DMA的触发循环实现对eTMR的PWM周期计数

- 引言

- 分析问题

- eTMR的调试模式Modulization

- FTM的多次重载事件

- 终极大招-使用触发链

- 解决问题

- 确认DMAMUX中的eTMR相关触发源

- eTMR产生触发信号

- 软件

- 总结

- 参考文献

引言

最近在同客户一起适配一个无线充电电路控制系统的项目中,客户工程师向我提出了一个需求,希望能实现使用YTM32微控制器,对输出控制充电功率的PWM信号,每30个周期触发一次中断,用于调整占空比,这样便于动态调整向目标负载的供电功率。来活了,开搞。

分析问题

一开始我能想到的实现方式,是使用软件直接对产生PWM信号的eTMR模块的Overflow中断进行计数。但客户工程师King提到,需要输出的PWM信号频率可能会比较高,频繁进出eTMR的中断会影响CPU运行控制算法的效率,希望能够通过硬件机制实现。

eTMR的调试模式Modulization

此时,我最初想到的是利用eTMR输出信号的调制模式(Modulization)。调试模式实际上是将相互调制的两个输出信号进行逻辑与,然后再输出。此时,使用两路PWM,一路作为载波信号,另一路作为包络信号,控制载波信号,可以实现调输出控制信号占空比的功能(直流电机控制算法中调整负载驱动能力的过程中就用到了类似的思路)

26.4.16 Modulation Implementation

The eTMR0 and supports channel outputs modulated by eTMR1 channel 1 output. The eTMR3 supports channel outputs modulated by eTMR2 channel 1 output. Any of the 8 channels of eTMR0 and eTMR3 can be configured to support this modulation function. This function is enabled by configuring

CIM_ETMROPT1[ETMR0_CHxOUTSEL] and CIM_ETMROPT1[ETMR3_CHxOUTSEL]. See ETMR0 Output Modulation Select and ETMR3 Output Modulation Select for details.

但King提到,当前使用的YTM32B1MD14芯片的四个eTMR都被他用掉了,没有额外的eTMR可以专门用来产生载波信号(或者包络信号)。同时,调制模式是对时间进行同步控制的,但客户工程师明确提到,这个应用场景需要对周期数量进行控制,在PWM周期时间灵活变化的场景中,控制时长和控制数量是不等价的。因此,调制模式不适合解决这个问题。

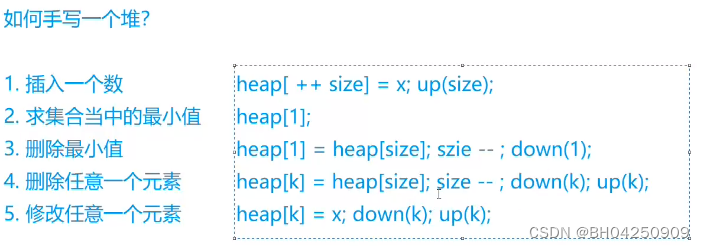

FTM的多次重载事件

King还提到,他记得之前他用过的一家友商微控制器平台上,就已经设计了这个功能。我一看,果不其然,确实有,对应着FTM模块的寄存器字段FTM_CONF[LDFQ],如图x所示。

FTM0->CONF = FTM_CONF_LDFQ(30);/* Allow each 32times reload opportunity interrupt */

通过阅读手册原文,我明确了思路,意识到在应用中的重点可能不是中断,而是调整占空比。这时,我想起来YTM32的手册里也有类似的关于Loading Frequency的设计。如图x所示。

其中大意是,eTMR的一些同计数相关的寄存器,同时还设计了缓冲寄存器(或称为“影子寄存器”),包括 CHMASK、INIT、MID、MOD、CH_VAL0和CH_VAL1。当启用eTMR后,这些寄存器的值就被锁定了,只有在特定的时刻才会从各自对应的影子寄存器中载入新值。

这其实也是一些能够适配高频率计数器的高级定时器的标配设计,为了获取更高的计数精度,计数的时钟源的频率有时甚至会高于驱动定时器外设数字部分工作的系统总线时钟频率,此时,通过总线设置的计数器相关寄存器的值,就需要在合适时刻,由两个时钟域同步后,才能生效(由影子寄存器载入到实际起作用的寄存器中)。

使用这个功能的意义还在于,留给软件一些时间,用于先后完成多个寄存器的配置,然后在同一个时间点上,让多个参数配置同时生效。在数字系统设计中,也称之为防止“冲突冒险”,否则,某些中间状态可能会意外触发系统崩溃(例如电机控制应用场景中,在某个瞬间可能同时导通H桥的上下两个桥臂,以至于烧掉电机的线圈导线)。

如果从当前King描述的单路PWM控制信号的应用场景上看,仅对单路PWM进行控制,不需要多路PWM协同工作的情况下,实际没啥必要启用这个缓冲的功能,要求硬件立即载入生效即可,这也是对软件最干净和友好的方式。

从手册上的描述来看,eFTM_SYNC[LDFRQ]是同FTM_CONF[LDFQ]功能最接近的,八成是他想要的。

终极大招-使用触发链

然而,我又察觉到了一种潜在的需求,或许King就是想要实现通过软件更新PWM占空比的节奏,因此提到了使用中断的需求(实际上经过同步多次载入事件的事件确实也能产生中断),并且提供的样例代码中使用了32次同步,而我们家的eTMR在这里最多仅能配置16次同步?我觉得这事可能还有下文,说不准还需要超过32次的周期,那时,仅靠eTMR或者FTM自身的设计,也不能完全搞定了。

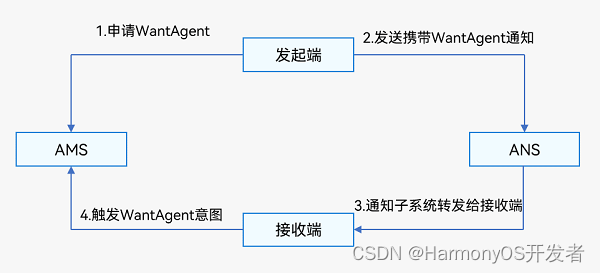

如此,我又想出来一个终极大招。我打算对PWM信号同时对外发出的触发信号Trigger进行计数,不过YTM32微控制器系统中没有专门对Trigger进行计数的外设模块(我印象中,只有老东家的LPC系列微控制器上的一个偏门的外设SCT,为了管理硬件实现的状态机模型,可以对Trigger计数并作为状态转换的一个判定条件),但幸运的是,YTM32中设计了一个基于大循环和小循环的DMA控制器,其中大循环就是对DMA的触发进行计数的,我可以利用DMA的大循环计数器来实现对eTMR的DMA触发信号计数。并且DMA的大循环(触发循环)也有重载机制(自动绕圈计数)和中断,并且长度可配置,远远超出32次的限制,完美符合对PWM脉冲累计计数可编程的需求。

解决问题

现在,大方向已经有了,就是要确定从eTMR的Overflow事件,到DMA的大循环,能不能走出一条通路。这就需要在手册里搜集零星的相关的描述,把所有线索串在一起。

从实现可能性从大到小,反推整个触发链:先要确认DMA控制器(DMAMUX)能够捕获到来自eTMR的触发信号,然后在eTMR中确认eTMR的触发信号能否同PWM的一次输出周期关联起来,最后再查阅如何配置eTMR产生对应的触发信号。这三个环节环环相扣,如果连不上,这事可能也就搞不成了。小心翼翼。。。

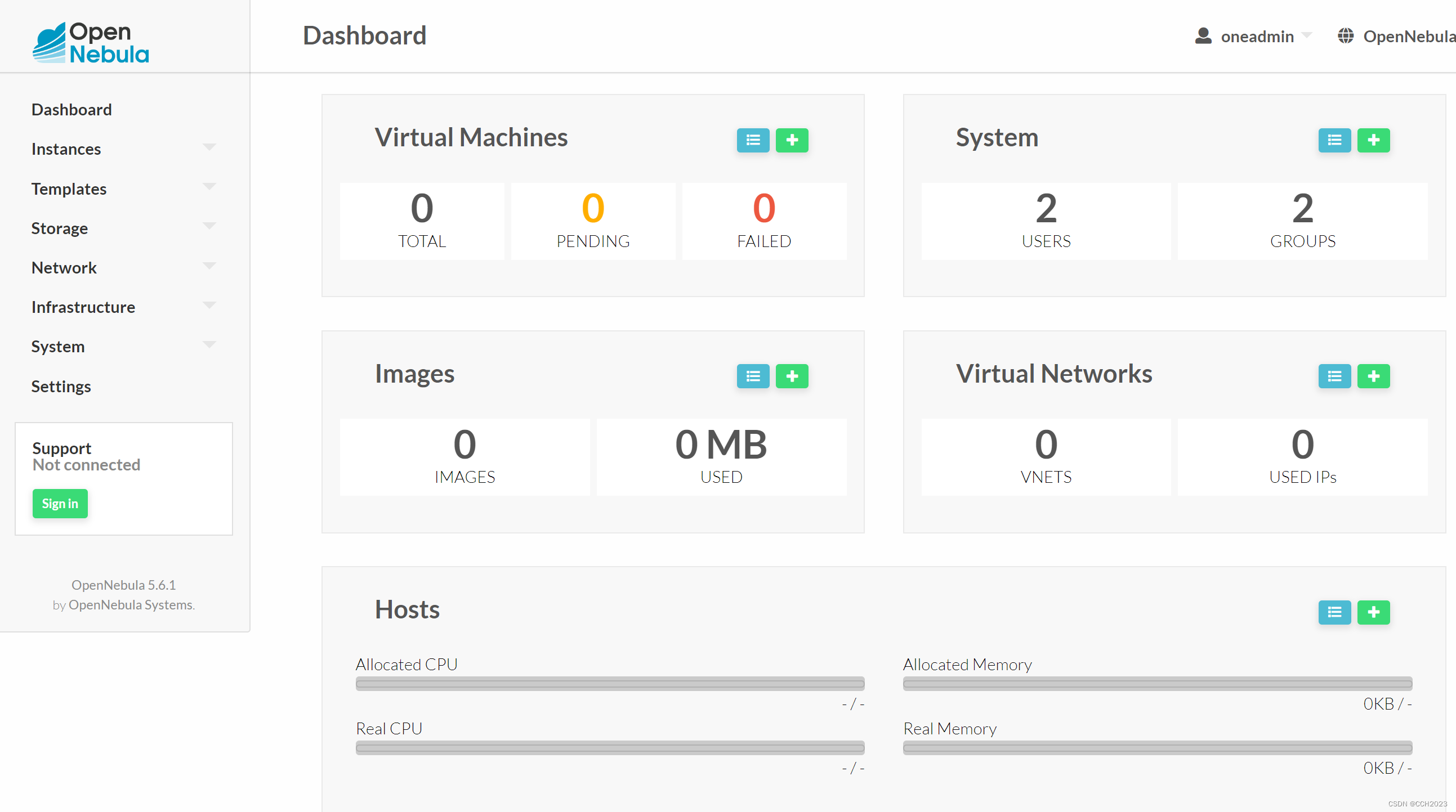

确认DMAMUX中的eTMR相关触发源

在DMA章节中,查阅关于DMAMUX的表项,它是芯片系统集成过程中列写的,每款芯片的DMAMUX表项都不一样,因此需要具体去查。如图x所示。

看到表中的内容,我差一点泪流满面,这真是诚意满满啊。这里要注意,此处DMAMUX能捕获的触发信号不是十分规整的,eTMR1和eTMR2包含的8个通道,每个通道是可以独占一个DMA触发通道的,而eTMR0和eTMR3就只能各自定时器的所有通道共享一个DMA触发通道。在本例中,将使用eTMR0的这个共享的触发通道进行说明。为什么选用这个通道呢?一方面是因为独占触发通道的用例更简单,另一方面,是因为客户工程师King那边现在用的就是eTMR0的CH2,如此调下来的用例可以在他的板子上验证。

OK,这里已经确认了,DMA是可以接收来自eTMR的触发信号。接下来就要看eTMR是如何产生这个触发信号了。

eTMR产生触发信号

查阅手册中关于eTMR的章节,在关于DMA的功能介绍中,有如下内容:

26.4.19 DMA

All eTMRs support DMA, this function is enabled by setting CH_CTRL[DMAEN]=1. The DMA request is generated when STS[CHxF]=1. The DMA request is cleared by clearing STS[CHxF]. The DMA priority is higher than the interrupt.

这段内容是说,通过配置eTMR_CHn_CTRL[DMAEN]=1,就能启用产生DMA触发的功能,相当于是把eTMR到DMAMUX的信号通路打开了,允许eTMR发出DMA触发信号(Request)。当eTMR通道的计数匹配事件产生后,eTMR_STS[CHxF]标志位置1,就会产生一个DMA的触发(原本也可以产生一个中断)。但这个标志位应该是需要被清零,才能捕获到下次触发。这里又说DMA的优先级高于中断,估计大概率不会需要通过中断服务程序清零了。一种可能的情况是,DMA捕获到来自外设的触发信号后,向外设回发的应答信号,可以用来作为硬件清零CHxF标志位的操作。

但进一步理解下,这里还要注意,不能直接用eTMR的计数器溢出事件触发,而必须通过一个通道的事件触发。因此为了产生DMA的触发信号,还需要再启用一个eTMR通道。这个问题不大,单从具体的应用场景看,反正是要产生PWM信号的,直接用这个输出PWM波形的通道触发DMA,也是可行的。有一些资深的玩家可能要提问了,那有没有可能仅用定时器触发DMA呢?比如要使用固定周期的DMA向UART引擎送数,向总线上发送心跳数据包。答案是,没有。目前在YTM32B1MD微控制器的DMAMUX中,入选的定时器只有eTMR,(其他例如TMR、LPTMR、pTMR等尚未入选),而使用eTMR则不得不通过一个eTMR通道才能产生DMA触发。但是,YTM32微控制器平台上还涉及了另一个同触发相关的外设TMU(Trigger Mux Module),其中收纳了pTMR,也能发挥一定的联动作用)

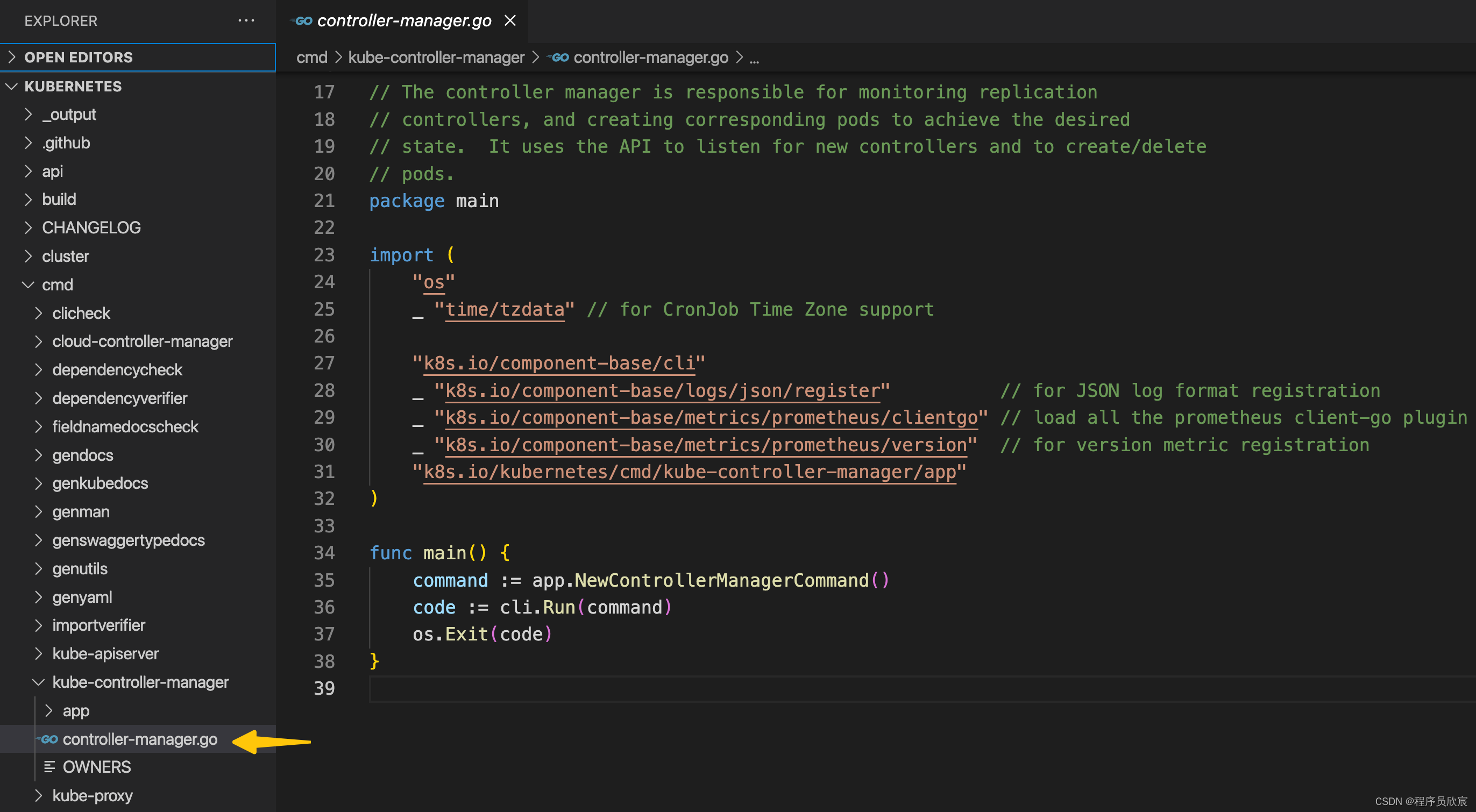

软件

编写本例的软件工程源代码,编译,下载,调试,可以正常触发DMA中断,说明已经搭建起触发链,按照预期方式工作。详情源码可见:https://gitee.com/suyong_yq/arm-mcu-sdk/blob/master/applications/demo_apps/basic/etmr_trigger_dma_counter/main.c。

但在调试过程中出现一点小插曲。我在样例工程中设定eTMR的PWM的频率是100Hz,指定DMA捕获到1000次PWM的触发信号后触发一次中断。如代码所示:

void etmr_init(void)

{

/* setup counter. */

eTMR_CounterInit_Type etmr_init;

etmr_init.ClkSrc = eTMR_CounterClkSrc_BusClk;

etmr_init.ClkFreqHz = CLOCK_FIRC_FREQ_HZ;

etmr_init.StepFreqHz = CLOCK_FIRC_FREQ_HZ / 100000u; /* 100khz. */

etmr_init.InitVal = 0u;

etmr_init.MidVal = 0u;

etmr_init.ModVal = 1000; /* 100 hz for timeout. */

etmr_init.EnableRunningOnDebug = false;

etmr_init.EnableGlobalCountingBase = false;

eTMR_InitCounter(BOARD_ETMR_PORT, &etmr_init);

/* setup channel. */

eTMR_ChannelOutputCompareInit_Type etmr_chn_init;

etmr_chn_init.EnableComplementaryMode = false;

etmr_chn_init.EnableDoubleSwitchMode = false;

etmr_chn_init.InitOutputLogic = eTMR_OutputLogic_Low;

etmr_chn_init.EnableDma = true; /* enable to generate request to trigger the dma. */

etmr_chn_init.OutputCompareEventForVal0 = eTMR_OutputCompareEvent_ToOutputLogic1;

etmr_chn_init.OutputCompareEventForVal1 = eTMR_OutputCompareEvent_ToOutputLogic0;

etmr_chn_init.Val0 = 0;

etmr_chn_init.Val1 = 200;

eTMR_InitChannelOutputCompare(BOARD_ETMR_PORT, BOARD_ETMR_CHN, &etmr_chn_init);

}

void etmr_dma_init(void)

{

/* setup dma. */

dma_init(1000); /* collect pwm triggers for each period. */

/* setup etmr. */

etmr_init();

/* start etmr counter. */

eTMR_StartCounter(BOARD_ETMR_PORT);

}

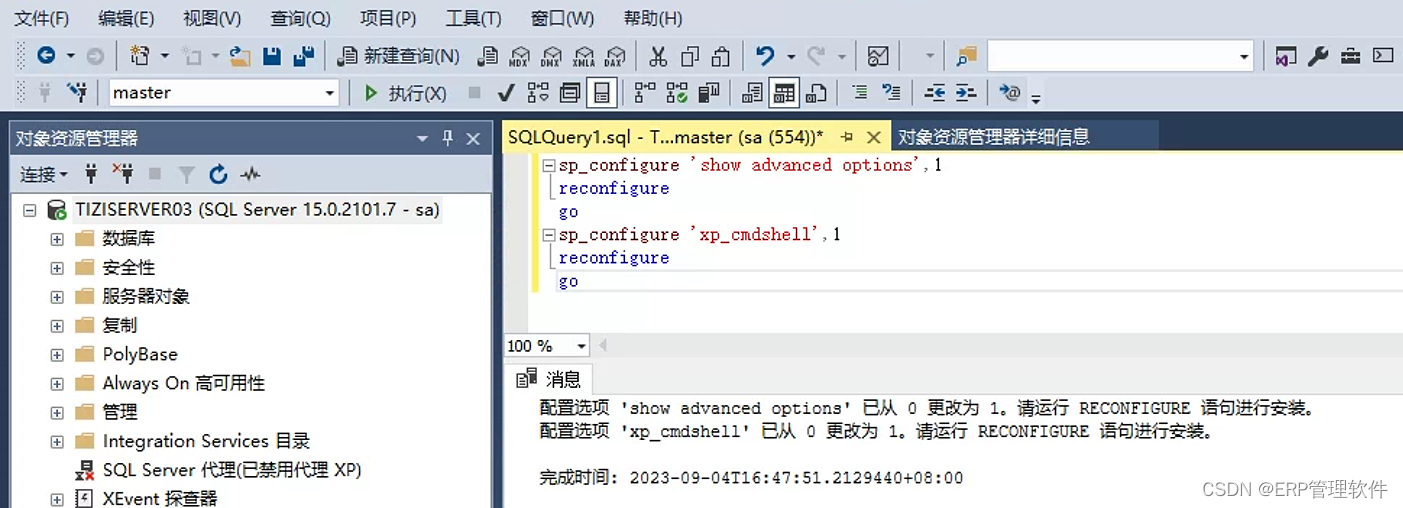

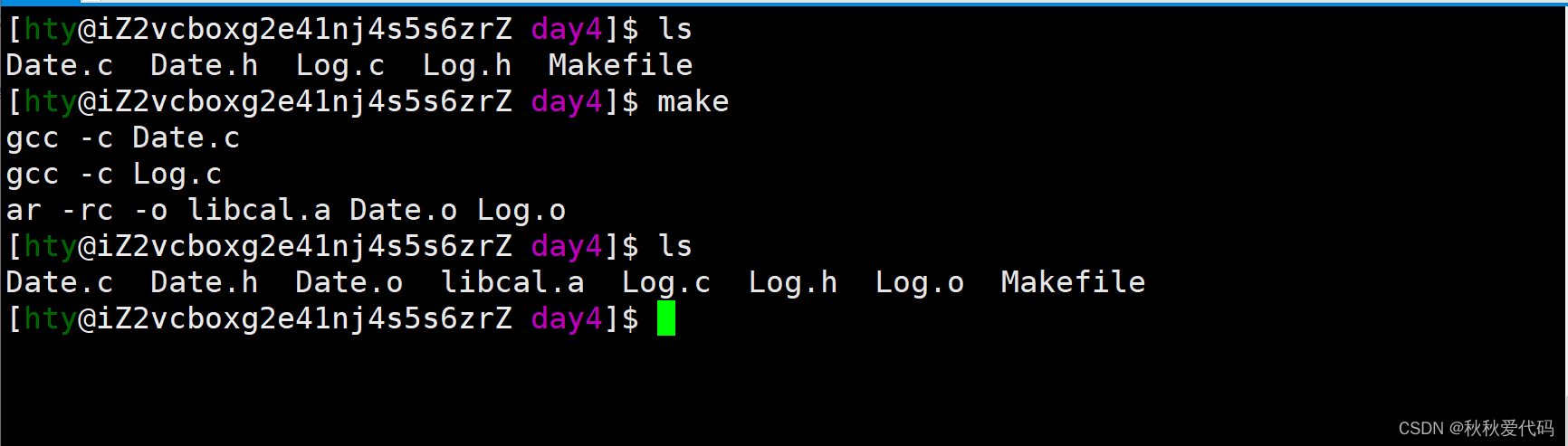

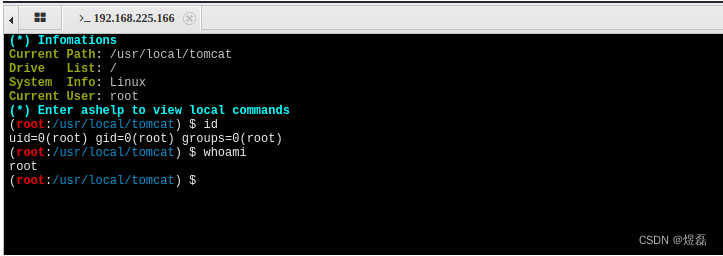

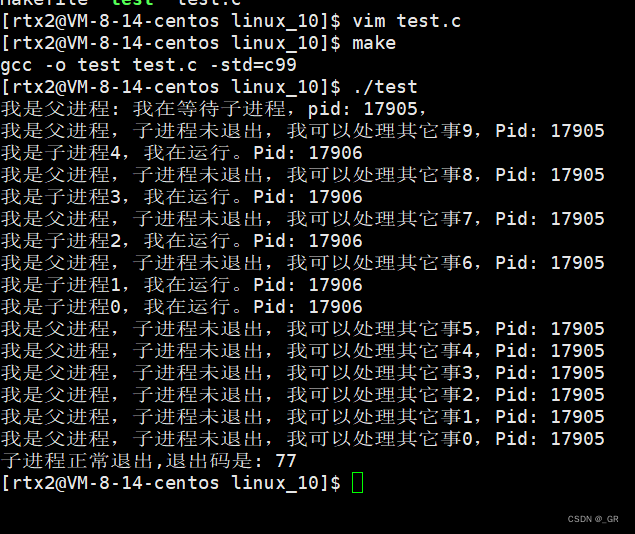

预计触发DMA中断的时间间隔大约在10s左右,但实际上,触发DMA中断的周期基本上在5s,频率差了2倍??如图x所示。

再翻了翻手册,总算是找到root cause了。在手册中关于输出比较模式的介绍中提到,每个通道配备的两个匹配事件,都可以让标志位CHxF置位,那也就意味着,每个PWM周期都会产生两个触发信号。这也就解释了DMA中断触发的周期比预想中少了一半的情况。如果还想得到预定时间长度的中断周期,就得把大循环的长度设置为双倍!

26.4.5 Output Compare Mode

When CHx_CTRL[CHMODE]=0x2, the channel x is in output compare mode. In this mode, each channel can set, clear, or toggle the output when the counter reaches the specific value defined by CH_VAL0[VAL0] and CH_VAL1[VAL1]. Configure CH_CTRL[VAL0CMP] and CH_CTRL[VAL1CMP] to select the action of the corresponding channel when the counter reaches the CH_VAL0[VAL0] and CH_VAL1[VAL1]. As shown in Figure eTMR Output Compare. The channel flag (STS[CHxF]) will be set when a compare event occurs.

总结

本例实现了一种利用DMA的大循环(触发循环)对eTMR模块产生PWM信号波形进行计数并产生周期中断的功能,相对于硬件IP通过重载同步机制中设计的计数方式,本例利用对DMA触发信号进行计数,可以实现更多数量的计数,并且具有更广泛的普适性。

文中使用的DMA触发计数方法,不仅仅可用于对定时器触发信号的计数,还可用于实现对DMAMUX能够捕获的其他触发信号的计数。更进一步,如果配合其他的触发管理设备(例如Trigger Mux),形成触发链,还可以进一步扩大DMA触发计数方法的适用范围。

参考文献

- S32K-RM.pdf,https://www.nxp.com/products/processors-and-microcontrollers/s32-automotive-platform/s32k-auto-general-purpose-mcus/s32k1-microcontrollers-for-automotive-general-purpose:S32K1

- YTM32B1MD1x_RM_v1.1.pdf