目录

1.CMOS逻辑设计

1.1 基本MOS结构

1.2 COMS逻辑门

1.3 标准单元

2.CMOS单元建模

3.电平翻转波形

4.传播延迟

5.波形的转换率

6.信号之间的偏移

7. 时序弧和单调性

8.最小和最大时序路径

9.时钟域

10.工作条件

1.CMOS逻辑设计

1.1 基本MOS结构

MOS(Metal Oxide Semiconductor,金属氧化物半导体)晶体管。源极和漏极之间的距离就是MOS晶体管的长度。用来制造MOS晶体管的最小长度通常就是CMOS技术工艺的最小特征尺寸(Feature Size)。举例来说,0.25μm工艺允许MOS晶体管有0.25μm或者更大的沟道长度。通过缩小沟道的尺寸,晶体管的尺寸会变小,这样在一定区域内就可以封晶体管。正如我们所知的,更小的尺寸也会让设计在更高的速度上运行。

1.2 COMS逻辑门

CMOS逻辑门是用NMOS和PMOS晶体管搭建的。CMOS反相器可以说是最基本的逻辑门了。CMOS反相器的两种稳定状态取决于输入的状态。当输入A是低电平(Vss或者逻辑0),NMOS晶体管是关断(Off)状态,PMOS晶体管是导通(On)状态,这导致输出Z被上拉至Vdd,也就是逻辑1。当输入A是高电平(Vdd或逻辑1),NMOS晶体管是导通状态,PMOS晶体管是关断状态,这导致输出Z被下拉到Vss,也就是逻辑0。在上述两种状态的任一种里,CMOS反相器都是稳定的,不会从输入A或者电源Vdd吸取任何电流。

CMOS反相器的特性可以扩展到任何CMOS逻辑门。在CMOS逻辑门中,输出节点被上拉结构(由PMOS晶体管构成)连接到Vdd,被下拉结构(由NMOS晶体管构成)连接到Vss。举例来说,图2-3所示为一个两输入的CMOS与非门(Nand Gate)。在本例中,上拉结构由2个并联的PMOS晶体管构成,下拉结构由2个串联的NMOS晶体管构成。

对于任何CMOS逻辑门,上拉和下拉结构是互补的。对于逻辑0或者逻辑1的输入,如果上拉状态是导通的,那下拉状态是关闭的;类似地,如果上拉状态是关闭的,那下拉状态就是导通的。下拉和上拉结构是被CMOS门实现的逻辑函数控制的。例如,在CMOS与非门中,控制下拉结构的函数是“A与B”,也就是说,当A和B都是逻辑1,下拉结构导通。类似地,控制上拉结构的函数是“不是A,或者不是B”,也就是说,当A或B至少有1个是逻辑0,上拉结构导通。这些特性确保了基于控制上拉结构的函数,输出节点的逻辑会被上拉到Vdd。因为下拉结构是被互补函数控制,当上拉结构的函数结果为0,输出节点会处于逻辑0。

对于逻辑0或者逻辑1的输入,在稳定状态下,CMOS逻辑门不会从输入或者电源吸取任何电流,因为上拉结构和下拉结构不会同时处于导通状态。(只有在转换时,上拉结构和下拉结构才会同时处于开启状态)(但是由于CMOS工艺的特性,稳定状态也会有很小的漏电流被吸收,而且,随着深亚微米工艺尺寸越来越小,漏电流的影响逐渐增大,已不容忽略)。CMOS逻辑的另1个重要方面是输入仅对上一级构成电容性负载(Capacitive Load) 。-----即分析时,作为上一级的输出电容组成部分。

总结一下,现在常见的数字集成电路其底层的基本逻辑电路都是由CMOS结构构成。上拉逻辑部分由PMOS组成,下拉逻辑部分由NMOS组成。反相器就是一个最基本的CMOS逻辑电路,上拉部分只有一个PMOS,下拉部分只有一个NMOS。

1.3 标准单元

芯片中的大多数复杂功能通常是由基本的构建模块来实现的。基本的模块实现了简单的逻辑功能,比如与(And)、或(Or)、与非(Nand)、或非(Nor)、与或非(And-Or-Invert)、或与非(Or-And-Invert),以及触发器(Flip-Flop)。这些基本的模块是预先设计好的,被称为标准单元(Standard Cell)。标准单元的功能和时序经预先特征化(Pre-Characterized),供设计师使用。设计师就可以使用标准单元作为基;构建模块来实现需要的功能。

上文描述的CMOS逻辑门的关键特性是适用于所有CMOS数字设计的。当处于稳定的逻辑状态,所有的数字CMOS单元都不会从电源吸取电流(漏电流除外)。所以,大部分的功耗是和设计的活动相关,是由设计中的CMOS单元输入端的充放电引起的。

什么是逻辑1或者逻辑0?在CMOS单元里,VIHmin和VILmax定义了范围:任何高于VIHmin的电压都被认为是逻辑1,任何低于VILmax的电压都被认为是逻辑0。如下图所示。VIHmin和VILmax的值是从标准单元的直流传输特性中得来的。

2.CMOS单元建模

如果一个标准单元的输出引脚驱动多个扇出单元,该输出引脚的总电容,就等于所它驱动的单元的输入引脚电容,加上组成该线(Net)的所有线段(Wire Segment)的电 容,再加上驱动单元的输出电容。(这就是线载模型计算延迟的根本思想)

注意,在CMOS单元中,单元的输入只表现为电容负载。

下面展示一个例子:1个单元G1驱动了3个其他单元——G2、G3和G4。Cs1、s2、Cs3和Cs4是组成这条线的所有线段的电容值。所以:

Total cap (Output G1) = Cout(G1) + Cin(G2) + Cin(G3) +Cin(G4) + Cs1 + Cs2 + Cs3 + Cs4

# Cout是单元的输出引脚电容。

#Cin是单元的输入引脚电容。

这个总电容就是单元G1翻转的时候需要充放电的电容,所以总电容的值影响单元G1的时序。

从时序的角度看,我们需要对CMOS单元建模,来帮助我们分析经过该单元的时序。每个输入引脚都指定了输入引脚电容。每个输出引脚也可以指定电容,但大部分CMOS逻辑单元都没有包括输出引脚的电容。

当输出为逻辑1,输出级的上拉结构导通,它提供了一条从输出到Vdd的路径。类似地,当输出为逻辑0,输出级的下拉结构提供了一条从输出到Vss的路径。当CMOS单元的状态翻转时,翻转的速度是由输出线(Output Net)电容的充放电速度决定的。输出线电容(见图2-5)的充放电是通过上拉结构和下拉结构分别进行的。注意,上拉结构和下拉结构中的通道对输出的充放电路径构成电阻。充放电路径的电阻是决定CMOS单元速度的主要因素。上拉电阻的倒数被称为单元的输出高电平驱动(Output High Drive)。输出上拉结构越大,上拉电阻越小,单元的输出高电平驱动就越大。更大的输出结构也意味着这个单元有更大的面积。输出上拉结构越小,单元的面积越小,单元的输出高电平驱动越小。同样的概念也可以应用到下拉结构上,它决定了下拉路径的电阻值以及输出低电平驱动(Output Low Drive)。通常,单元被设计成有相似的上拉和下拉驱动能力。

输出驱动决定了可以驱动的最大电容负载。而最大电容负截又决定了最大扇出(Fan-out)的数量,也就是说,决定了可以驱动多少个单元。更高的输出驱动对应着更低的输出上拉和下拉电阻,这让单元在输出引脚可以充放电更大的负载。

图2-6所示为CMOS单元的等效抽象模型。这个模型是为了抽象出单元的时序行为,所以仅对输入级和输出级建模。这个模型不能表达单元的内在延迟或电学行为。

CpinA是单元输入A的输入引脚电容。Rdh和Rdl是单元输出驱动电阻,这2个电阻会根据单元驱动的负载来确定输出引脚Z的上升和下降时间。这个驱动电阻也决定了单大扇出限制。

图2-7中的线和图2-5是一样的,不同的是图2-7是用等效模型来表示单元。

Cwire = Cs1 + Cs2+ Cs3 + Cs4

Output charging delay (for high or low) = Rout *(Cwire + Cin2+Cin3+Cin4)在上面的表达式中, Rout是Rdh或者Rdl中的1个。Rdh是上拉输出电阻, Rdl输出驱动电阻。

3.电平翻转波形

如图2-8a所示,当闭合开关SWO,电压施加到RC网络,输出变为逻辑1。假设当SW0时,电压尚处在OV,输出端电压转换(Voltage Transition)由以下公式表示:

该上升电压波形如图2-8b所示。乘积(Rdh*Cload)被称为RC时间常数,通常该常数和输出的转换时间(Transition Time)有关。

当断开SW0并闭合SW1,输出从逻辑1变为逻辑0,输出电压转换如图2-8c所示出电容通过处于导通状态的SW1放电。这种情况下,输出电压转换由以下公式表示:

在一个CMOS单元中,因为PMOS上拉晶体管和NMOS下拉晶体管会在极短的时间内同时导通,所以输出的充放电波形看起来不会像图2-8中RC的充放电波形那样。图2-9说明了在输出从逻辑1翻转到逻辑0的不同阶段,一个CMOS反相单元内的电流路径。图2-9a说明了当上拉和下拉结构同时导通时的电流流动。随后,图2-9b说明了上拉结构关断后的电流流动。当输出到达最终状态后,由于电容Cload完全放电,此时没有电流流动。

图2-10a说明了CMOS单元输出上的典型波形。注意转换波形是如何逐渐向Vss轨和Vdd轨弯曲的,且波形的线性部分处于波形的中间位置。

后续,我们将用图2-10b中所示的简化图来描述一些波形。它显示了波形具有转换时间,也就是从1个逻辑状态转换到另1个逻辑状态所需要的时间。图2-10c显示了同样的波形但是转换时间为0,这是理想波形。

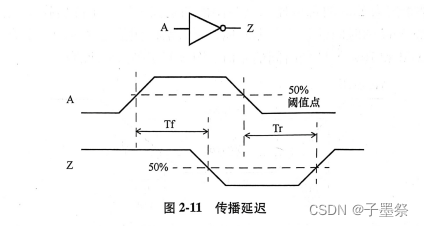

4.传播延迟

考虑一个CMOS反相单元以及它的输入和输出波形。单元的传播延迟(Propagation)是用翻转波形上的一些测量点来定义的。比如用以下4个变量来定义的点 :

#输入下降沿阈值点:

input_threshold_pct_fall : 50.0;

#输入上升沿阈值点:

input_threshold_pct_rise : 50.0;

#输出下降沿阈值点:

output_threshold_pat_fall : 50.0;

输出上升沿阈值点:

utput_threshold_pct_rise : 50.0;这些变量是一个指令集的一部分,该指令集是用来描述单元库的。这些阈值参数是由Vdd或者电源的百分比定义的。对大多数标准单元库来说,通常50%的阈值被用来测量延迟。上升沿是指从逻辑0 到1的转换,下降沿是指从逻辑1到逻辑0的转换。

以图2-11中的反相器单元和引脚的波形为例。传播延迟用以下值表示:

1)输出下降沿延迟(Tf)

2)输出上升沿延迟(Tr)

通常这2个值是不同的。图2-11说明了这2个传播延迟是如何测量的。

如果我们只考虑理想波形,传播延迟就只是简单的2个沿之间的延迟,如图2-12所示。

5.波形的转换率

转换率(Slew Rate)被定义为改变的速率。在STA中,上升或下降波形是用电平转换的快慢来测量的。转换率通常是由转换时间(Transition Time)来衡量的,转换时间就是信号在两个指定电平之间转换所需要的时间。注意,转换时间实际是转换率的倒数——转换时间越大,转换率越慢,反之亦然。图2-10说明了CMOS单元输出上的典型波形。这个波形在末段是渐进的,很难判断转换时间精确的开始和结束点。因此,用指定的阈值水平来定义转换时间。 例如,转换率阈值设置可以是:

#下降沿阈值:

slew_lower_threshold_pct_fall : 30.0;

slew_upper_threshold_pct_fall : 70.0;

#上升沿阈值:

slew_lower_threshold_pct_rise : 30.0;

slew_upper_threshold_pct_rise : 70.0;这些阈值被指定为Vdd的百分比。这些阈值的定义表明,下降转换率就是下降涨70% Vdd和30% Vdd的时间的差值。类似地,上升沿的阈值定义表明,上升转换率就升沿到达30% Vdd和70% Vdd的时间的差值。图2-13用图形来说明。

6.信号之间的偏移

偏移(Skew)是两个或多个信号的时序之差,信号可以是数据也可以是时钟。 比如果1个时钟树(Clock Tree)有500个终点,有50ps的偏移,这意味着最长的时钟路与最短的时钟路径的延迟差为50ps。图2-15展示了1个时钟树的例子。时钟树的起点通常是定义时钟的节点。时钟树的终点通常是同步元件(比如触发器)的时钟引脚。时钟延迟(Clock Latency)是信号从时钟源(Clock Source)到终点的时间。时钟偏移(Clock Skew)是时钟树到达每个终点的时间差。

一个理想的时钟树是假设时钟源拥有无限的驱动能力,也就是说时钟可以驱动无限多个终点且没有延迟。另外,时钟树包含的任何单元都假定为0延迟。在逻辑设计的早期,STA通常是假设理想时钟树来进行的,这是为了专注分析数据路径。在理想时钟树中,默认时钟偏移为 0 ps 。可以用约束 set_clock_latency 来明确指定时钟树的延迟(Latency)。下面的例子指定了时钟树的延迟:

set_clock_latency 2.2 [ get_clocks BZCLK]

#上升沿和下降沿的延迟都是2.2ns.

#如果上升沿和下降沿的延迟不一致,用-rise和-fall来分别指定.时钟树的时钟偏移( Clock Skew)也可以用约束 set_clock_uncertainty 来明确设定具体的值:

set_clock_uncertainty 0.250 -setup [get_clocks BZCLK]

set_clock_uncertainty 0.100 -hold [get_clocks BZCLK]set_clock_uncertainty 指定了1个时间窗口,时钟的沿可能在这个窗口内的任意时间出现。这个时钟沿时序的不确定性(Uncertainty)是为了考虑到几个因素,比如时钟周期的抖动(Jitter),以及时序验证需要的额外余量(Margin)。每一个真实的时钟源都有一定量的抖动,所谓抖动就是1个时间窗口,时钟沿可能出现在窗口内的任意时间。时钟周期抖动是由时钟发生器的类型决定的。现实中,没有理想的时钟,也就是说所有的时钟都有一定量的抖动,而且在定义时钟的不确定性时应包含抖动。

在时钟树实现(Implemented)之前,时钟的不确定性也必须包含实现后可预期的偏移(Skew)。

我们可以为建立时间检查(Setup Check)和保持时间检查(Hold Check)分别设定不同的时钟不确定性。保持时间检查的不确定性不需要包括时钟抖动,所以通常保持时间检查的不确定性比较小。

图2-16的例子展示了1个具有250ps不确定性的时钟。图2-16b展示了逻辑个触发器的可用时间是如何减去不确定性的。这相当于验证设计可以运行在更高的频率上。

如图2-16所指定, set_clock_uncertainty 也可以用来建模任何额外的余量。比如,一个设计师可能会用50ps的时序余量作为设计中的额外悲观余量。这部分可以被加到 set_clock_uncertainty 命令中。通常,在时钟树被实现( Implemented)前,clock_uncertainty 指定的值通常要包括时钟抖动( Jitter)、时钟偏移( Skew)、以及悲观值。

set_clock_latency 2.0 [ get_clocks USBCLK]

set_clock_uncertainty 0.2 [ get_clocks USBCLK]

#200ps的不确定性可能包括了50ps的时钟抖动、100ps的时钟偏移,以及50ps#的额外悲观值。我们之后将会看到 set_clock_uncertainty 是如何影响建立时间和保持时间的检查。时钟不确定性考虑成最终裕量(Slack)计算时的偏离(Offset)。

总结一下,时钟的不确定性其实对时序的建立时间和保持时间检查都提出了更高的要求。

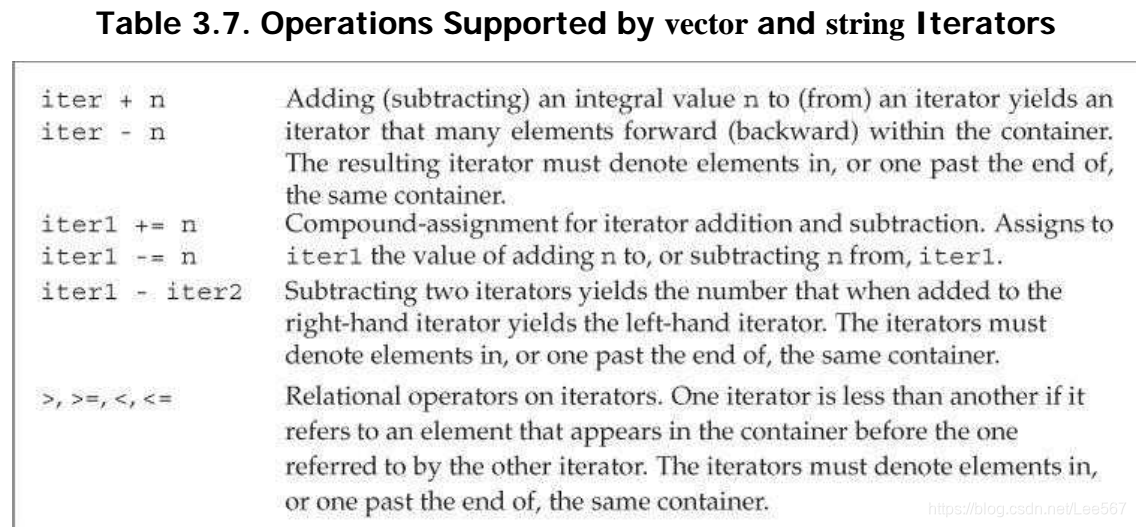

7. 时序弧和单调性

每1个单元都有多个时序弧(Timing Arc)。举例来说,1个组合逻辑单元,比如(And)、或门(Or)、与非门(Nand)、或非门(Nor)、加法器(Adder)单元,每个输入到每个输出都有时序弧。时序单元比如触发器,有从时钟到输出的时序弧,有数据引脚(Data Pin)对时钟的时序约束(Timing Constraint)。每个时序弧都有时序(Timing Sense),也就是说,对应输入上不同类型的转换(Transition),输出是如何的。如果输入的上升转换引起输出的上升(或者不变),输入的下降转换引起输出的(或者不变),这都是正单调(Positive Unate)。比如,与门和或门的时序弧就是正单调,如图2-17a所示。

如果输入的上升转换引起输出的下降转换(或者不变),输入的下降转换引起输出的上升转换(或者不变),这都是负单调(NegativeUnate)。比如,与非门和或非门的时序弧就是负单调,如图2-17b所示。

如果输出的转换不能由输入转换的方向单独决定,也要取决于其他输入的状态,这就是非单调(Non-unate)时序弧。比如,异或门(XOR)的时序弧就是非单调的,如图2-17c所示。

单调性对时序是很重要的。它决定了电平沿(电平转换)是如何通过单元传播的,以及是如何出现在单元输出上的。可以利用时序弧的非单调性,比如使用异或门来翻转时钟的极性(Polarity),如图2-18所示。如果输入POLCTRL是逻辑0,单元UXOR0输出上的时钟DDRCLK和输入时钟MEMCLK有一样的极性。如果POLCTRL是逻辑1,单元UXORO输出上的时钟就有和输入时钟MEMCLK相反的极性。

8.最小和最大时序路径

逻辑传播通过逻辑路径的总时间被称为路径延迟(Path Delay)。这包括通过路径上各种逻辑单元(Cell)以及线(Net)的总延迟。通常情况下,逻辑可以通过几条不同的播到终点。而实际路径取决于这条逻辑路径上其他输入的状态,如图2-19中的例子。到达终点有多条路径,可以得到到达终点的最大时序和最小时序。相应地,最大时序最小时序路径被分别称为最大路径(Max Path)和最小路径(Min Path)。2个端点的最大路径就是拥有最大延迟的路径(也就是最长路径)。类似地,最小路径就是拥有最小延迟(也就是最短路径)。请注意,最长和最短指的是路径上的累计延迟,而不是路径元个数。

图2-19展示了1条触发器间的数据路径。UFF1和UFF3之间的最大路径UNANDO、UBUF2、UOR2以及UNAND6单元,而最小路径是经过UOR4和UNAND6 注意在这个例子里,最大和最小路径的终点都是触发器UFF3的D引脚(Pin)。

最大路径通常也叫作晚路径(Late Path),最小路径通常也叫作早路径(Early Patth)。

当考虑1条从UFF1到UFF3这样的触发器到触发器的路径,1个触发器发出数据个触发器接收数据。这种情况下,因为UFF1发出数据,UFF1就被称为发射触发器(Launch Flip-flop)。UFF3捕获数据,UFF3 被称为捕获触发器(Capture Flip-flop)。“发射”和“捕获”这样的术语不是固定的,是由触发器到触发器的路径决定的。比如果1条路径中任何触发器捕获了UFF3发射的数据,UFF3就变成了发射触发器。

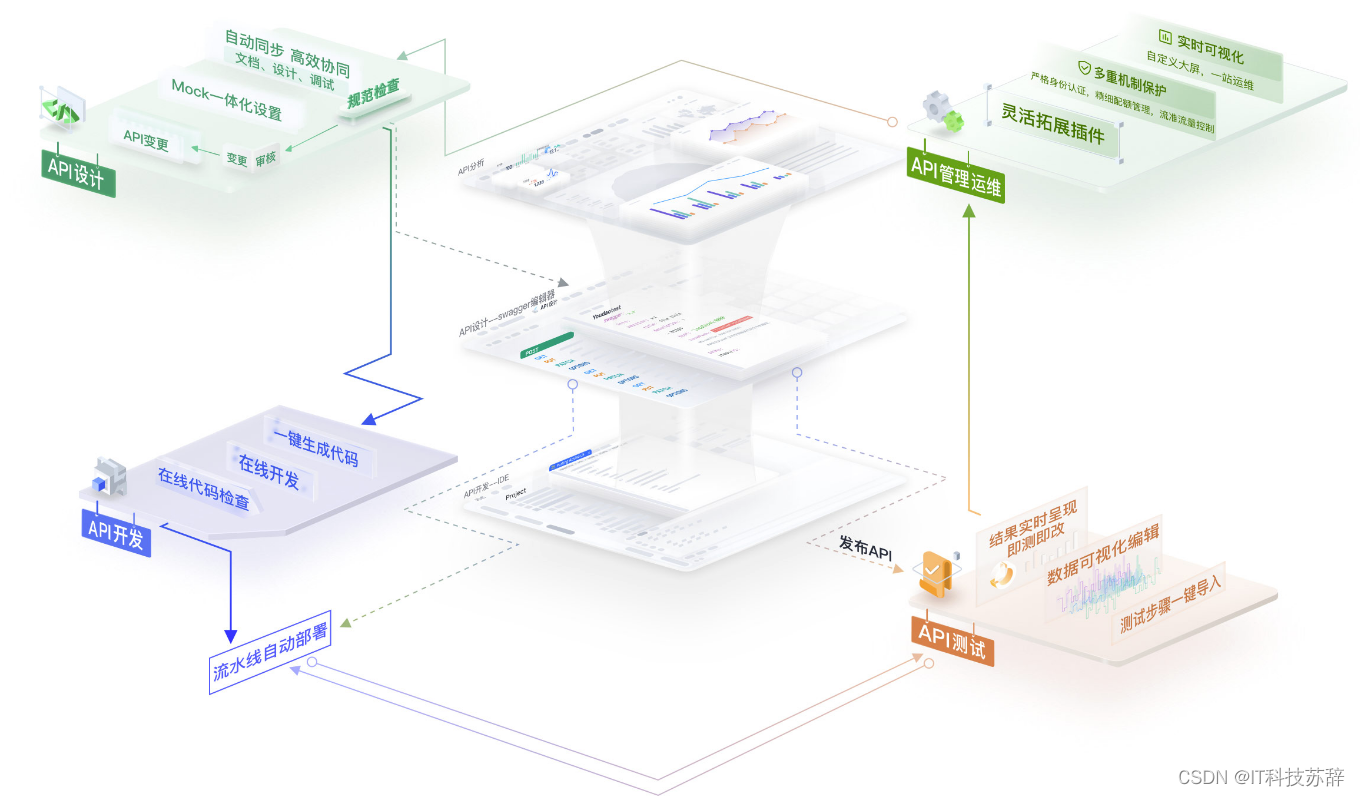

9.时钟域

在同步逻辑设计中,1个周期时钟信号将计算出的新数锁存到寄存器中。这个新数据是基于上1个时钟周期的触发器值。锁存的数据被用来计算下1个时钟周期的数据。

1个时钟通常驱动许多触发器。由同一个时钟驱动的一组触发器被称为的时钟域(Clock Domain)。在1个典型的设计中,通常有多个时钟域。比如,200个触发器可以被时钟USBCLK驱动,1000个触发器可以被时钟MEMCLK驱动。图2-20描述了和它们的时钟。在这个例子中,我们称这里有2个时钟域。

一个有趣的问题是,这2个时钟域是相互独立的还是有关联的。答案取决于是否有数据路径从1个时钟域开始,到另1个时钟域结束。如果没有这样的路径,我们可以肯定地说这2个时钟域是相互独立的。这意味着,没有时序路径是从1个时钟域开始,到另1个时钟域结束。

如果确实有数据路径跨时钟域(如图2-21所示),必须去确定这条路径是真还是假。例如,真实的路径就是1个有2信速时钟的触发器驱动1个有1信速时钟的触发器。伪路径(False Path)就是设计师将时钟同步器(Clock Synchronizer)逻辑明确地放在2个时钟域之间(做了CDC处理)。在这种情况下,即使有从1个时钟域到另1个时钟域的路径,这也不是真实的时序路径,因为没有约束数据要在1个时钟周期内传播通过同步器逻辑。所以这样的路径被称为伪路径,不是真实路径,因为时钟同步器确保了数据可以正确地从1个时钟域传递到另1个时钟域。可以使用 set_false_path来指定时钟域之间的伪路径,比如:

set_false_path -from [get_clocks USBCLK] -to [get_clocks MEMCLK]

即使没有在图2-21中描述,跨时钟域也可以是双向的,从USBCLK时钟域到MEMCLK时钟域,从MEMCLK时钟域到USBCLK时钟域。在STA中需要理解并处理好这两种情况。

为什么要讨论跨时钟域的路径呢?通常一个设计有大量的时钟,可能有海量的跨时钟域路径。判断哪些跨时钟域路径是真实的,哪些不是,是时序验证重要的一部分。同时可以节约分析时间,这确保了设计师专注于验证真实的时序路径。

10.工作条件

STA通常实在特定的工作条件下进行的。工作条件是由PVT共同定义的。

P: Process 工艺

V: Voltage 电压

T: Temperature 温度

单元延迟和互连延迟是在特定的工作条件下计算的。

下一篇,学习标准单元库的内容。

![Android APP 自动化测试搭建:Appium + Genymotion + [Robot Framework] Open Application](https://img-blog.csdnimg.cn/4929c6c368464a32bb91283b327651eb.png)