名称:Quartus的2FSK调制解调verilog

软件:Quartus

语言:Verilog

要求:使用verilog实现2FSK的调制和解调,并进行仿真

代码下载:Quartus的2FSK调制解调verilog_Verilog/VHDL资源下载

代码网:hdlcode.com

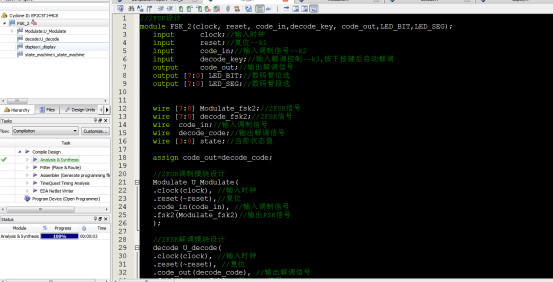

部分代码展示

//2FSK设计 module FSK_2(clock, reset, code_in,decode_key, code_out,LED_BIT,LED_SEG); input clock;//输入时钟 input reset;//复位--k1 input code_in;//输入调制信号--k2 input decode_key;//输入解调控制--k3,按下按键后启动解调 output code_out;//输出解调信号 output [7:0] LED_BIT;//数码管位选 output [7:0] LED_SEG;//数码管段选 wire [7:0] Modulate_fsk2;//2FSK信号 wire [7:0] decode_fsk2;//2FSK信号 wire code_in;//输入调制信号 wire decode_code;//输出解调信号 wire [3:0] state;//当前状态值 assign code_out=decode_code; //2FSK调制模块设计 Modulate U_Modulate( .clock(clock), //输入时钟 .reset(~reset),//复位 .code_in(code_in), //输入调制信号 .fsk2(Modulate_fsk2)//输出FSK信号 ); //2FSK解调模块设计 decode U_decode( .clock(clock), //输入时钟 .reset(~reset), //复位 .code_out(decode_code), //输出解调信号 .fsk2(decode_fsk2)//输入FSK信号 ); //状态机控制,按下decode_key按键后启动解调 state_machine i_state_machine( . clock(clock), . reset(~reset),//复位--k1 . decode_key(decode_key),//输入解调控制--k3 . Modulate_fsk2(Modulate_fsk2),//输入2FSK信号 . decode_fsk2(decode_fsk2),//输出2FSK信号 . state_out(state)//状态值 ); //数码管显示模块 display i_display( . clock(clock),//50M时钟 . code_in(code_in),//输入调制信号 . code_out(decode_code),//输出解调信号 . state(state),//当前状态值 . LED_BIT(LED_BIT),//数码管位选 . LED_SEG(LED_SEG)//数码管段选 );

设计文档(文档点击可下载):

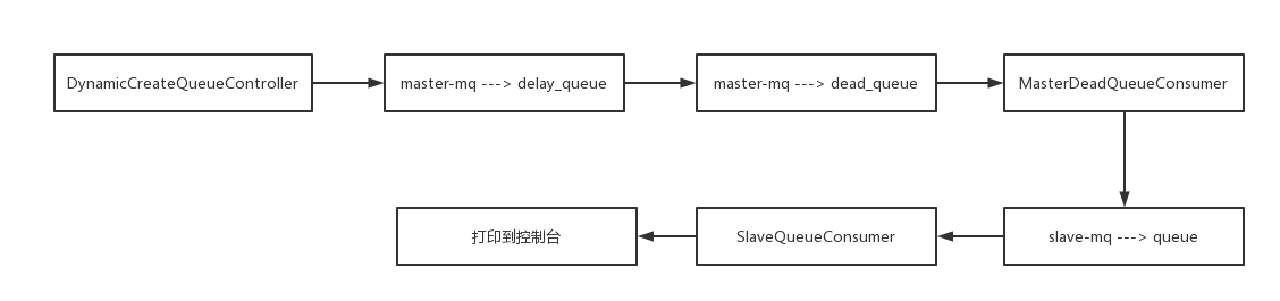

1.

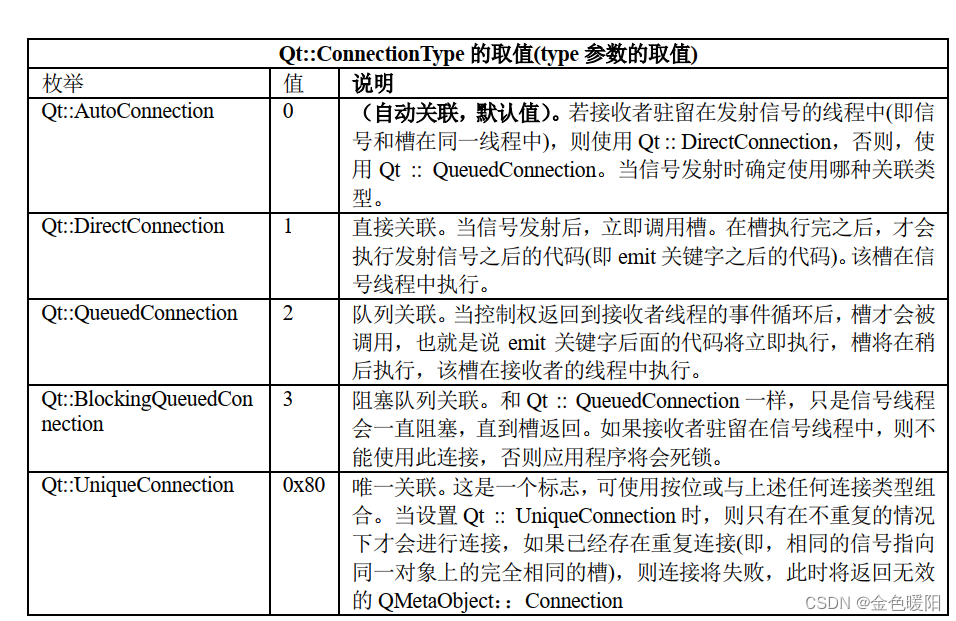

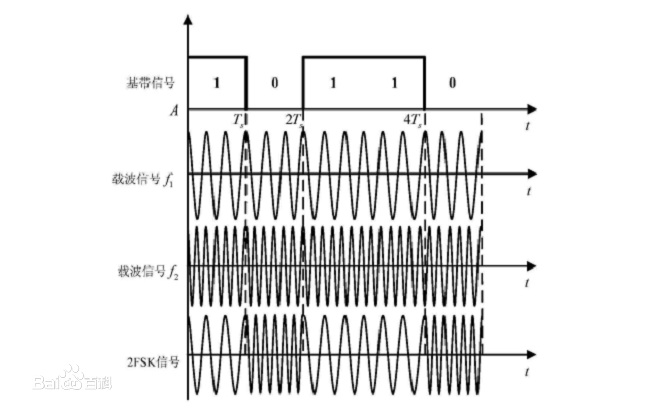

2FSK(Frequency Shift Keying)为二进制数字频率调制(二进制频移键控),用载波的频率来传送数字信息,即用所传送的数字信息控制载波的频率。2FSK信号便是符号“0”对应于载频 f1,而符号“1”对应于载频 f2(与 f1 不同的另一载频)的已调波形,而且 f1 与 f2 之间的改变是瞬间的。传“0”信号时,发送频率为 f1 的载波; 传“1”信号时,发送频率为 f2的载波。

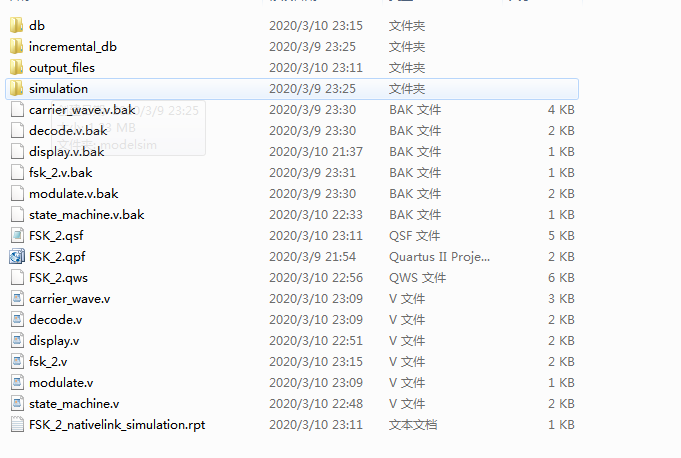

2. 工程文件

3. 程序文件

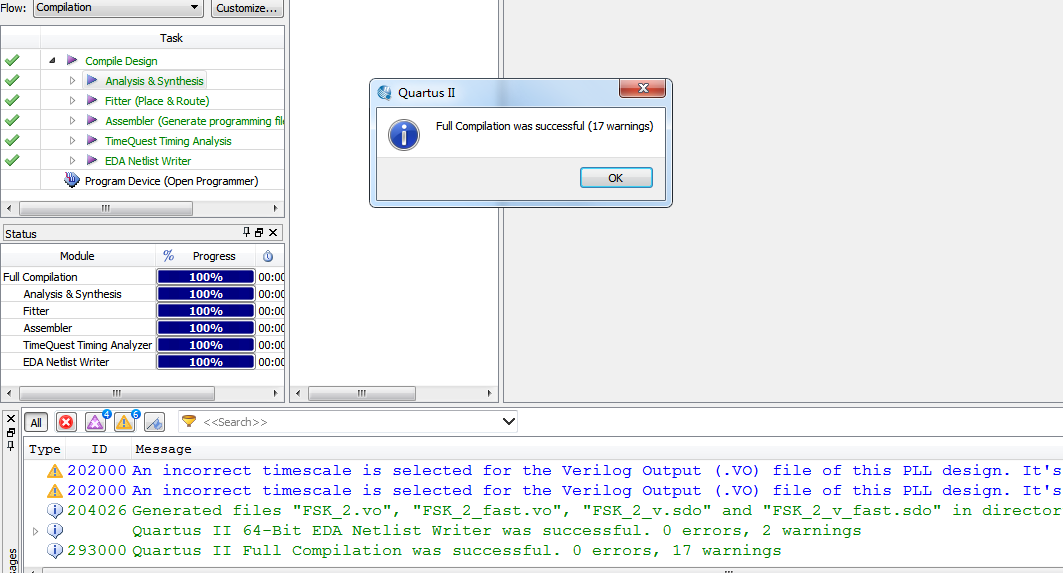

4. 程序编译

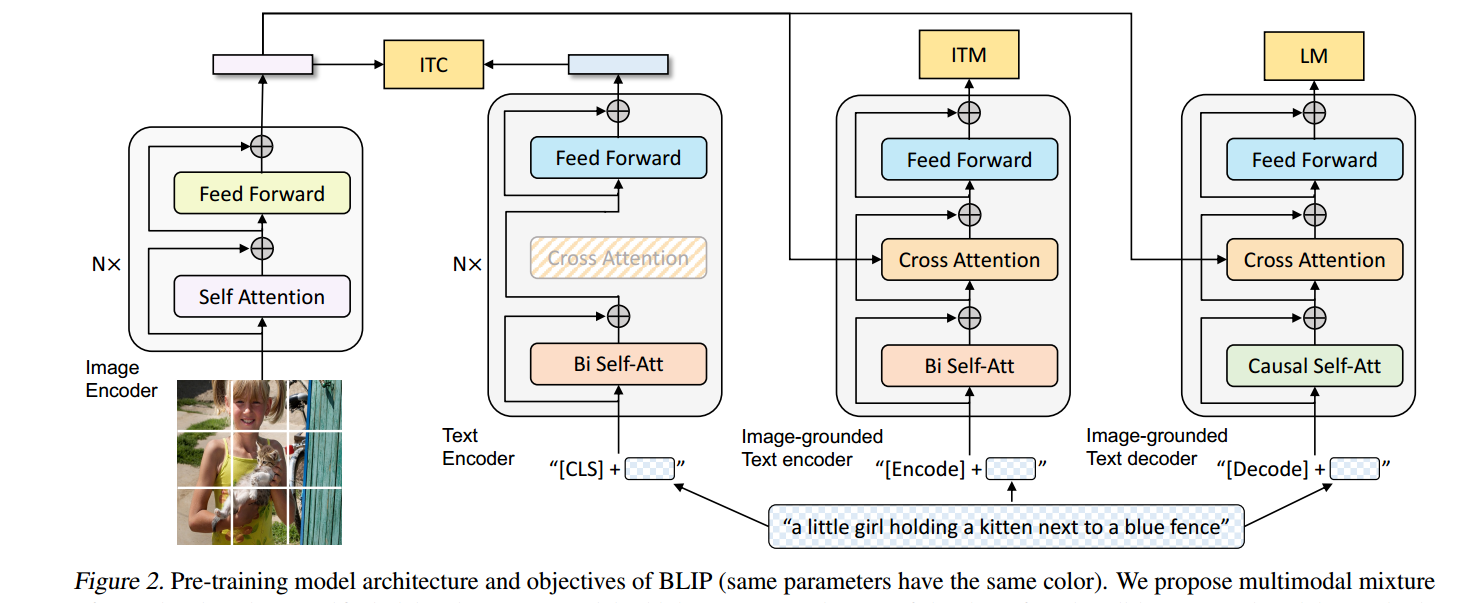

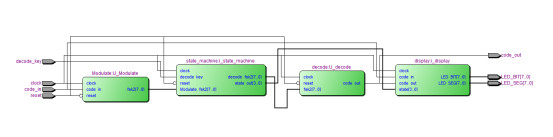

5. RTL图

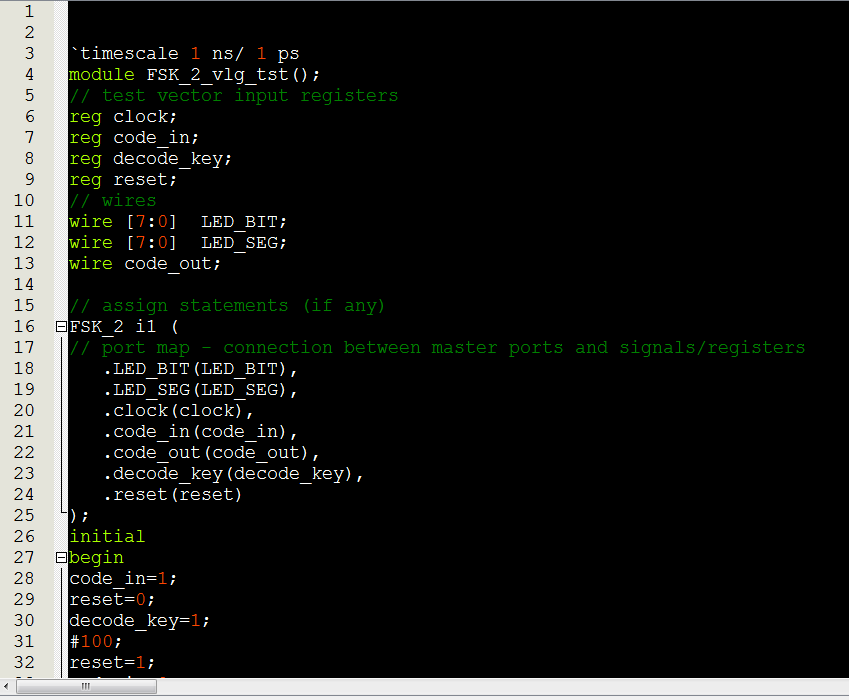

6. testbench

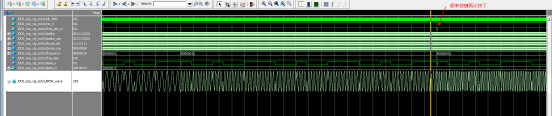

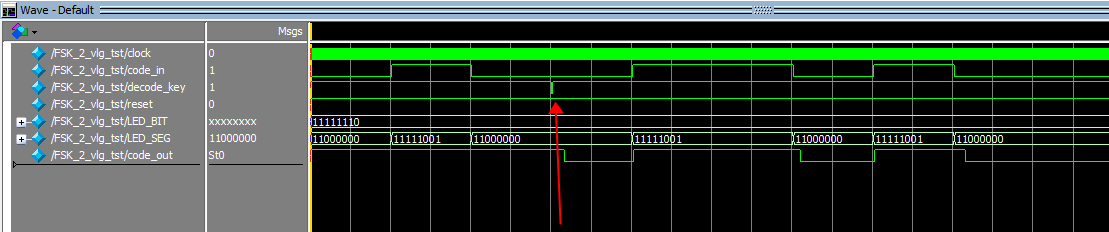

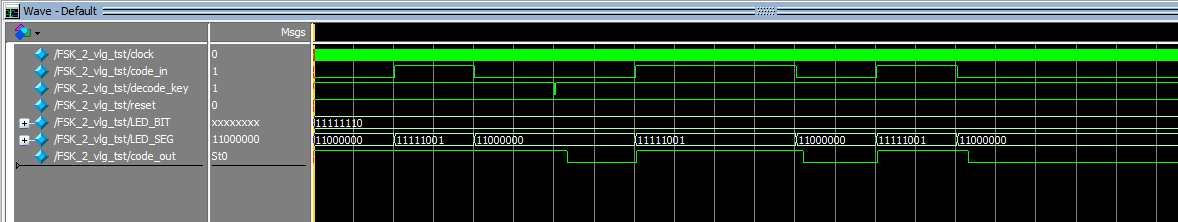

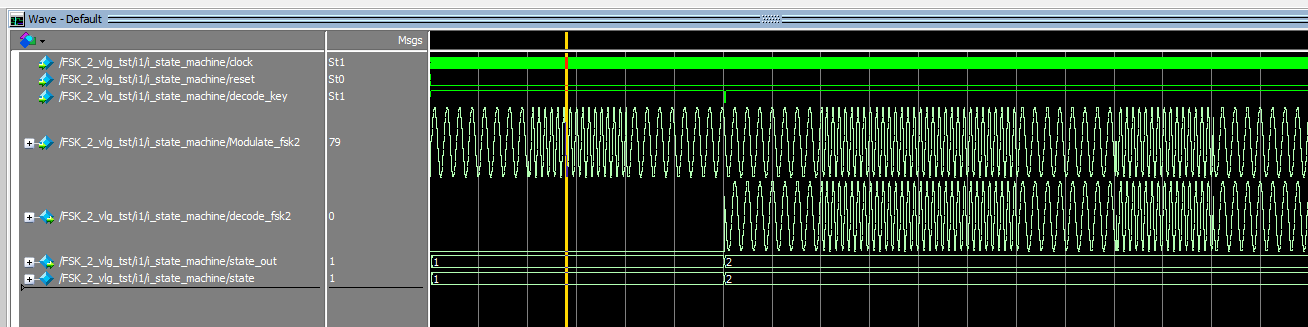

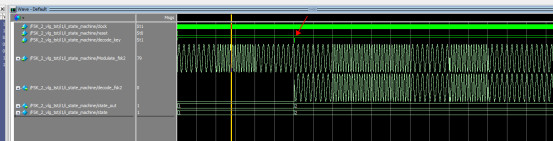

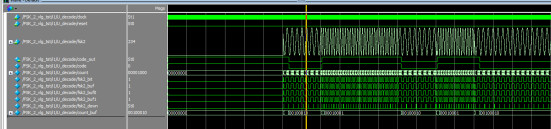

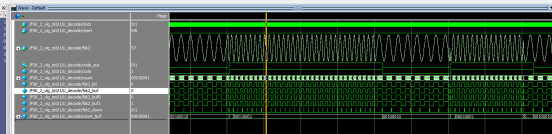

7. 仿真图

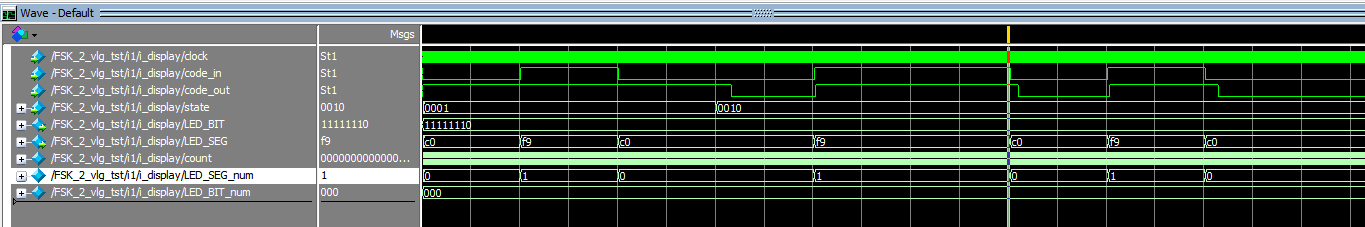

按下按键后启动解调,可以看到解调出的code_out与输入code_in一致

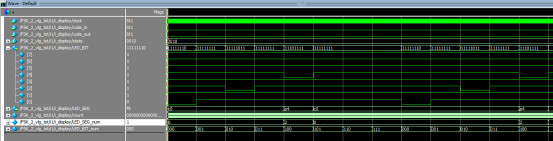

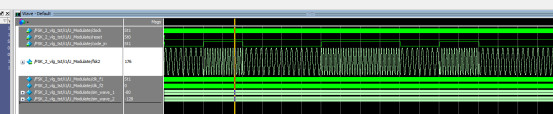

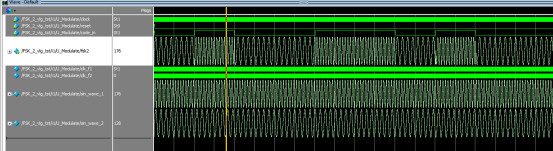

调制模块

状态控制模块

按下按键后启动解调

解调模块

数码管显示模块