用作存储元件的电路

新输入的信号可能使电路保持同样的状态也可能使电路进入另一种新的状态

输入信号置位与复位可以用于改变构成存储元件的电路状态

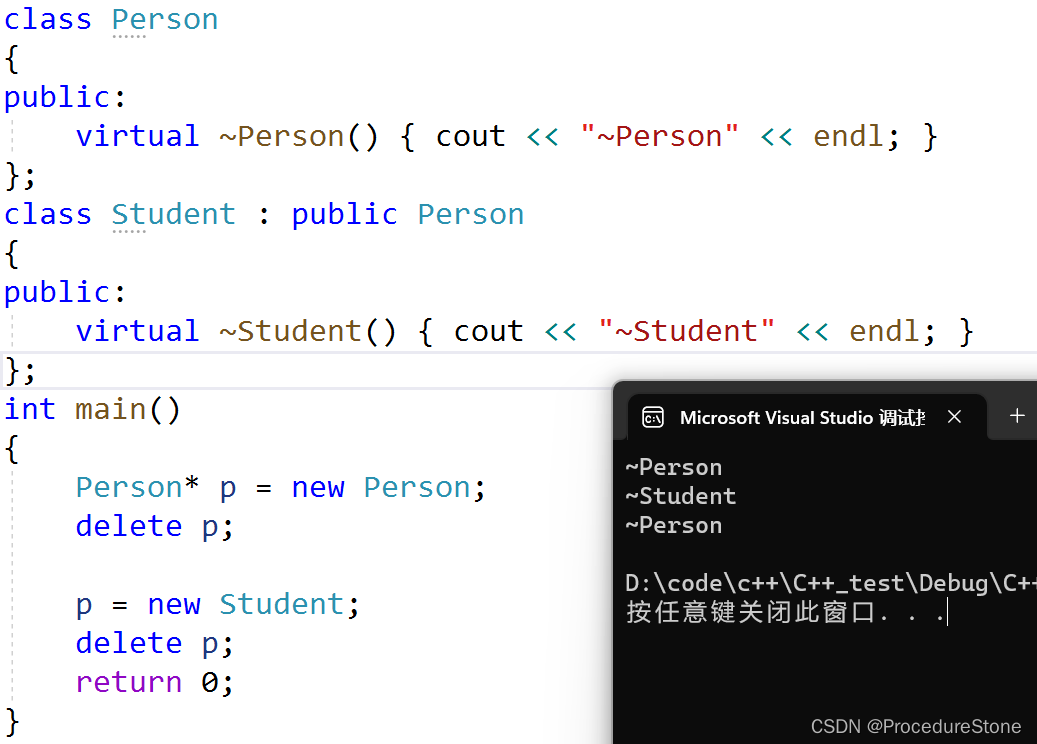

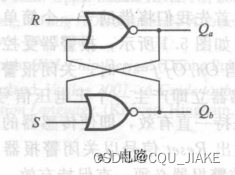

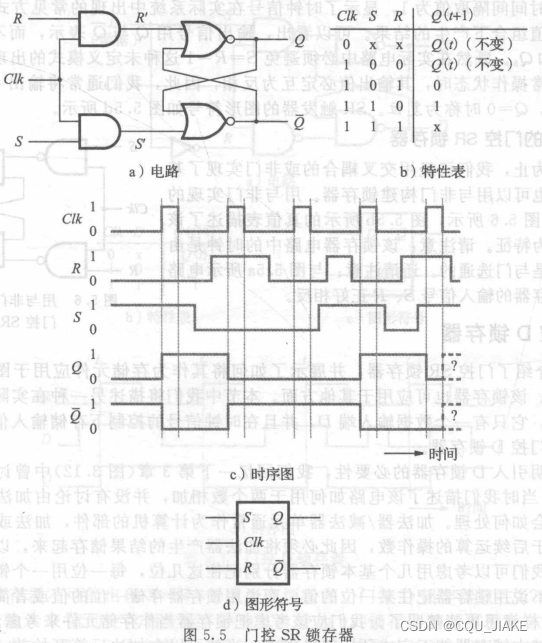

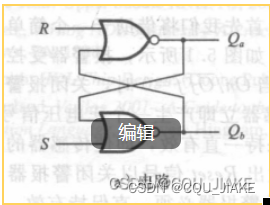

RS锁存器

通过或非门就是说输入信号中有一个是1,输出就的是0

在R=S=0时,RS对或非门的结果无影响,则相当于QA过非门为QB,QB过非门为QA,即QA与QB总是相反。

S=1,R=0先是QB=0,然后复制给R的或非门,产生QA=1,QA再复制给S的或非门,保持QB=0

如果S=1,R=1,先是QB=0,在R的或非门时,QA=0,之后QA再复制给S的或非门,保持QB=0;

如果S=0,R=0,先是QB=1,然后赋值给R的或非门,有QA=0,

如果其中一个为1,就表明一个信号有影响,一个无影响,如果是R为1,那就是R有影响,R要强制QA为0,而S无影响,那就是QA单独作用(取反),即QB=!QA.

如果S为1,就是S有影响,QB被强制为0,而R无影响,QA=!QB

如果RS都为1,就是QAQB都被强制为0,那就是说一旦RS无信号时,QAQB就要不断反转,直到再次相反为止

谁有信号,那段就要被强制置位,类似于按下葫芦浮起瓢的过程,水面上只允许有一个葫芦,按那个就是RS信号,按R就把R葫芦按下去,置位0,则S葫芦浮了上来,为1;按S则S葫芦下去,R葫芦上来;如果两个都按,则都为0,但一旦同时松手就会出问题。如果都不按,就是保持原样。

意思是说,不是所以输出端都是有效输出,只有QA是作为后续电路需要的输出信号,QB就不需要。所谓置位,就是让充作输出的QA作为1,就把S按下,复位就是让作为输出QA为0,即把R按下

(想象记忆是这么想象,但原理不是这个)

其状态的改变总是发生在输入信号改变时。如果不能控制其输入信号的改变时间,则无法知道锁存器什么时候会改变其输出状态。所以时钟信号就是充当了一个使能的作用

只要clk=0,锁存器就会保持其当前状态 。

通常将输出Q=1时称为锁存器置位,Q=0时称为复位。

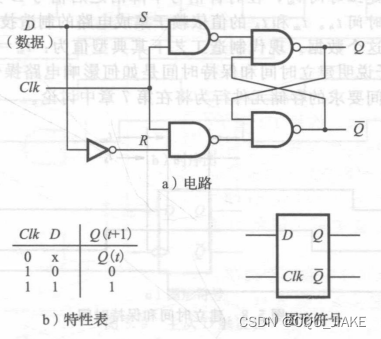

D锁存器

电平敏感

一旦clk变为0,锁存器的状态便被冻结,直到时钟信号再次变为1,输出Q才会变化。因此,在时钟从1变为0时,D锁存器把输入信号D储存起来,即此时输出的Q一直是clk结束时所保存的那个信号

若clk为0,则r,s均出1,那么1对与非门无影响(或非门是0没影响),即保持原样

clk为1时:D为1时,S门出0,Q为1,则R门出1,!Q为0,即D为1则输出1;

D为0时,S输出1,R输出0,则!Q为1,Q为0,即D为0则输出0;

S,R的信号肯定不同,其中为0的信号过与非门后就一定为1,那么另一个出来就一定是0,这是相当于一个强制赋值的过程,而不是从信号里选择的过程。

即通过与非门利好为0的信号,只要有0信号,其输出的信号就是1,也就能保另一个与起来就是1,过非门后就是0

与非门,有一个为0则输出为1,只有都为1才会输出0

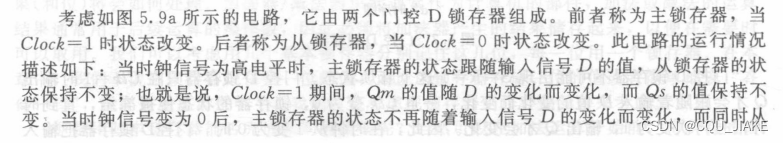

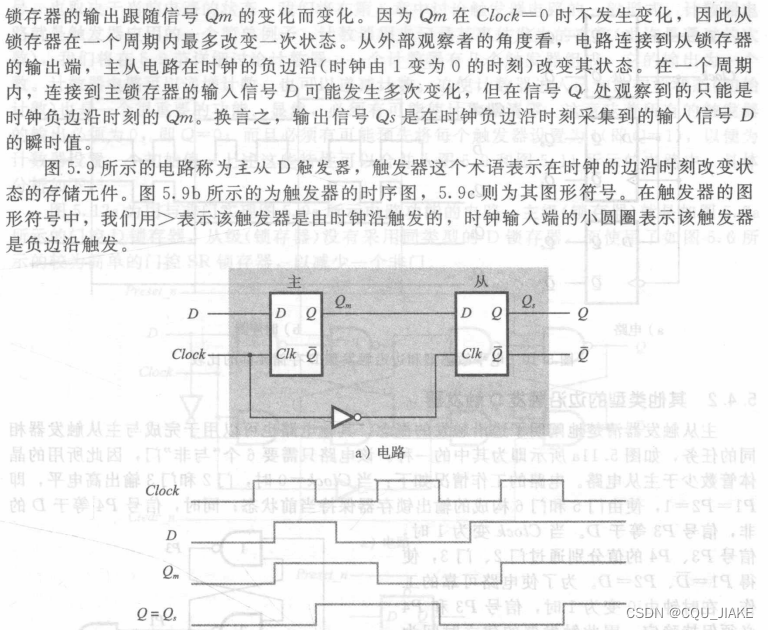

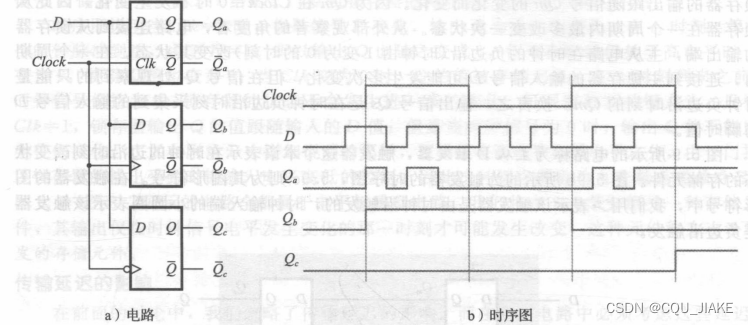

当时钟为0时,从触发器被触发,采集此时的QM信号;

边沿敏感

两个电平敏感组成为边沿敏感

关键在于那个非门的时钟,表示是时钟为0时输出,输出为为0那一刻,即下降沿瞬间的电平信号

如果是要组成上升沿,就是采样只采上升那一瞬间的主锁存器信号,那就要使主锁存器在无时钟信号时激活,在有信号时保持休眠;这样才能在上升沿来临时,使激活的从锁存器输出的是休眠前那一刻主锁存器所锁住的D信号

应该保证的是,主锁存器和从锁存器的电平接收应该是不同的,不然就没有区别。

如果要下降沿,就要让主锁存器在有时钟信号时接收信号电平,然后在时钟结束时,主锁存器锁住此时接收的电平信号,让后让从锁存器激活,输出此时主锁存器所存储的电平信号

这里就是主从锁存器的激活区间是不同的,互补的,即有时钟信号时,主锁存器激活,从锁存器不激活;没有时,从锁存器激活,主锁存器休眠。即主锁存器保留的是对应时间沿之前的D信号,并在时间沿到来之后保存那一刻瞬间的D信号,然后在时间沿之后,从锁存器激活,输出主锁存器所保留的那个瞬间D信号,直到时间沿的再次到来完成更新。

如果D信号不长于时钟周期,即在时钟下降沿结束时,D就为0了,那么Qm就为0,在时钟信号消失,从锁存器激活时,也就为0,起不到在下降沿激发的作用

如果D信号不长于时钟周期,即在时钟下降沿结束时,D就为0了,那么Qm就为0,在时钟信号消失,从锁存器激活时,也就为0,起不到在下降沿激发的作用

锁存器,锁存的不是时钟信号,而是D信号。时钟信号与类型决定锁存的是什么时候的D信号。

当时钟信号为0时,锁存器就开始锁存此时瞬间存储的D信号,直到时钟信号恢复(电平敏感)

即如果是电平敏感,那么在时钟信号内,Q总是输出D的信号;如果是边沿敏感,那么Q就是输出在时钟变化那一刻的D信号,如果是上升沿就是输出上升那一刻的D信号;如果是下降沿,就是下降那一刻的D信号;之后就一直保持输出那一刻的信号,为稳定状态,直到对应的时间沿再次来临,才会进行更新下个沿来临前稳定输出的电平值。

之前的误区是认为只要时间沿来临就会变,实际是错的,只是说时间沿来是发生改变的必要条件,发生改变取决于时钟信号与此刻瞬间的D信号

输出信号Qs是时钟负边沿时刻采集到的输入信号D的瞬时值

边沿锁存器,输出一个周期的稳定信号,输出信号为每个周期初始时瞬间的D信号

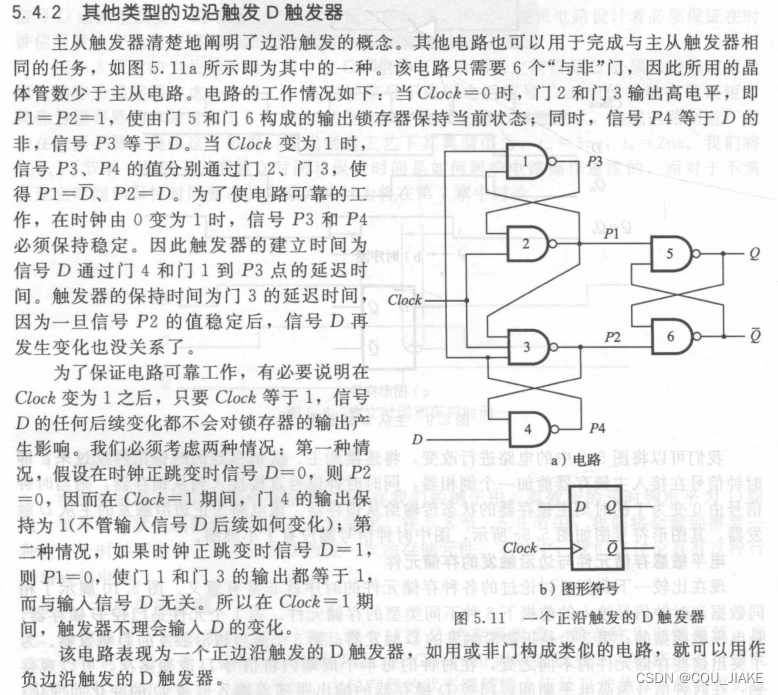

当时钟上升沿来临时,Q必须要输出这刻之前的D信号,那就需要P3,P4(保留之前D信号)保持稳定,即当P3P4把它们保存的前D信息赋给现态后,就无所谓了

?

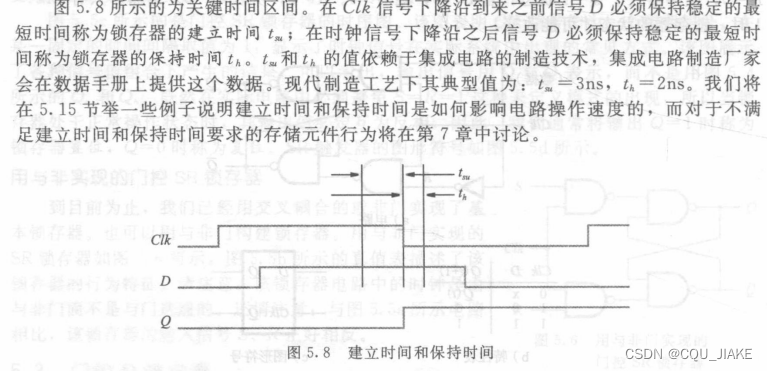

tsu为clk下降沿到来之前信号D必须保持稳定的最短时间,就是说clk下降到来时,实际就已经开始传递信号了,只不过传递的有点慢,就是说,每个时刻接收到的都是前几个时刻的信息,那么在clk下降到来时,就该把此时clk下降的消息和此时d的信号传过去,而至于clk下降之前的d的信号,需要管到多远,就是tsu,就是说锁存器此时接收到的D信号也不是实时的,而是来自之前时刻的D信号,如果之前的时刻没有D信号,那么该时刻就不会有D信号。clk结束后,锁存器需要保存信号

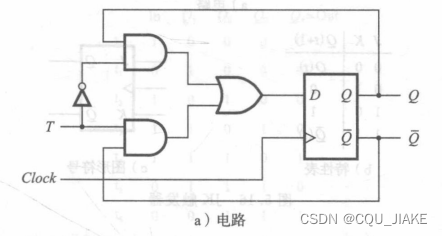

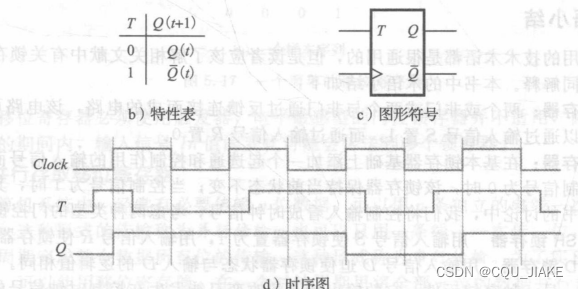

T触发器

右侧为时钟正沿D触发器,每个时钟正沿触发。

T信号后是两个与门,其输入信号分别为Q和Q非,通过T信号对其完成一次选择(即如果T为1,那就不会对与门产生影响,输出原信号,否则就会被与成0),之后两个选择过的信号(一个为没有被影响,一个为被T或T的非与成0的非信号)合并在一起为1个信号(或门,即只保留那个没有被影响的信号),作为D信号给时钟正沿D触发器。

在T为1时,选择的是Q非,那么作为D信号,在时钟上升沿到来时作为次态的Q信号输出,如果T在下个时钟周期还为1,那么就会再选择Q非,使其作为新的Q

在T为0时,选择的是Q,那么作为D信号,在时钟上升沿到来时作为次态的Q信号输出,即保持Q状态不变

即T为1时,就会使得在每个时钟的上升沿时反转一次Q的状态,如果为0就保持。

JK触发器

右边依然是上升沿触发的D触发器

D信号为经过J,K两个信号选择的Q和Q非,J,K相互独立

如果J,K都选择了Q,Q非(即对其过门无影响,J=1,K=0),则经过或门后为1(Q|Q非=1),表示使Q强制置为1

如果只选择了其中一个(即Q,0或Q非,0两种状况),那么就是让那个信号作为新的Q状态

如果都没有选择(0,0),那过或门就是0,表示让Q强制置为0

对电路的理解与再分析

对信号的处理有选择与强制赋值两种情况

其差别在于,选择,反转之类的操作是基于原信号本身的操作,即之后到底是什么信号都是可以由之前是什么的信号得到的,而到底怎么选,怎么操作,就看输入的信号是怎么样的

而强制赋值就是不管之前是什么信号,都被通过计算赋值给算出来,即和之前的Q,Q非没关系,而只与输入的信号是什么有关系

如果有非门,就是强制赋值的情况;有与或门,就是基于原信号的情况(通过选择器)

与或都是二元运算,没有说一个输入进与、或门的

或非门,考虑输入为1,为1时就是强制出0.

与非门,考虑输入为0,为0时就是强制出1.

RS

RS锁存器,是或非门,对于R,S信号,不是从中选择,而是根据其信号进行计算赋值。

二输入或非门就是,如果其中一个是1,那就强制出0,不管另一个是什么;如果一个是0,那就对另一个无影响,就相当于一个非门,如果另一个还是0,那就出1,如果另一个是1,那就出0,即反转另一个信号,

如果输入信号是1,或非后就是0(此时决定出的那个信号(Q或Q非)作为输入信号给另一个赋值时就不会造成影响)。即如果输入信号是1,那么不管传进来的那个信号(要决定的信号)的非信号是什么,最后都会被强制赋值为0。

如果是0,就是让处于此信号的非信号(即输入信号一个是0,一个是传进来的信号,输出的是,那个信号的非信号)的反转一次(即原来是什么则还是什么,比如Q,传进来Q非,反转一次还是Q)。

如果R,S都为0,那就是,两个非门搅合在一起,(还是下面的分析和过程……这里可以是因为存储的信号不同,在变化一次后后续的信号就不变了,而都为1那种相同的情况,就是变化一次后过非门还在同时变,就起不到存储的作用,而是纯粹的01震荡)

如果只有1个为1,那那个为1的或非门出来就是0,就是把那段给强制赋为0,然后另一个为非门,反转,就输出这个0的非,即1.

如果R,S都为1,那么两个输出都是0(都强制赋为0),虽然在有信号时可以保持,但一旦失去信号时,就相当于下图,出大问题,QA反转一次后一份给QB,然后一份再反转一次,再反转一次后一份给QA,一份再反转一次……即两个非门连在一起就不断地反转了,永不停歇的震荡。

这点到了,但没到点子上,之所以不行是因为要反转,两个信号从00变到11,又从11变到00,即不能保持一个稳定的信号,而是处于不断变化震荡的状态,不能确定之后两个信号到底是什么状态

不行是因为此时两端的信号是相同的(即电路不是说固定一段去运行,而是QAQB同时输进去,如果不同,就可以自洽的运行(我把你变成和我相反的,你把我变成和你相反的,即我们两个本就不同,不管怎么变,变几次,我们都是不同的,而且保持自己的状态),保持存储,如果相同,就是你把我变成和你相反的同时我又把你变成和我相反的,那么我们都是之前相反的,而且还相同,那么之后又是重复这个过程(直到一个累了,慢了,就确定了一种状态,否则只要电路同步,就不会停止过程),如果不同就不会不行,就是正常的存储,正常的存储就是要让电路不断的运行下去

即这种

即这种

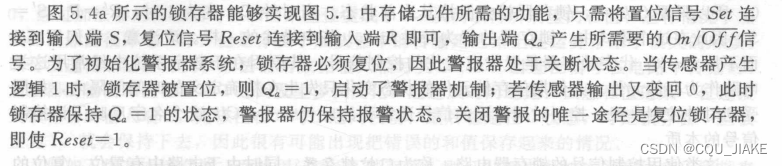

而这种电路的分析,如果Set置位信号为1,那么或非后强制为0,再过或非(R为0),就会出1,即置电路为1,之后这个电路就是1(S,R都为0,即上图的那个记忆元件,记忆了1,并不断把这个1在圈里来回踢)

而这种电路的分析,如果Set置位信号为1,那么或非后强制为0,再过或非(R为0),就会出1,即置电路为1,之后这个电路就是1(S,R都为0,即上图的那个记忆元件,记忆了1,并不断把这个1在圈里来回踢)

即只有一个信号为1时,记忆1;

两个都为1时,记忆0,或者可以说是复位;

两个都为0时,就保持之前记的,该转啥转啥。

D

后面是一个与非门,

后面是一个与非门,

与非门,如果有0,就会强制出1;如果有1,就是非门,反转这个信号的非信号,即保持原信号

二元门,信号确定为1时,与门失去作用,确定为0时,或门失去作用

前面clk与R,S的与非门,相当于使能端和输入信号的综合。

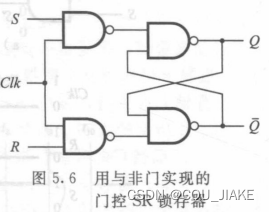

用与非门

当没有时钟信号时,与非出来 的两个信号都为1,那么对与非门没影响,就是两个非门,即保持电路原状态并起到存储作用

都为0时,则与非出来都是1, 起到储存作用

只有1个时,那么那个为0的信号过与非门就是1,1的信号出来是0,其再过与非门出强制出1,即强制给为1的那个信号赋值为1

都为1时,一旦时钟信号消失,就会使电路处于震荡状态

关于verilog中reg

[6:0]的wire信号表示,输入时来了6个信号,这六个信号相互独立,从六根线来

如果输出[6:0]的wire类型,就表示输出也是6个信号,即伸出去6根线,相互独立

而如果输出为reg型,就表示输出一个信号,这个信号是6位的,即一个变化的电平波,只有一根线出去(常用于序列或编码的输出)