目录

0. 参考文档

1.嵌入式网络接口简介

2.嵌入式网络硬件架构方案

2.1 SOC内未集成MAC芯片

2.2 SOC内集成MAC芯片

2.3 主流方案总结

2.3 参照实际网卡的说明

3.MII/RMII及MDIO接口

3.1 MII

3.2 RMII

3.3 MDIO

0. 参考文档

网卡构造:MAC与PHY的关系,GMAC介绍_学海无涯_come on的博客-CSDN博客对于上述三部分,并不一定都是独立的芯片,主要有以下几种情况CPU内部集成了MAC和PHY (难度较高)CPU内部集成MAC,PHY采用独立芯片 (主流方案)CPU不集成MAC和PHY,MAC和PHY采用独立芯片或者集成芯片 (高端采用)在软件上对网口的操作通常分为下面几步:为数据收发分配内存;初始化MAC寄存器;初始化PHY寄存器(通过MIIM);启动收发;_gmachttps://blog.csdn.net/chenhuanqiangnihao/article/details/128287341

【genius_platform软件平台开发】第九十八讲:嵌入式网络接口(MAC、PHY)_隨意的風的博客-CSDN博客15这16个寄存器的功能,16~31这16个寄存器由厂商自行实现。也就是说不管你用的哪个厂家的PHY芯片,其中0~15这16个寄存器是一模一样的。仅靠这16个寄存器是完全可以驱动起PHY芯片的,至少能保证基本的网络数据通信,因此Linux内核有通用PHY驱动,按道理来讲,不管你使用的哪个厂家的PHY芯片,都可以使用Linux的这个通用PHY驱动来验证网络工作是否正常。事实上在实际开发中可能会遇到一些其他的问题导致Linux内核的通用PHY驱动工作不正常,这个时候就需要驱动开发人员去调试了。https://blog.csdn.net/Windgs_YF/article/details/131262026

PHY芯片快速深度理解(持续更新中……)_daisy.skye的博客-CSDN博客物理层芯片称为PHY、数据链路层芯片称为MAC。可以看到PHY的数据是RJ45网络接口(网线口)穿过了的差分信号,而PHY作用就是将差分信号转为数字信号,这块内容不用深究,制造商都设计好了。那我们干什么呢?(主要是对phy芯片进行模式选择,比如工作速率,工作模式)为什么要熟悉RJ45网口上面说到针对phy芯片我们只要进行模式选择(下文会介绍使用mdio接口,通过寄存器控制)那模式选择后,如何查看是否有效呢?最简单直接的就是通过RJ45网口的指示灯查看。_phy芯片https://blog.csdn.net/qq_40715266/article/details/124095801

1.嵌入式网络接口简介

提起网络,我们一般想到的是“以太网卡”。网卡硬件分为两部分:1)数据链路层的MAC芯片;2)物理层的PHY芯片。

MAC位于OSI七层协议中数据链路层的下半部分,主要负责控制与连接物理层的物理介质。MAC在发送数据的时候,MAC事先判断是否可以发送数据,如果可以,给数据加上一些控制信息,再将数据以及控制信息以规定的格式封装成帧发送到物理层;在接收数据的时候,MAC只接收发送至本网卡的单播帧、组播帧和广播帧,其余的丢弃,再将帧重新组合成数据,并判断输入的数据并是否发生传输错误,如果没有错误,则去掉控制信息发送至LLC层。

PHY位于OSI七层协议中的物理层。PHY在发送数据的时候,收到MAC过来的数据,然后把并行数据转化为串行流数据,按照物理层的编码规则把数据编码,再变为模拟信号把数据送出去,收数据时的流程反之。

2.嵌入式网络硬件架构方案

大家都是通过看数据手册来判断一款SOC是否支持网络,如果一款芯片数据手册说自己支持网络,一般都是说的这款SOC内置MAC,MAC类似I2C控制器、SPI控制器一样的外设。

但是光有MAC还不能直接驱动网络,还需要另外一个芯片:PHY,因此对于内置MAC的SOC,其外部必须搭配一个PHY芯片。内部没有MAC的SOC芯片,就需要使用外置的MAC+PHY一体芯片了,这里就要牵扯出常见的两个嵌入式网络硬件方案了。

2.1 SOC内未集成MAC芯片

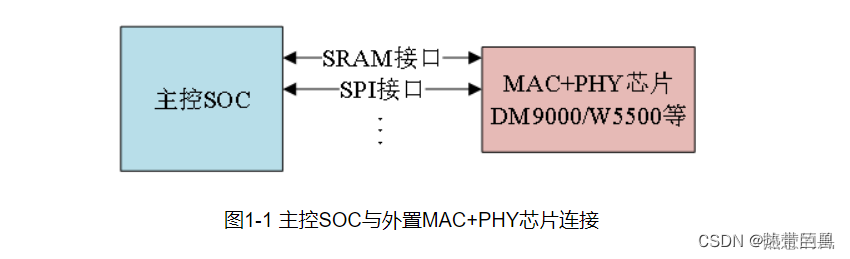

对于内部没有MAC的SOC芯片,可以使用外置 MAC+PHY一体的网络芯片来实现网络功能。比如三星linux开发板里面用的最多的DM9000,DM9000对SOC提供了一个SRAM接口,SOC会以SRAM的方式操作DM9000。

有些外置的网络芯片更强大,内部甚至集成了硬件TCP/IP协议栈,对外提供一个SPI接口,比如W5500。SOC通过SPI接口与W5500进行通信,由于W5500内置了硬件TCP/IP协议栈,因此SOC就不需要移植软件协议栈,直接通过SPI来操作W5500,简化了单片机联网方案。

这种方案的优点就是让不支持网络的SOC能够另辟蹊径,实现网络功能,但是缺点就是网络效率不高,因为一般芯片内置的MAC会有网络加速引擎,比如网络专用DMA,网络处理效率会很高。而且此类外置芯片网速都不快,基本就是10/100M。另外,相比PHY芯片而言,此类芯片的成本也比较高,可选择比较少。

SOC与外部MAC+PHY芯片的连接如下图所示:

2.2 SOC内集成MAC芯片

我们一般说某个SOC支持网络,说的就是他内部集成网络MAC外设,此时我们还需要外接一个网络PHY芯片。目前几乎所有支持网络的SOC都是内置MAC外设,比如STM32F4/F7/H7系列、NXP的I.MX系列,内部集成网络MAC的优点如下:

1)内部MAC外设会有专用的加速模块,比如专用的DMA,加速网速数据的处理。

2)网速快,可以支持10/100/1000M网速。

3)外接PHY可选择性多,成本低。

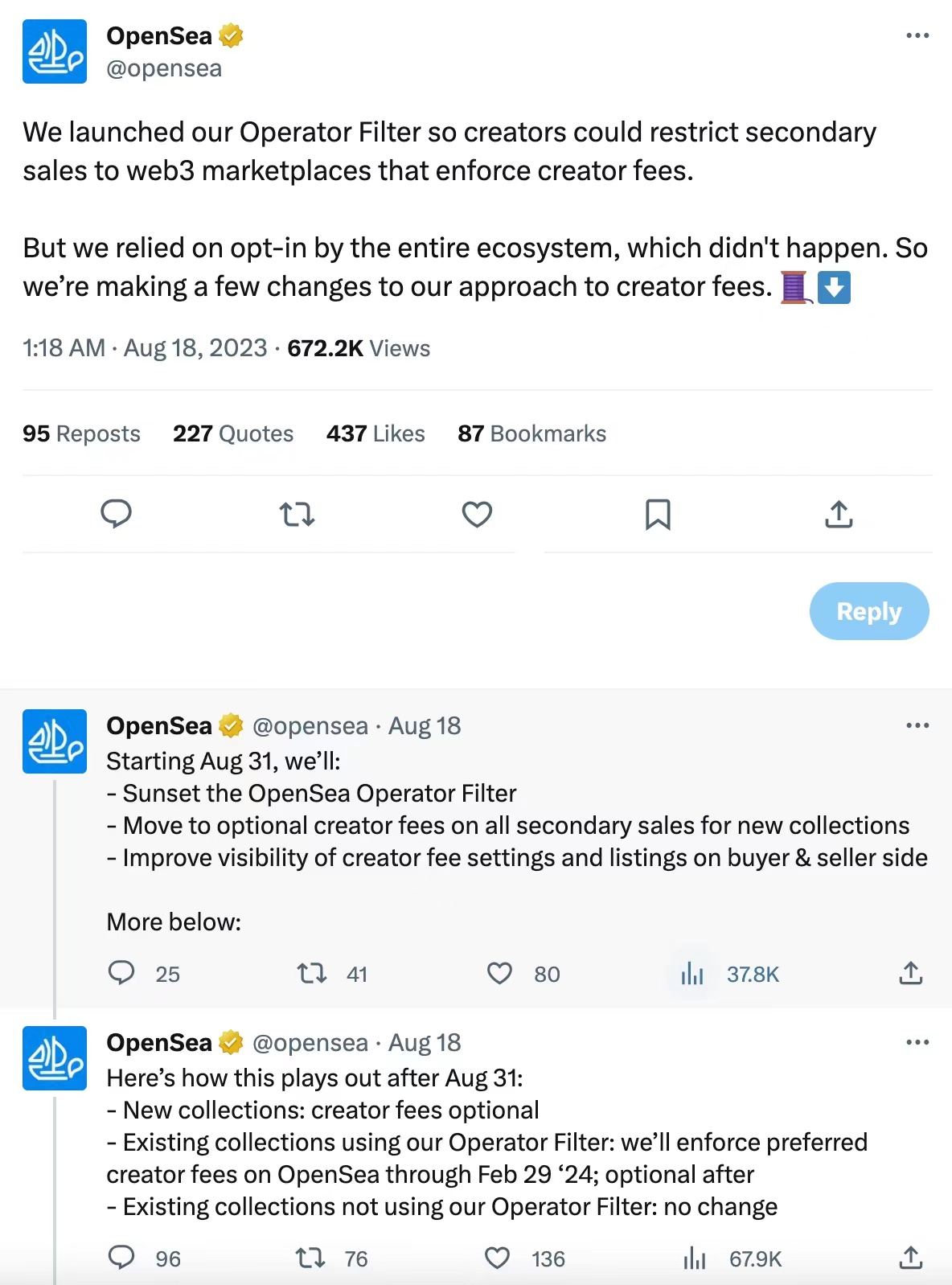

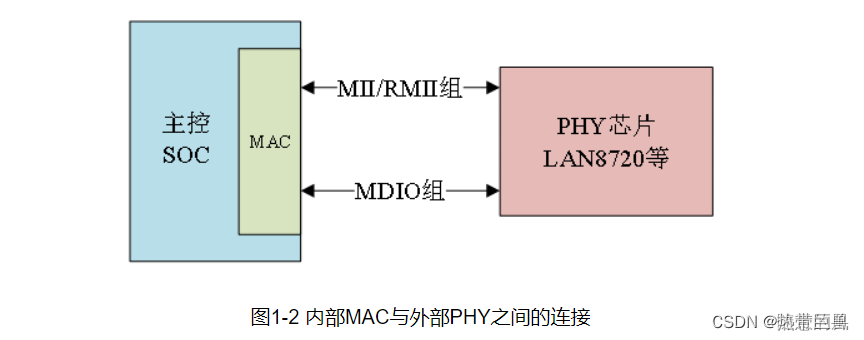

内部的MAC外设会通过MII或者RMII接口来连接外部的PHY芯片,MII/RMII接口用来传输网络数据。另外主控需要配置或读取PHY芯片,也就是读写PHY的内部寄存器,所以还需要一个控制接口,叫做MIDO(也叫作SMI),MDIO很类似IIC,也是两根线,一根数据线叫做MDIO,一根时钟线叫做MDC。SOC内部MAC外设与外部PHY芯片的连接如下图所示:

2.3 主流方案总结

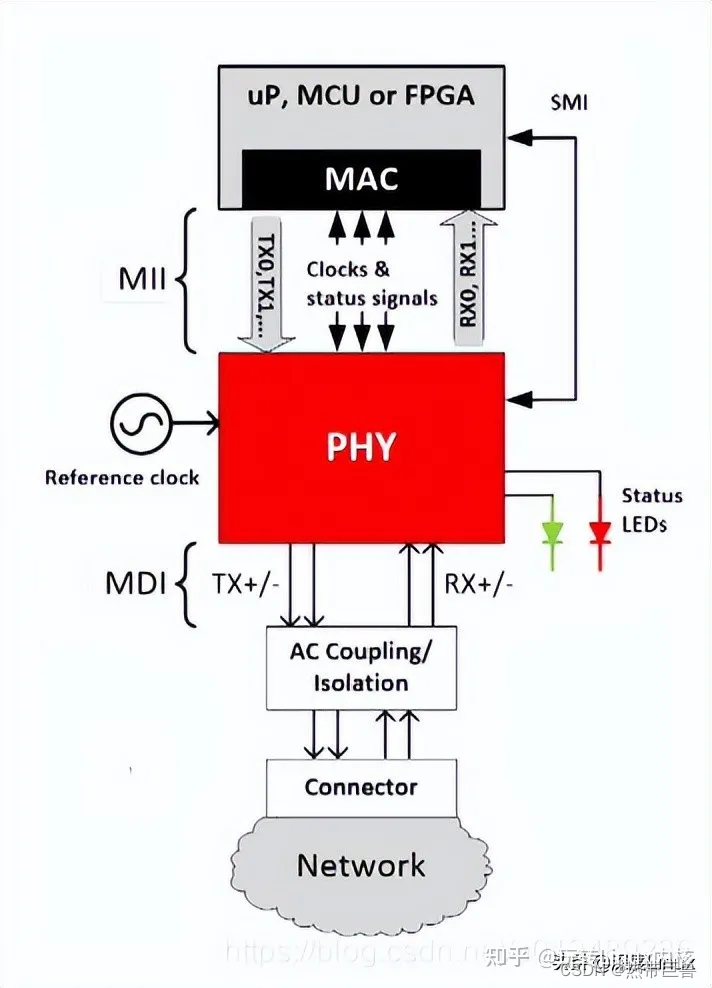

由于PHY包含大量模拟器件,而MAC是典型的数字电路,考虑到芯片面积及模拟/数字混合架构的原因,将MAC集成进SOC,PHY留在片外,这种结构是最常见的。

其中,MAC与PHY之间有两个重要的接口:1)MII总线接口,主要完成数据收发相关业务;2)MDIO总线接口(也叫作SMI),主要完成SOC对PHY芯片各寄存器的配置。

当PHY芯片发送数据时,接受MAC芯片从MII接口发送过来的数字信号,然后转换成模拟信号,通过MDI接口传输出去。

网络设备是通过网线连接起来的,插入网线的地方叫做RJ45座(见下图上),RJ45座要与PHY芯片连接在一起,但是中间还需要一个网络变压器(见下图下),其主要作用是1)增强信号。网线传输的距离很长,有时候需要送到100米甚至更远的地址,那么就会导致信号的流失,需要提前增强信号;2)隔离外部设备,增强芯片抗干扰能力。网线与内部芯片直接相连的话,电磁感应和静电也很容易导致芯片的损坏。所以就要使用网络变压器连接RJ45座。

同时,PHY芯片会引出两个引脚,连接到RJ45座的LED灯上,对LED灯进行控制,用来指示当前网络通信状态。RJ45 座子上一般有两个灯,一个橙色,一个绿色,绿色亮表示网络连接正常,黄色闪烁说明当前正在进行网络通信,黄灯闪动频率越快表示网速越好。

2.3 参照实际网卡的说明

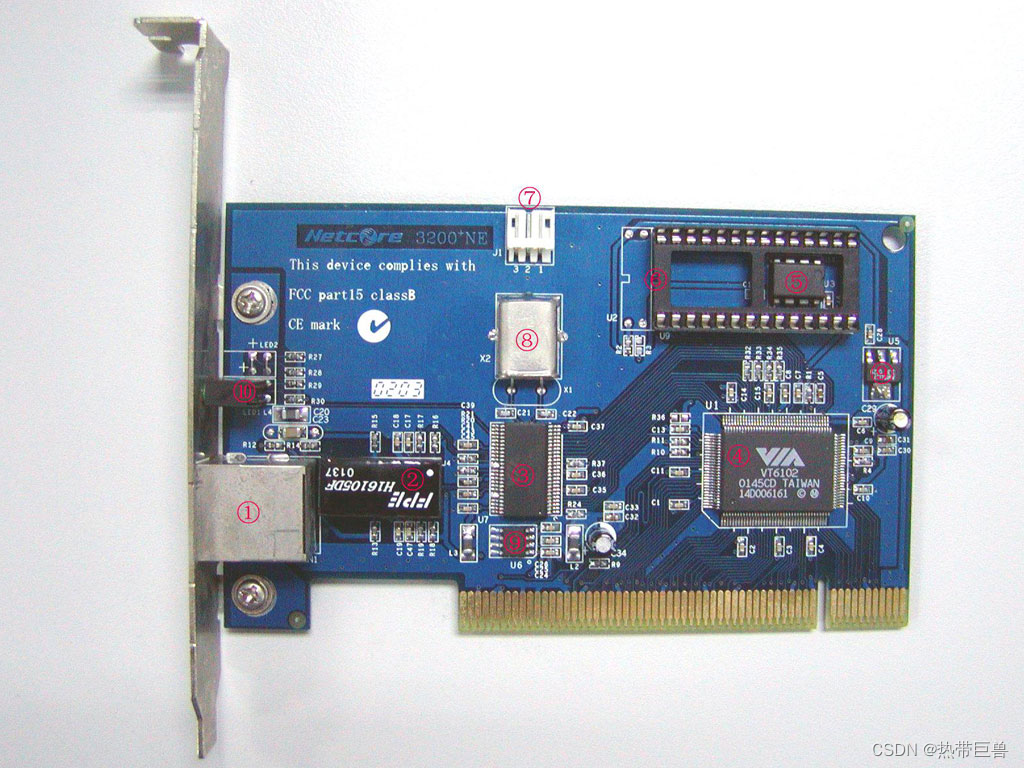

MAC和PHY分开的以太网卡 :

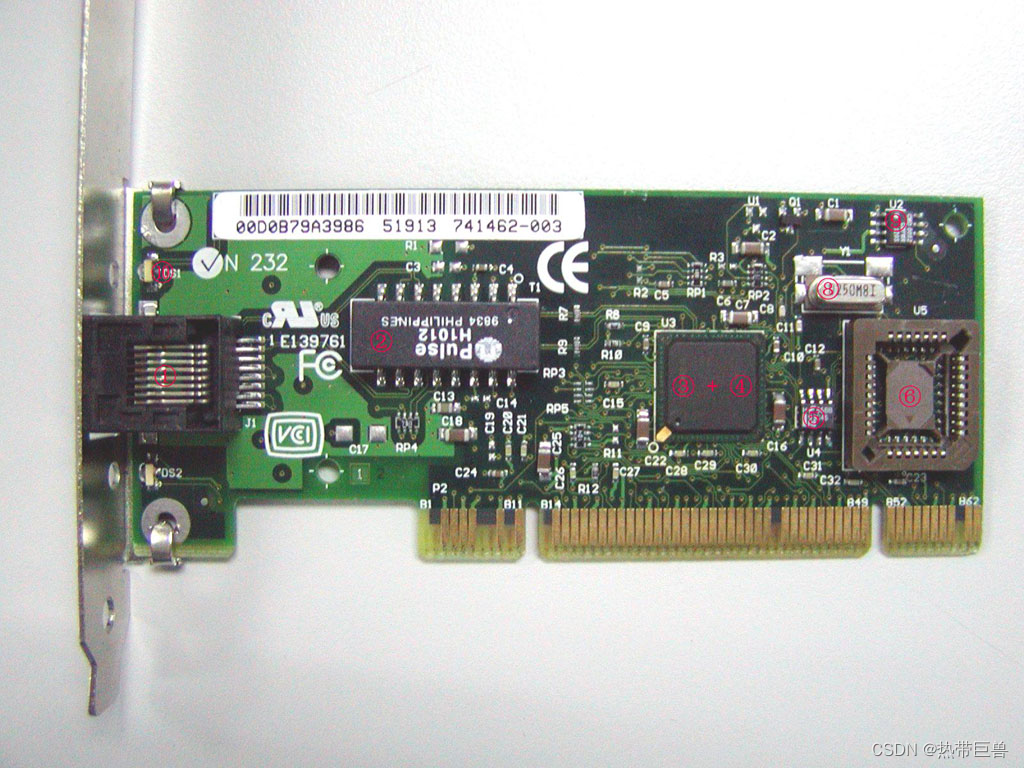

MAC和PHY集成在一个芯片的网卡:

上图中各部件为:①RJ-45接口、②Transformer(隔离变压器)、③PHY芯片、④MAC芯片、⑤EEPROM、⑥BOOTROM插槽、⑦WOL接头、⑧晶振、⑨电压转换芯片、⑩LED指示灯。

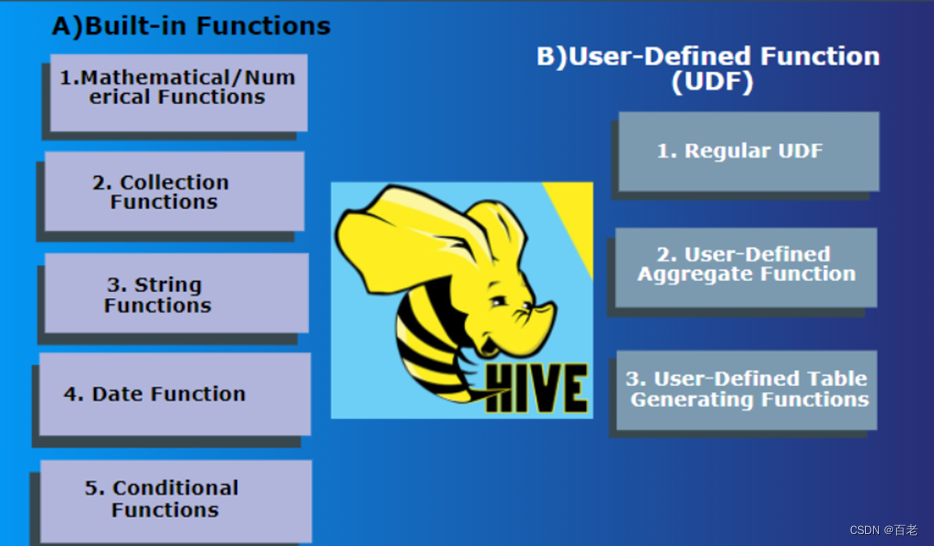

3.MII/RMII及MDIO接口

MAC与PHY接口支持四种类型:MII、RMII、GMII、RGMII。这四种类型都是从MII(Media Independent Interface)衍生出来的,RMII(Reduced MII)是精简版的MII,GMII(Gigabit MII)是支持千兆传输速率的MII,RGMII(Reduced GMII)是精简版的GMII。下面主要介绍MII和RMII。

3.1 MII

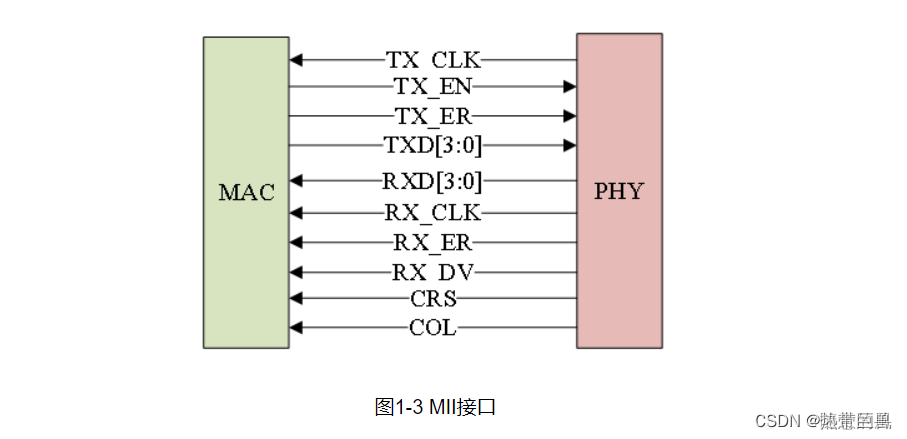

MII全称是Media Independent Interface,直译过来就是介质独立接口,它是IEEE-802.3定义的以太网标准接口,MII接口用于以太网MAC连接PHY芯片,连接示意图如下图所示:

MII接口一共有16根信号线,含义如下:

- TX_CLK:发送时钟,如果网速为100M的话时钟频率为25MHz,10M网速的话时钟频率为2.5MHz,此时钟由PHY产生并发送给MAC。

- TX_EN:发送使能信号。

- TX_ER:发送错误信号,高电平有效,表示TX_ER有效期内传输的数据无效。10Mpbs网速下TX_ER不起作用。

- TXD[3:0]:发送数据信号线,一共4根。

- RXD[3:0]:接收数据信号线,一共4根。

- RX_CLK:接收时钟信号,如果网速为100M的话时钟频率为25MHz,10M网速的话时钟频率为2.5MHz,RX_CLK也是由PHY产生的。

- RX_ER:接收错误信号,高电平有效,表示RX_ER有效期内传输的数据无效。10Mpbs网速下RX_ER不起作用。

- RX_DV:接收数据有效,作用类似TX_EN。

- CRS:载波侦听信号。

- COL:冲突检测信号。

MII接口的缺点就是所需信号线太多,这还没有算MDIO和MDC这两根管理接口的数据线,因此MII接口使用已经越来越少了。

3.2 RMII

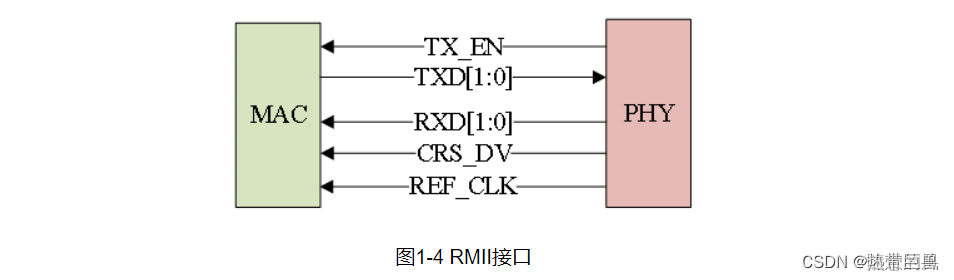

RMII全称是Reduced Media Independent Interface,翻译过来就是精简的介质独立接口,也就是MII接口的精简版本。RMII接口只需要7根数据线,相比MII直接减少了9根,极大的方便了板子布线,RMII接口连接PHY芯片的示意图如下图所示:

- TX_EN:发送使能信号。

- TXD[1:0]:发送数据信号线,一共2根。

- RXD[1:0]:接收数据信号线,一共2根。

- CRS_DV:相当于MII接口中的RX_DV和CRS这两个信号的混合。

- REF_CLK:参考时钟,由外部时钟源提供, 频率为50MHz。这里与MII不同,MII的接收和发送时钟是独立分开的,而且都是由PHY芯片提供的。

3.3 MDIO

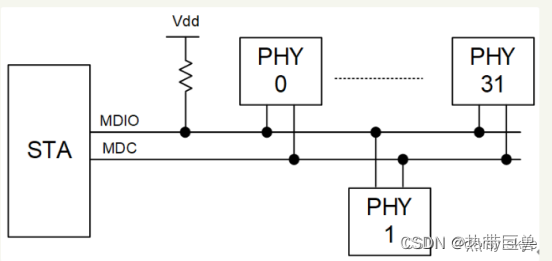

MDIO接口(也叫作SMI接口),全称是Management Data Input/Output,直译过来就是管理数据输入输出接口,是一个简单的两线串行接口,包括一根MDIO数据线和一根MDC时钟线。驱动程序可以通过MDIO和MDC这两根线访问任意PHY芯片的任意一个寄存器,总线框图如下图所示。

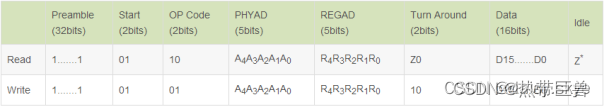

MDIO的读写时序如下图所示,其含义是读/写某一PHY芯片(由PHYAD字段指定)中的某一寄存器(由REGAD字段指定):

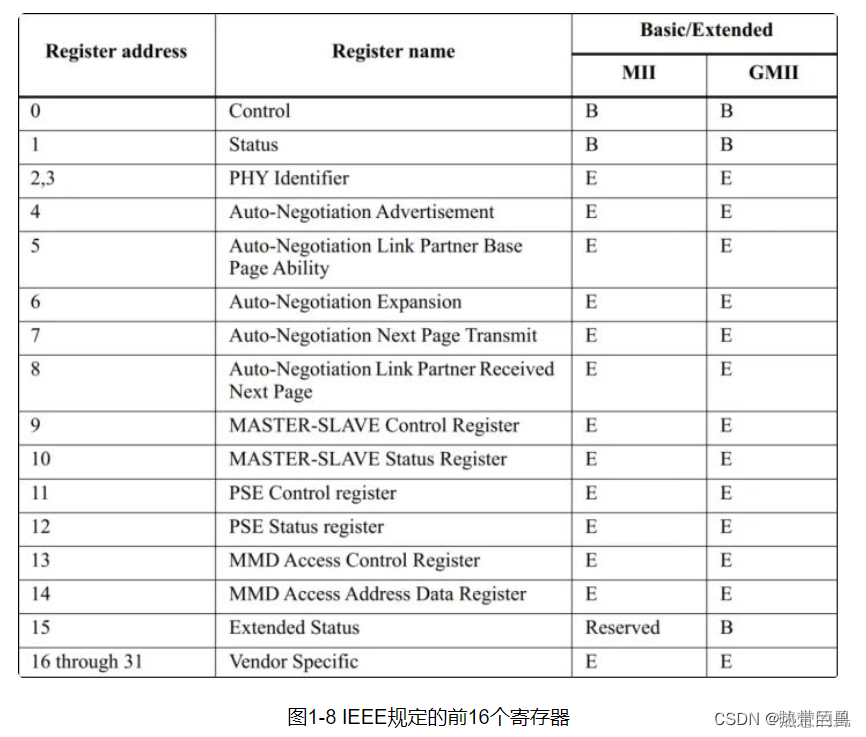

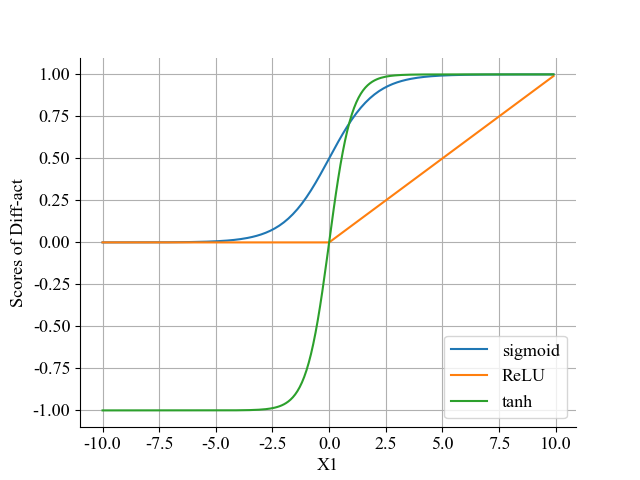

从上表可知,MDIO可读写的PHY地址(即图中的PHYAD字段)为5位,所以一个SOC最多管理2^5=32个PHY芯片(与MDIO总线框图相呼应)。MDIO可访问该PHY芯片(由PHYAD指定)中的寄存器地址(即图中的REGAD字段)也为5位,所以一个PHY芯片中最多有32个寄存器,其中寄存器0-15这16个寄存器各个公司都是一样的,后面16个寄存器则由不同厂家各自定义。

IEEE802.3协议英文原版中的 “22.2.4 Management functions”章节对PHY的前16个寄存器功能进行了规定,如下图所示: