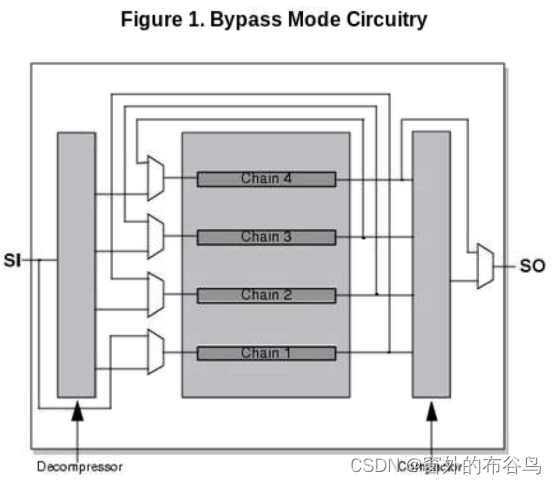

默认,EDT逻辑中包含bypass逻辑,bypass电路可以bypass EDT逻辑,访问设计core中未压缩的扫描链。

bypass EDT逻辑可以应用未压缩test patterns到设计中

- Debug 压缩test patterns。

- 应用附加自定义未压缩扫描链。

- 应用来自其他ATPG工具的test patterns。

在扫描插入时,bypass可以被插入到core网表中。使能放置MUX和lockup cell以操作core网表中的bypass mode而不是EDT逻辑。该option支持更加有效的设计布线。

Structure of the Bypass Logic

因为扫描链的数量很多,bypass mode将它们配置成更少,更长的扫描链。例如,在设计中有100个core扫描链和四个外部channel,每25个扫描链被连接形成一个bypass链,该bypass链连接到给定channel的input和output。

bypass逻辑使用MUX实现,工具包括MUX和lockup cells以连接EDT逻辑中的扫描链。

Generating EDT Logic When Bypass Logic Is Defined in the Netlist

EDT技术支持网表包括两组pre-defined扫描链,预定义的两组扫描链使能在core设计中插入bypass chains和core