DDR3硬件电路设计

- 1 简介

- 2 电路设计

- 3 设计要点

1 简介

RAM(Random Access Memory)是随机存储器,存储单元中的内容可以按需任意去除或者存入,并且存取的速度与存储单元的位置无关。这种存储器在断电时,将丢失其存储的内容,一般用于存储短时间使用的程序。按照存储的信息不同可以分为静态存储器(Static RAM,SRAM)和和动态存储器(Dynamic RAM,DRAM)。

| 存储器 | 描述 |

|---|---|

| 静态存储器 | 不需要刷新电路即能保存它内部存储的数据。 |

| 动态存储器 | 每隔一段时间,要刷新充电一次,否则将会丢失内部的数据。 |

特别地,SDRAM(Synchronous DRAM)是同步动态随机存储器,指Memory工作需要同步时钟,内部的命令的发送与数据的传输都以它为基准(其总线工作在同步时许的方式下,总线时钟 以CPU时钟频率为基准)。随机是指数据不是线性依次存储,而是自由指定地址进行数据读写。动态是指存储阵列需要不断的刷新老保证数据不丢失。DDR(X)就是SDRAM。

随着技术的发展,DDR的电压不断下降。同时对于低功耗的设计难度越来越大,抗干扰性的难度也逐步增加。

| 存储器 | 电源电压 |

|---|---|

| DDR1 | 2.5V |

| DDR2 | 1.8V |

| DDR3 | 1.5V |

| DDR4 | 1.2V |

| DDR5 | 1.1V |

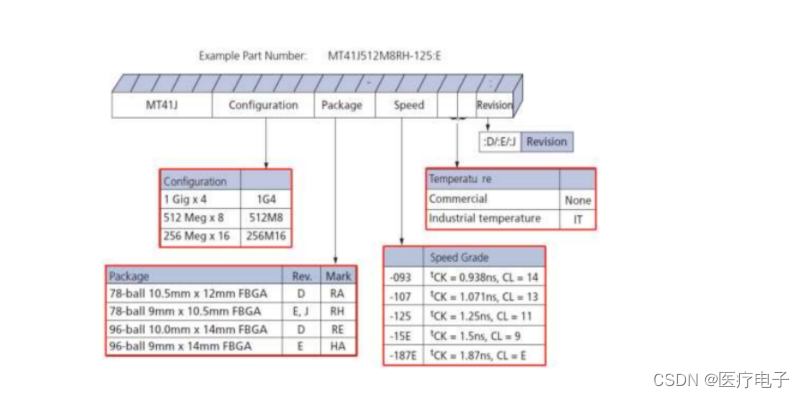

命名的规范:

容量的计算:

DDR3 的内部是一个存储阵列,将数据“填”进去,你可以它想象成一张表格。和表格的检索原理一样,先指定一个行(Row),再指定一个列(Column),我们就可以准确地找到所需要的单元格,这就是内存芯片寻址的基本原理。对于内存,这个单元格可称为存储单元,那么这个表格(存储阵列)就是逻辑 Bank(Logical Bank,简称 Bank)。

存储单元=行 x 列 x 逻辑Bank数量

DDR3为减少地址线,把地址线分为行地址线和列地址线,在硬件上是同一组地址线;行地址线和列地址线是分时复用的,地址要两次发送,线发送行地址线,在发送列地址线。一般来说列地址线是10位,即A0~A9;行地址数量根据内存和BANK数目,数据线位宽等决定。

**举例:**32Meg x 16 x 8 banks 的含义:每个逻辑 BANK 的单元格数×每个单元格的位数×逻辑 BANK 数量(芯片的位宽),即每个逻辑 BANK 的单元格数为 32兆,每个单元格的数据位是 16bit,逻辑 BANK 的数量为 8 个。总大小:32M * 16bit * 8banks = 4096Mbit。

封装:

4/8bit 芯片采用 78 球 FBGA 封装:

16bit 芯片采用 96 球 FBGA:

带宽对比:

DDR3 的催生是源于处理器外频增加引起的对内存带宽增长需求,DDR3 存在的最根本意义在于能提供比 DDR2 更高的数据传输率。带宽对比如下:

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-YSkDLh7d-1671247623873)(硬件电路设计.assets/image-20221213204559615.png)]](https://img-blog.csdnimg.cn/c4400226176d4928a01a3cb93f81b8fe.png)

DDR2 采用了 4bit 预取技术,DDR3 采用了 8bit 预取技术,也就是 Prefetch技术。DDR2 使用了 4-bit 预取技术,一次从存储单元预取 4-bit 的数据,然后在 I/O时钟上升沿和下降沿传输出去,由于 4-bit 需要 2 个时钟周期才能完成传输,这就是为什么 DDR2 的 I/O 时钟频率为存储单元频率两倍的原因。DDR3,采用 8-bit 预取技术,一次从存储单元预取 8-bit 的数据,在 I/O 端口处上下沿触发传输,8-bit 需要 4 个时钟周期完成,所以 DDR3 的 I/O 时钟频率是存储单元核心频率的 4 倍,由于是上下沿都在传输数据,所以实际有效的数据传输频率达到了核心频率的 8 倍。比如,核心频率为 200MHz 的 DDR3-1600,其 I/O 时钟频率为 800MHz,有效数据传输频率为 1600MHz。

各种频率描述:

| 频率 | 描述 |

|---|---|

| 核心频率 | 核心频率就是内存的工作频率,也就是上图表中的内存时钟,一般是 100MHz 到200MHz。对于 DDR3-1600,核心频率就是 200MHz。 |

| 时钟频率 | 时钟频率是指 DDR 芯片 IO 管脚 CK 和 CK#上的时钟信号的频率。DDR3 的时钟频率是核心频率的 4 倍。对于 DDR3-1600,时钟频率就是 800MHz。 |

| 数据传输频率 | DDR 内存在 IO 时钟的上下边沿都传输数据,所以数据传输频率是时钟频率的 2倍。对于 DDR3-1600,数据传输速率就是 1600MT/s。一般我们以数据速率来表述 DDR 的速率。 |

2 电路设计

实战电路:

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-G4STuccL-1671247623878)(硬件电路设计.assets/image-20221217110230412.png)]](https://img-blog.csdnimg.cn/0f09b55fae1a4b4ba270d4c8d3f9e9f7.png)

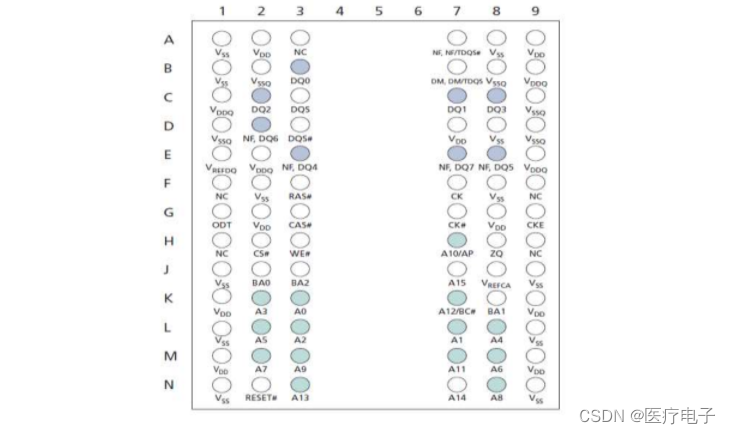

引脚定义:

DDR3 的管脚可以分为电源线、时钟和复位、数据线、地址线和控制线。

| 引脚 | 类型 | 描述 |

|---|---|---|

| VDD | 电源引脚 | 电源电压(1.5±0.075V) |

| VDDQ | 电源引脚 | DQ 电源,1.5V(+/-0.075V),为了降低噪声,在芯片上进行了隔离。 |

| VREFCA | 电源引脚 | 控制、命令、地址的参考电压。VREFCA 在所有时刻(包括自刷新)都必须保持规定的电压。 |

| VREFQ | 电源引脚 | 数据的参考电压。VREFDQ 在所有时刻(包括自刷新)都必须保持规定的电压。 |

| VSS | 电源引脚 | 地 |

| VSSQ | 电源引脚 | DQ地,为了降低噪声,在芯片上进行了隔离。 |

| ZQ | 参考电压 | 输出驱动校准的外部参考。这个脚应该连接 240ohm 电阻到 VSSQ。 |

- 主电源VDD和VDDQ

主电源的要求是 VDDQ=VDD,VDDQ 是给 IO buffer 供电的电源,VDD 是给内核供电。但是一般的使用中都是把 VDDQ 和 VDD 合成一个电源使用。有的芯片还有专门的 VDDL,是给 DLL 供电的,也和 VDD 使用同一电源即可。

参考电源 Vref

参考电源 Vref 要求跟随 VDDQ,并且 Vref=VDDQ/2,所以可以使用电源芯片提供,也可以采用电阻分压的方式得到。由于 Vref 一般电流较小,在几个 mA~几十 mA 的数量级,所以用电阻分压的方式,即节约成本,又能在布局上比较灵活,放置的离 Vref 管脚比较近,紧密的跟随 VDDQ 电压,所以建议使用此种方式。需要注意分压用的电阻在 100Ω~10kΩ 均可,需要使用 1%精度的电阻。Vref 参考电压的每个管脚上需要加 10nF 的电容滤波,并且每个分压电阻上也并联一个电容较好。

匹配的电压 VTT

VTT 为匹配电阻上拉到的电源,VTT=VDDQ/2。DDR 的设计中,根据拓扑结构的不同,有的设计使用不到 VTT,如控制器带的 DDR 器件比较少的情况下。如果使用 VTT,则 VTT 的电流要求是比较大的,所以需要走线使用铜皮铺过去。并且VTT 要求电源既可以吸电流,又可以灌电流才可以。一般情况下可以使用专门为 DDR 设计的产生 VTT 的电源芯片来满足要求。而且,每个拉到 VTT 的电阻旁一般放一个 10Nf~100nF 的电容,整个 VTT 电路上需要有 uF 级大电容进行储能。

时钟和复位:

| 引脚 | 类型 | 功能描述 |

|---|---|---|

| CK、CK# | 输入 | 差分时钟输入,所有控制线和地址线输入信号在CK上升沿和CK#下降沿交叉处被采样。 |

| RESET# | 输出 | 复位,低电平有效。 |

DDR3的时钟位差分走线,一般使用100Ω的匹配电阻,可以有效控制差分信号的上升延缓程度,对EMI有一定的作用。

数据组:

| 引脚 | 类型 | 功能描述 |

|---|---|---|

| DQ0-DQ7 | 输入/输出 | 数据输入/输出,DQ[7,0]参考Vrefdq |

| DQ8-DQ15 | 输入/输出 | 数据输入/输出,DQ15,8]参考Vrefdq |

| DM | 输入 | 数据输入屏蔽 |

地址、控制、命令:

| 地址 | 类型 | 功能描述 |

|---|---|---|

| CKE | 输入 | 时钟使能信号。使能(低)和禁止(高)内部电路和DRAM上的时钟。 |

| CS# | 输入 | 片选信号,使能(高)和禁止(低)。CS#为高时,所有命令都被屏蔽。 |

| BA0、BA1、BA2 | 输入 | Bank地址输入。定义activate、read、write是对那个bank操作。 |

| A0-A9、A10/AP、A11、 A12/BC#、A13-A15 | 输入 | 地址输入 |

| ODT | 输入 | 片上终端使能。ODT使能(高)和禁止(低)片内终端电阻。 |

| RAS# | 输入 | 行地址选通 |

| CAS | 输入 | 列地址选通 |

| WE# | 输入 | 写使能。 |

| TDQS、TDQS# | 输入 | 终端数据选通。当TDQS使能时,DM禁止,TDQS和TDQS#提供终端电阻。 |

| DQS、DQS# | 输入/输出 | 数据选通。读时时输出,边缘与读出的数据对齐。写时是输入,中心与写数据对齐。 |

3 设计要点

-

在进行电路设计前,确定 fpga 配置 DDR 时,器件手册上适配的器件型号。

-

如果 fpga 有专门的 DDR 的存储接口,优先注意接专用的 BANK。

-

电源设计时,需要考虑电压、电流以及上电的时序是否满足要求(TPS51200)。

(注意 DDR3 和 DDR3L(1.35V)的区别,电源设计的时候需要注意)。(有时候1.35V 的 DDR3L,也可以用 1.5V 供电,需要软件里面配置一下。)

-

ZQ 校正功能,加 240 欧姆的电阻到地。

-

ZYNQ 比较特殊,分为 PS 和 PL 两个部分。

-

注意 PCB layout(尤其重要(详见 PCB 设计要点))具体细节看 DDDR3 PCB 设计要点。

-

不是所有的 DDR3 都支持 Fly-By。(详见 PCB 设计要点);有些时序需要严格控制的,注意做 Pin-Delay。

-

DDR3 的 CLK 终端电阻需要串一个 80.6 或 100 欧姆的电阻。且需要靠近 DDR3放置。要是用 80.6,对应的 vtt 端接电阻用 40 欧姆左右;要是用 100,对应的 vtt 端接电阻用 50 欧姆左右。

-

复位处加 4.7K 的下拉电阻。几片互联,一片加上就行了。

-

FPGA 那一侧的处理。

-

DQ 信号线的组,FPGA 对应的 VREF,需要加一个 100nf 的电容接到 VREF;DQS 对应的数据选通端,N 和 P 需要对应。

-

FPGA 那一侧的 IO:一个组内,DQS 和 DM 不要交换管脚。DQ 可以交换。地址线可以交换。注意一些特殊的管脚不要交换。比如时钟、差分之类的。(主要还是考虑布线的一个趋势。)

-

注意信号电平的匹配(HR、HP、HD)

Xilinx 的 7 系列 FPGA 有两种 IO Bank:HP(High Performace)和 HR(High Range)。HP(high-performance)I/O banks 的设计目的是为了获取更高的 Memory 及 chip-to-chip 间的传输速率;而 HR(high-range)I/O banks 的设计目的是为了更宽的 I/O 电平标准。两种 BANK 的 IO 口电压不同,其中 HR I/O Banks 的 VCCO 电压最大为 3.3V,HP I/O banks 的 VCCO 电压最大为 1.8V。特别是初次使用 7 系列时,在硬件设计中特别要注意它们 I/O 口的最大工作电压,一不注意就会把电压搞错,导致 FPGA 不能正常工作。

HR = High Range I/O with support for I/O voltage from 1.2V to 3.3V.

HP = High Performance I/O with support for I/O voltage from 1.0V to 1.8V.

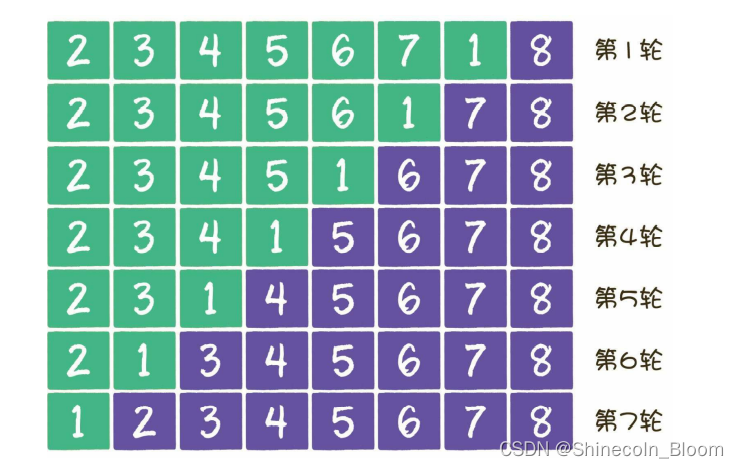

- FPGA 和 DDR3 级联,一般低端一点的 FPGA 配置 1-2 片 DDR、高端的配置 4+片 DDR。

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-SJzXoCyw-1671247623879)(硬件电路设计.assets/image-20221213205710329.png)]](https://img-blog.csdnimg.cn/9d33bd7d87ac474a86a08c607bd3a3ae.png)

![[附源码]Python计算机毕业设计-哈尔滨旅游项目推荐平台Django(程序+LW)](https://img-blog.csdnimg.cn/0d621c6b7bcd4aa6b58fd24cb8b4edb4.png)

![[CCS12.1][CC2340] 环境搭建](https://img-blog.csdnimg.cn/fdcdfadd930e47fba5ac0a5530727e16.png)