目录

01 AXI4-Full Brust传输介绍

write burst transcation

read burst transcation

02 AXI4_Full读写事务接口说明

写事务(Write transaction)

AXI4-Full_master写事务逻辑信号

AXI4-Full_slave写事务逻辑信号

读事务(Read transaction)

AXI4-Full_master读事务逻辑信号

AXI4-Full_slave读事务逻辑信号

03 文章总结

大家好,这里是程序员杰克。一名平平无奇的嵌入式软件工程师。

前面的推送已对AXI总线的特性以及相关内容进行了总结分享。本篇对AXI4-Full总线的一些特性不再赘述,本篇主要内容是对axi4-full的最重要的特性“burst传输”以及读写事务相关信号接口进行总结分享。

01 AXI4-Full Brust传输介绍

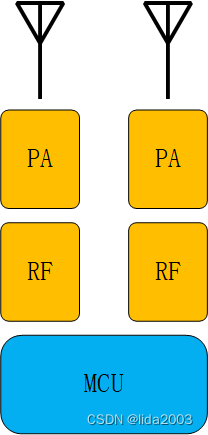

AXI4-Full总线协议其支持突发传输,主要用于处理器访问存储器等需要指定地址的高速数据传输场景。在Xilinx的SOC芯片中,主要用于PL与PS间对DDR/BRAM等高速存储器的读写访问。其在高速、高带宽的数据交互有着很大的作用。本节主要是介绍一下write、read突发传输的传输模型以及简单时序图。

write burst transcation

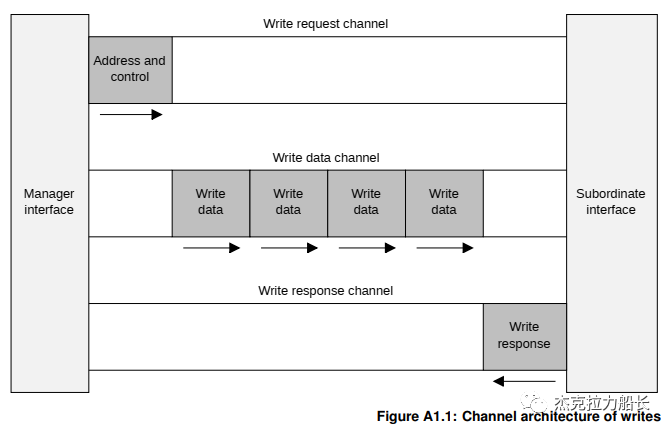

突发写传输模型如下图所示:

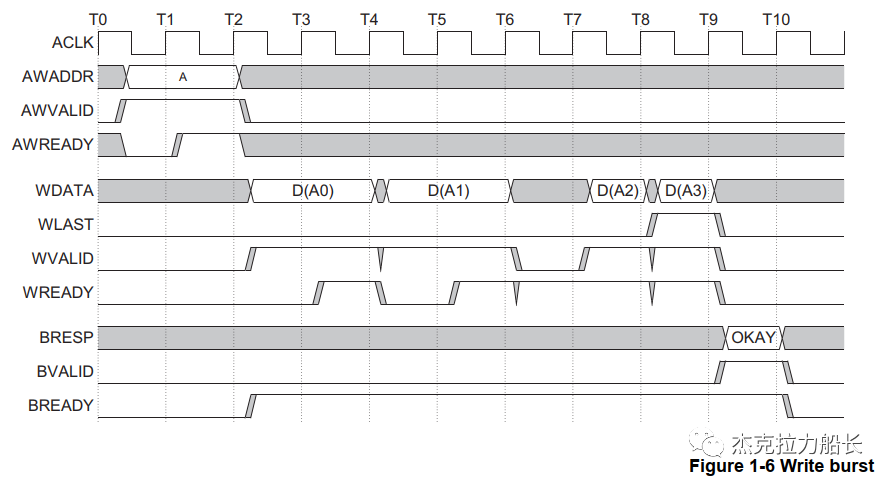

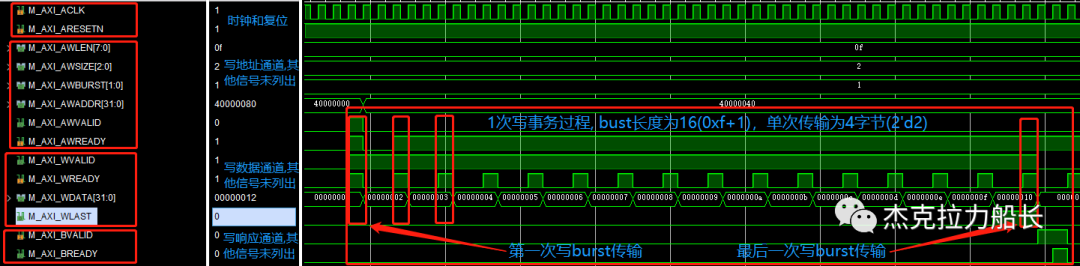

突发写传输时序略图如下所示:

上图与axi4-lite的时序对比来看,axi4-full的握手传输信号多了一个WLAST用以表示brust传输的最后一次;而axi4-lite仅仅支持burst一次;其他的诸如握手机制大同小异。此处其他配置信号并未显示出来。

read burst transcation

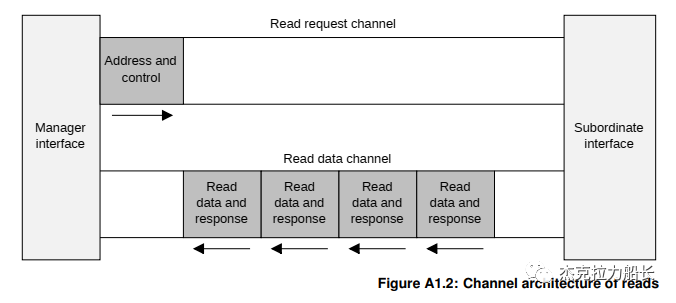

突发读传输模型如下图所示:

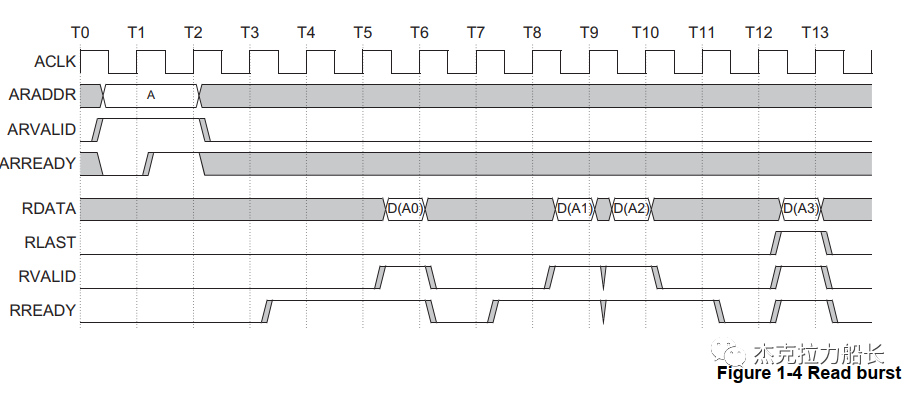

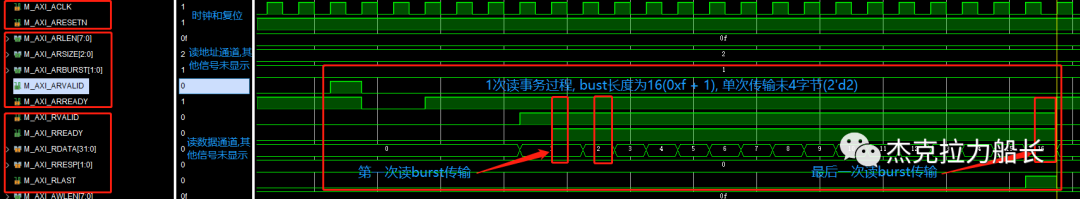

突发读传输时序略图如下所示:

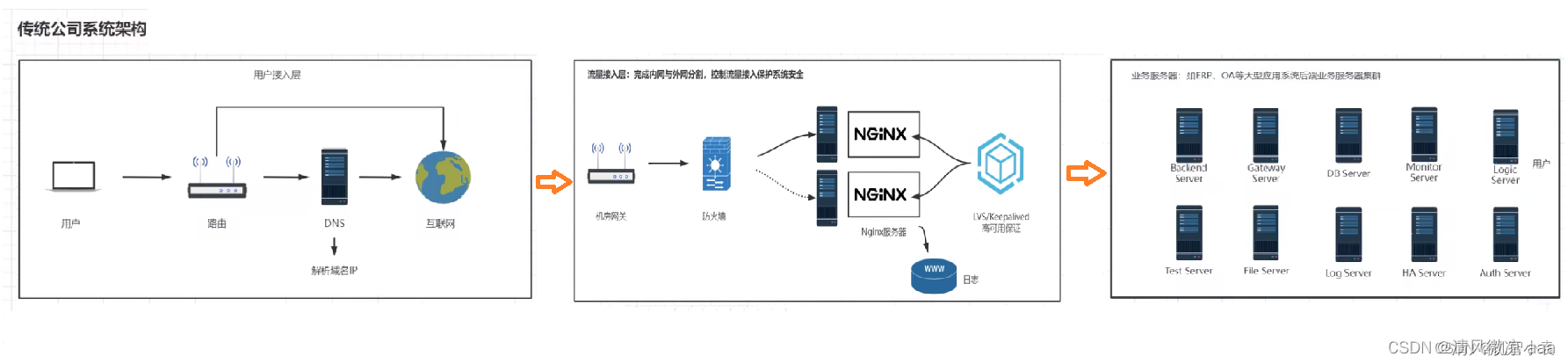

02 AXI4_Full读写事务接口说明

对于AXI4、AXI4-Lite而言,关键是地址和数据。对于地址和数据有效而言,取决于各通道的握手机制(xVALID、xREADY),以此为依据对时序进行分析。

写事务(Write transaction)

AXI4_Full写传输事务逻辑仿真如下:

-

AXI4-Full_master写事务逻辑信号

AXI4-Full_master控制的信号如下表:

| 信号 | 所属通道 | 说明 |

| AWID | 写地址通道 | 写地址ID,用来表征一组写信号 |

| AWADDR | 写入地址/突发传输开始地址 | |

| AWLEN | AWLEN[7:0]写传输的长度(burst次数),位宽为8bit, burst次数=ARLEN + 1,即最大支持256次burst传输. 对于INCR模式(地址递增):最大支持256次brust传输 对于WAP模式(边界环回):最大支持16次brust传输 | |

| AWSIZE[7:0] 固定位宽 | AWSIZE[2:0]单次burst传输的字节大小,位宽为3bit,用于表示传输字节[1, 128]具体如下: 0'b000 = 3'd0 :1字节(8bit) 0'b001 = 3'd1 :2字节(16bit) 0'b010 = 3'd2 :4字节(32bit) 0'b011 = 3'd3 :8字节(64bit) 0'b100 = 3'd4 :16字节(128bit) 0'b101 = 3'd5 :32字节(256bit) 0'b110 = 3'd6 :64字节(512bit) 0'b111 = 3'd7 :128字节(1024bit) | |

| AWBURST[1:0] 固定位宽 | 写突发传输类型: 0'b00-FIXED(固定长度),用于FIFO访问. 0'b01-INCR(地址递增),地址增量取决于AxSIZE的值 0'b10-WRAP(边界环回) 0'b11-RESERVED(无效保留) | |

| AWLOCK | 锁信号, 支持原子操作 | |

| AWCACHE[3:0] 固定位宽 | 内存参数(默认为0): AWCACHE[0] - Bufferable AWCACHE[1] - Modifiable AWCACHE[2] - Other Allocate AWCACHE[3] - Allocate | |

| AWPROT[2:0] 固定位宽 | 内存访问属性. 可用于保护内存免受意外事务的影响. AWPROT[0]:特权/非特权访问 0'b1-特权, 0'b0-非特权 AWPROT[1]:安全属性,与AxNSE共同作用(不详细说明) AWPROT[2]:访问的类型(数据/指令) 0'b1-指令访问, 0'b0-数据访问 | |

| AWQOS | 事务优先级信号, 默认设置为0x0 | |

| AWREGION | 域识别符,表征物理内存区域,可实现单一物理接口对应多个逻辑接口 | |

| AWUSER | 扩展的用户自定义信号 | |

| AWVALID | 有效信号 | |

| WDATA | 写数据通道 | 写数据 |

| WSTRB | 写数据选通信号 | |

| WLAST | 传输标志信号,表示最后一个突发传输 | |

| WUSER | 用户自定义扩展数据 | |

| WVALID | 写有效信号 | |

| BREADY | 写响应通道 | ready信号, 表示master可接收写响应 |

-

AXI4-Full_slave写事务逻辑信号

AXI4-Full_slave控制的信号如下表:

| 信号 | 所属通道 | 说明 |

| AWREADY | 写地址通道 | ready信号, 表示slave可接收写地址控制信号 |

| WREADY | 写数据通道 | ready信号, 表示slave可接收写数据 |

| BID | 写响应通道 | 写传输响应 ID |

| BRESP | 写响应信号,表示写传输的状态 | |

| BUSER | 用户自定义扩展信号 | |

| BVALID | 写响应有效信号 |

读事务(Read transaction)

AXI4_Full读传输事务逻辑仿真如下:

-

AXI4-Full_master读事务逻辑信号

AXI4-Full_master控制的信号如下表:

| 信号 | 所属通道 | 说明 |

| ARID | 读地址通道 | 读地址ID,用来表征一组读信号 |

| ARADDR | 数据突发传输开始读取地址 | |

| ARLEN | ARLEN[7:0]写传输的长度(burst次数),位宽为8bit, burst次数=ARLEN[7:0] + 1,即最大支持256次burst传输. 对于INCR模式(地址递增):最大支持256次brust传输 对于WAP模式(边界环回):最大支持16次brust传输 | |

| ARSIZE[7:0] 固定位宽 | ARSIZE[2:0]单次burst传输的字节大小,位宽为3bit,用于表示传输字节[1, 128]具体如下: 0'b000 = 3'd0 :1字节(8bit) 0'b001 = 3'd1 :2字节(16bit) 0'b010 = 3'd2 :4字节(32bit) 0'b011 = 3'd3 :8字节(64bit) 0'b100 = 3'd4 :16字节(128bit) 0'b101 = 3'd5 :32字节(256bit) 0'b110 = 3'd6 :64字节(512bit) 0'b111 = 3'd7 :128字节(1024bit) | |

| ARBURST[1:0] 固定位宽 | 读突发传输类型: 0'b00-FIXED(固定长度),用于FIFO访问. 0'b01-INCR(地址递增),地址增量取决于AxSIZE的值 0'b10-WRAP(边界环回) 0'b11-RESERVED(无效保留) | |

| ARLOCK | 锁信号, 支持原子操作 | |

| ARCACHE[3:0] 固定位宽 | 内存参数(默认为0): ARCACHE[0] - Bufferable ARCACHE[1] - Modifiable ARCACHE[2] - Allocate ARCACHE[3] - Other Allocate 特别注意: 此处与AWCACHE的各bit代表的含义不一致. 注意区分. | |

| ARPROT[2:0] 固定位宽 | 内存访问属性. 可用于保护内存免受意外事务的影响. ARPROT[0]:特权/非特权访问 0'b1-特权, 0'b0-非特权 ARPROT[1]:安全属性,与AxNSE共同作用(不详细说明) ARPROT[2]:访问的类型(数据/指令) 0'b1-指令访问, 0'b0-数据访问 | |

| ARQOS | 事务优先级信号, 默认设置为0x0 | |

| ARREGION | 域识别符,表征物理内存区域,可实现单一物理接口对应多个逻辑接口 | |

| ARUSER | 扩展的用户自定义信号 | |

| ARVALID | 有效信号 | |

| RREADY | 读数据通道 | ready信号 |

-

AXI4-Full_slave读事务逻辑信号

AXI4-Full_slave控制的信号如下表:

| 信号 | 所属通道 | 说明 |

| ARREADY | 读地址通道 | ready信号, 表示slave可接收读地址控制信号 |

| RID | 读数据通道 | 读传输响应 ID |

| RDATA | 读数据 | |

| RRESP | 读响应,用于表示读传输的状态 | |

| RLAST | 传输标志信号,表示最后一个突发读传输 | |

| RUSER | 扩展的用户自定义信号 | |

| RVALID | 有效信号 |

03 文章总结

鉴于公众号文章篇幅不宜过长,本文仅是对AXI_Full的burst传输模型以及相关接口进行说明,AXI4_Full模板(master/slave)代码的分析便只能在下一篇推送进行分享。

参考文档:

《ug761_axi_reference_guide.pdf》

《UG1037-Vivado-AXI Reference Guide.pdf》

《IHI0022E_amba_axi_and_ace_protocol_spec.pdf》