相信大家对CPU一定不陌生了,从小就耳濡目染了,不过想搞清楚CPU的工作原理,并不是一件简单的事情,毕竟迄今为止,CPU的制造仍然是人类科技的巅峰。下面我们以SIT测试为主,简单的介绍下CPU,至于其工作原理,就不在此做详述。

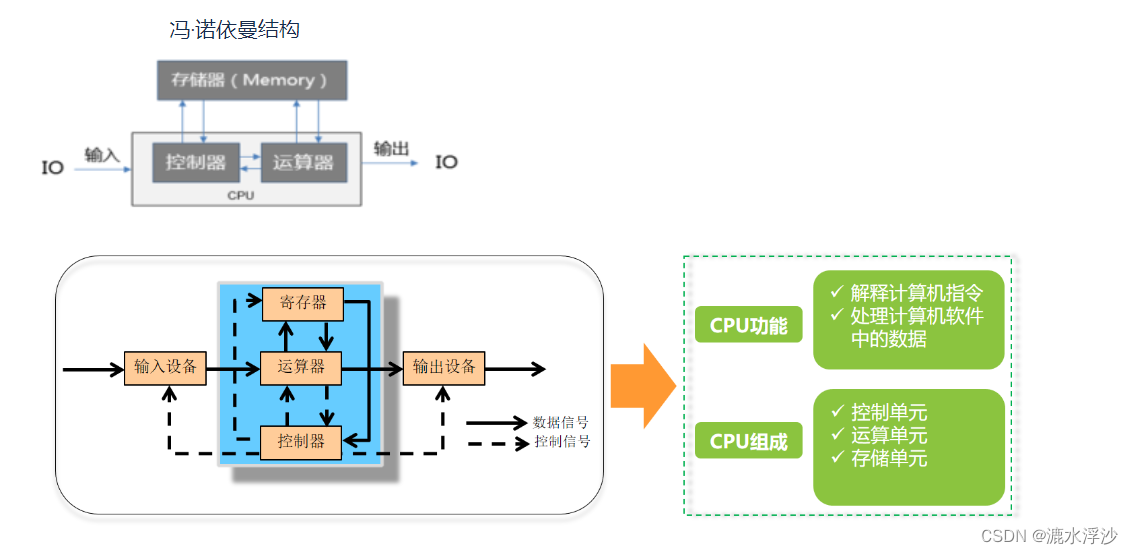

CPU(Central Processing Unit,中央处理器)是一块超大规模的集成电路,通常被称为计算机的大脑,是一台计算机的运算核心(Core)和控制核心( Control Unit),也是整个计算机系统中最重要的组成部件。

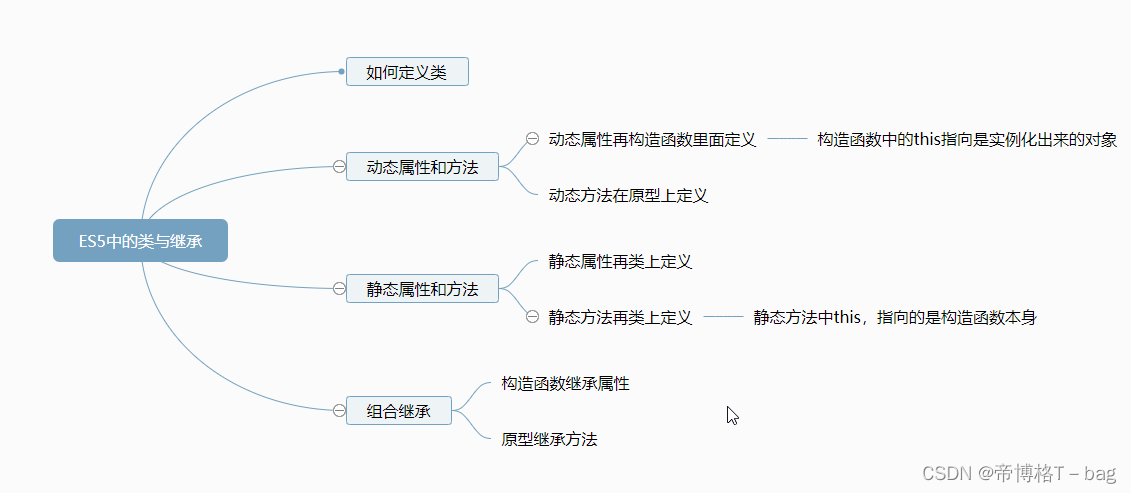

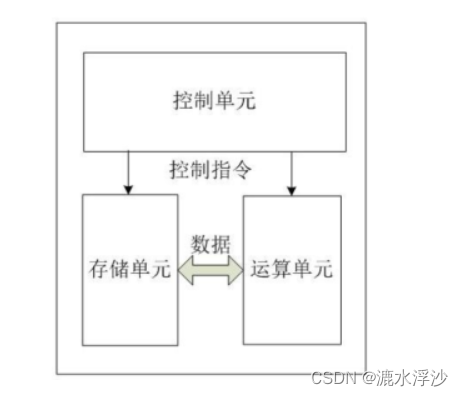

从上图可以看出,CPU在逻辑上由三部分组成。分别是控制单元、运算单元和存储单元,这三部分由CPU内部总线连接起来。如下所示:

控制单元:控制单元是整个CPU的指挥控制中心,由指令寄存器IR(InstrucTIon Register)、指令译码器ID(InstrucTIon Decoder)和操作控制器OC(OperaTIon Controller)等组成,对协调整个电脑有序工作极为重要。它根据用户预先编好的程序,依次从存储器中取出各条指令,放在指令寄存器IR中,通过指令译码(分析)确定应该进行什么操作,然后通过操作控制器OC,按确定的时序,向相应的部件发出微操作控制信号。操作控制器OC中主要包括节拍脉冲发生器、控制矩阵、时钟脉冲发生器、复位电路和启停电路等控制逻辑。

运算单元:是运算器的核心。可以执行算术运算(包括加减乘数等基本运算及其附加运算)和逻辑运算(包括移位、逻辑测试或两个值比较)。相对控制单元而言,运算器接受控制单元的命令而进行动作,即运算单元所进行的全部操作都是由控制单元发出的控制信号来指挥的,所以它是执行部件。

存储单元:包括CPU片内缓存和寄存器组,是CPU中暂时存放数据的地方,里面保存着那些等待处理的数据,或已经处理过的数据,CPU访问寄存器所用的时间要比访问内存的时间短。采用寄存器,可以减少CPU访问内存的次数,从而提高了CPU的工作速度。但因为受到芯片面积和集成度所限,寄存器组的容量不可能很大。寄存器组可分为专用寄存器和通用寄存器。专用寄存器的作用是固定的,分别寄存相应的数据。

CPU指令执行的过程可以分为5个阶段:取指令、指令译码、执行指令、访存取数、结果写回。

取指令阶段就是将内存中的指令读取到CPU中寄存器的过程,程序寄存器用于存储下一条指令所在的地址;

在取指令完成后,立马进入指令译码阶段,在指令译码阶段,指令编码器按照预先的指令格式,对取回的指令进行拆分和解释,识别区分出不同的指令类别和各种获取操作数的方法;

执行指令阶段的任务是完成指令所规定的各种操作,具体实现指令的功能;

访问取数阶段的任务是:根据指令地址码,得到操作数在主存中的地址,并从主存中读取该操作数用于运算;

结果写回阶段作为最后一个阶段,把执行指令阶段的运行结果数据“写回”到某种存储形式:结果数据经常被写到CPU的内部寄存器中,以便被后续的指令快速地存取。

CPU主要技术参数

1 位,字节和字长

位:在数字电路和电脑技术中采用二进制,代码只有“0”和“1”,代表CPU的“位”。

字节 :8位二进制为一个字节

字长:CPU在单位时间内能一次处理的二进制数的位数叫字长

因此,处理字长为8位数据的CPU通常就叫8位的CPU。同理32位的CPU就能在单位时间内处理字长为32位的二进制数据。

8位的CPU一次只能处理一个字节,而32位的CPU一次就能处理4个字节,同理字长为64位的CPU一次可以处理8个字节。

常见的服务器基本上都是64位的双路CPU

2 主频,外频和倍频

CPU 频率是CPU内部的数字时钟信号频率 。单位时间(即1s)内所产生的脉冲个数称之为频率,频率的标准计量单位是Hz。比如一个CPU每秒可以发送10000个脉冲信号,那么他的频率就是10MHZ。

CPU的主频,即CPU内核工作的主时钟频率,表示在CPU内数字脉冲信号震荡的速度。比如我们平时看到的4.0GHZ、3.0GHZ等指的就是CPU主频,即每秒可以产生40亿、30亿个脉冲信号。

主频=外频×倍频系数

外频通常为系统总线的工作频率,是CPU的基准频率,单位是MHz。外频是CPU与主板之间同步运行的速度,所以也可以说CPU的外频决定着整块主板的运行速度。

自从CPU诞生后,为了追求更高的性能,更快的速度,各大巨头就开始频率大战,虽然主频提升了,但外部芯片组还是旧有的运行频率,且远低于CPU主频。比如CPU的主频是10GHZ,网卡只有1GHZ,那么CPU就好比飞机带一个自行车跑,根本带不起来。那如何解决呢?外频和倍频应运而生。

倍频是指CPU主频与外频之间的相对比例关系,主频=外频*倍频

以前没有倍频概念,外频(系统总线频率)就相当于CPU的主频,两者速度一样。随着CPU的速度越来越快,倍频技术也就随之出现。即使外频(系统总线频率)工作速度相对较低,CPU速度仍然可以通过倍频来提升。

但由于CPU与系统之间数据传输速度有限,如果一味追求高倍频CPU会出现明显的瓶颈效应,即CPU从系统中得到数据的极限速度不能够满足CPU运算的速度。所以一般Intel的CPU都锁了倍频(工程样板可能除外),AMD之前也因为不锁倍频而很受电脑发烧友的追捧。

现在CPU频率越来高,从 2.4GHz、3.0GHz 到 4.0GHz,大家很容易产生 CPU 频率越高,速度越快的想法。

严谨来说,主频和实际的运算速度存在一定的关系,并不直接代表运算速度,但提高主频对于提高CPU运算速度却是至关重要的。

在同一时钟周期内,CPU执行一条运算指令,200Mhz主频应该要比100Mhz的主频快一倍,但除了CPU内核的工作频率,CPU的运算速度还要看CPU的流水线(如缓存、指令集、CPU位数等)各方面的性能指标,所以大家好才是真的好,不能只看CPU主频。

3 前端总线(FSB)频率

前端总线(Front Side Bus)频率:CPU就是通过前端总线连接到北桥芯片,进而通过北桥芯片和内存、显卡交换数据。前端总线是CPU和外界交换数据的最主要通道,因此前端总线的数据传输能力对计算机整体性能作用很大,如果没足够快的前端总线,再强的CPU也不能明显提高计算机整体速度。

前段总线频率直接影响CPU与内存直接数据交换速度。有一条公式:

数据带宽=(总线频率*数据位宽)/8

数据传输最大带宽取决于所有同时传输的数据的宽度和传输频率。比如,现在的支持64位的至强处理器,前端总线是800MHz,按照公式,它的数据传输最大带宽是6.4GB/秒。

外频与前端总线(FSB)频率的区别

前端总线的速度指的是数据传输的速度,外频是CPU与主板之间同步运行的速度。

也就是说,100MHz外频特指数字脉冲信号在每秒钟震荡一千万次;而100MHz前端总线指的是每秒钟CPU可接受的数据传输量是100MHz*64bit÷8Byte/bit=800MB/s。

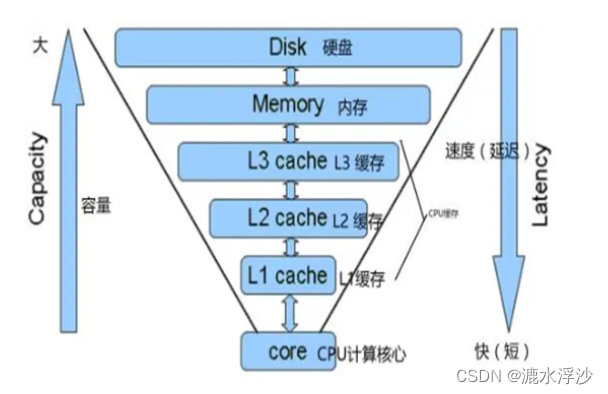

4 缓存 Cache

CPU缓存(Cache Memory)是位于CPU与内存之间的临时存储器,它的容量比内存小的多但是交换速度却比内存要快得多。CPU高速缓存的出现主要是为了解决CPU运算速度与内存读写速度不匹配的矛盾,因为CPU运算速度要比内存读写速度快很多,这样会使CPU花费很长时间等待数据到来或把数据写入内存。在缓存中的数据是内存中的一小部分,但这一小部分是短时间内CPU即将访问的,当CPU调用大量数据时,就可先缓存中调用,从而加快读取速度。

当CPU需要读取数据并进行计算时,首先需要将CPU缓存中查到所需的数据,并在最短的时间下交付给CPU。如果没有查到所需的数据,CPU就会提出“要求”经过缓存从内存中读取,再原路返回至CPU进行计算。而同时,把这个数据所在的数据也调入缓存,可以使得以后对整块数据的读取都从缓存中进行,不必再调用内存。

缓存大小是CPU的重要指标之一,而且缓存的结构和大小对CPU速度的影响非常大,CPU内缓存的运行频率极高,一般是和处理器同频运作,工作效率远远大于系统内存和硬盘。实际工作时,CPU往往需要重复读取同样的数据块,而缓存容量的增大,可以大幅度提升CPU内部读取数据的命中率,而不用再到内存或者硬盘上寻找,以此提高系统性能。但是从CPU芯片面积和成本的因素来考虑,缓存都很小。

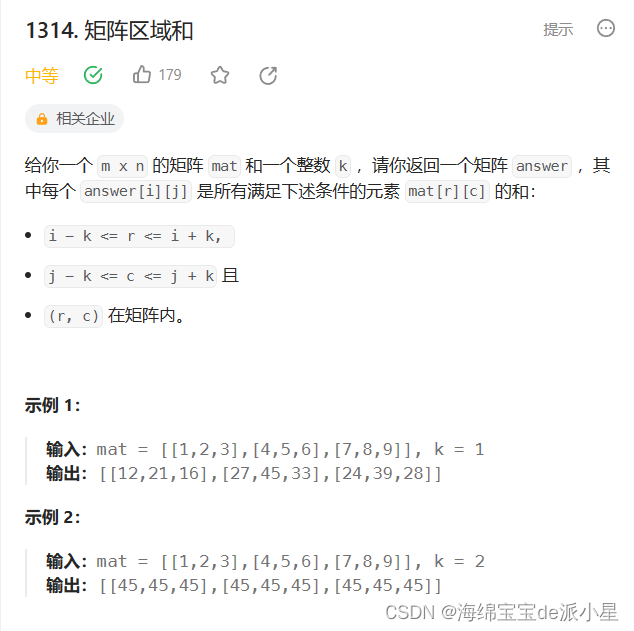

L1 Cache(一级缓存)是CPU第一层高速缓存,分为数据缓存和指令缓存。

内置的L1高速缓存的容量和结构对CPU的性能影响较大,L1级高速缓存的容量不可能做得太大。一般服务器CPU的L1缓存的容量通常在32—256KB。

L2 Cache(二级缓存)是CPU的第二层高速缓存,分内部和外部两种芯片。

内部的芯片二级缓存运行速度与主频相同,而外部的二级缓存则只有主频的一半。L2高速缓存容量也会影响CPU的性能,原则是越大越好,服务器和工作站上用CPU的L2高速缓存更高达256-1MB,有的高达2MB或者3MB。

L3 Cache(三级缓存),分为两种,早期的是外置,现在的都是内置的。

而它的实际作用即是,L3缓存的应用可以进一步降低内存延迟,同时提升大数据量计算时处理器的性能。降低内存延迟和提升大数据量计算能力对游戏都很有帮助。而在服务器领域增加L3缓存在性能方面仍然有显著的提升。

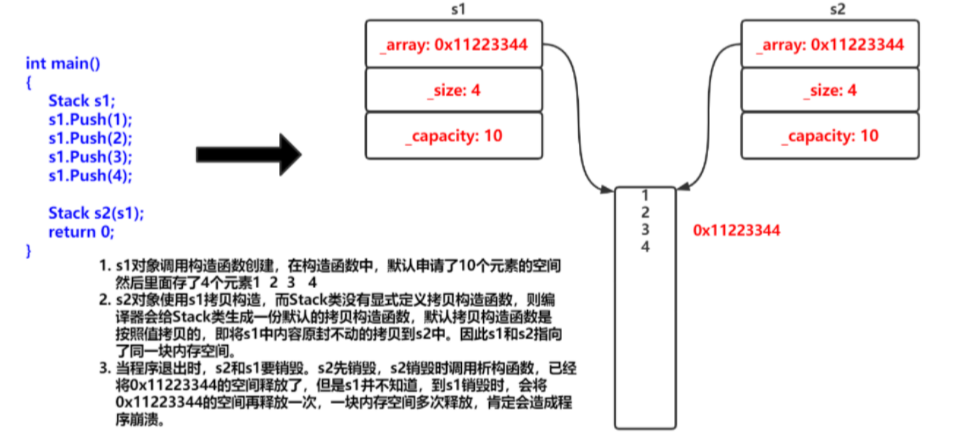

示例如下图:

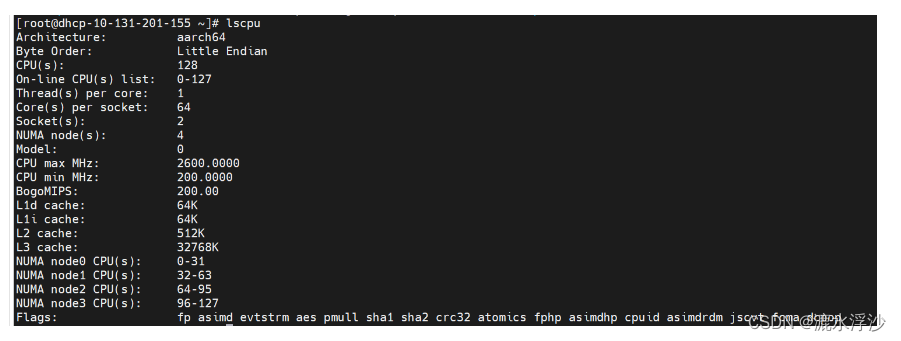

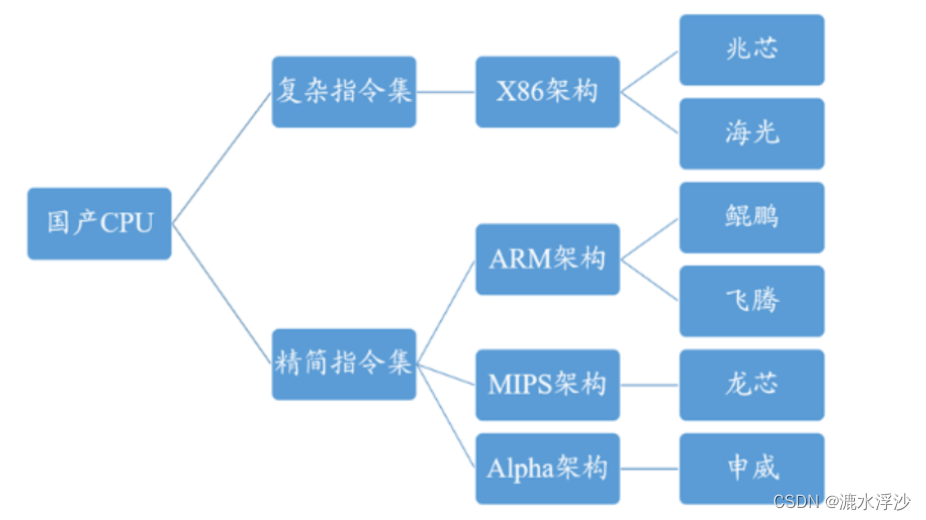

CPU的分类

CPU如果按照指令集分类的话,可以分为复杂指令集和精简指令集

CISC(complex instruction set computer),复杂指令集。早期的CPU全部是CISC架构,它的设计目的是要用最少的机器语言指令来完成所需的计算任务。这种架构会增加CPU结构的复杂性和对CPU工艺的要求,但对于编译器的开发十分有利。比如Intel和AMD的X86架构的CPU以及AMD授权的曙光研发的海光系列CPU。

RISC(Reduced Instruction Set Computer),精简指令集。RISC架构要求软件来指定各个操作步骤。这种架构可以降低CPU的复杂性以及允许在同样的工艺水平下生产出功能更强大的CPU,但对于编译器的设计有更高的要求。比如授权于ARM公司的华为鲲鹏系列的CPU。

我们在测试的时候遇到最多的就是X86和ARM的CPU,不过百分之90都是Intel和AMD,随着国产CPU的崛起,后面很有可能会遇见更多的国产CPU

![[matlab]matlab配置mingw64编译器](https://img-blog.csdnimg.cn/670dca82206f4d4e9a3ce799b27ab248.png)