标题:Simulation Study of 4H-SiC UMOSFET Structure With p+ -polySi/SiC Shielded Region

摘要

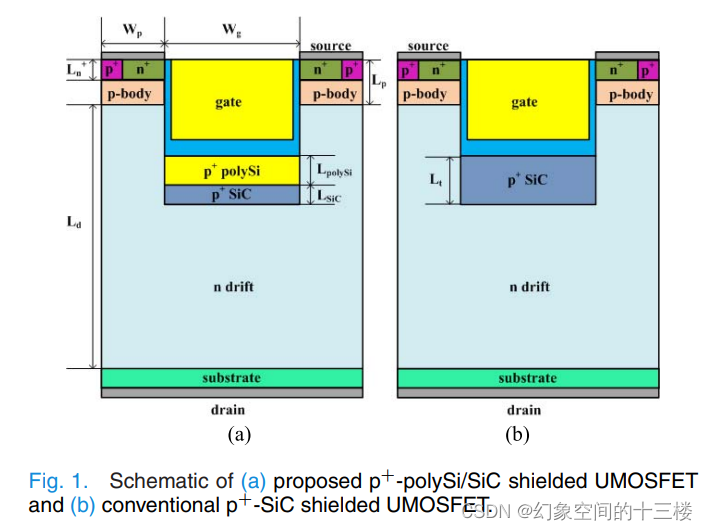

在这篇论文中,我们提出了一种改进效率的4H-SiC U型沟槽栅MOSFET(UMOSFET)结构。所提出的器件结构利用p±polySi/SiC被屏蔽区来降低导通状态的比电阻。我们展示了由p+ -polySi和n-drift区域形成的异质结二极管改善了体二极管效应,从而减少了反向恢复电荷。此外,我们通过模拟结果说明,与传统的p±SiC被屏蔽UMOSFET相比,所提出的器件结构在优势因子(包括击穿电压和导通电阻)方面提供了56.5%的改善,并分别在比电阻和反向恢复电荷方面减少了35.7%和55.5%。

关键词:击穿电压(BV)、电场、导通状态比电阻(RON,sp)、反向恢复电荷(Qrr)、碳化硅(SiC)、U型沟槽栅MOSFET(UMOSFET)

文章研究了什么

该文章研究了带有 p+ -polySi/SiC 被屏蔽区的 4H-SiC UMOSFET 结构的模拟。

文章的创新点是什么

该文章的创新点是提出了一种具有 p+ -polySi/SiC 被屏蔽区的改进效率的4H-SiC UMOSFET结构。该结构利用由 p+ -polySi 和 n-drift 区域形成的异质结二极管来改善体二极管效应并减少反向恢复电荷。通过模拟结果表明,与传统的 p+ -SiC 被屏蔽 UMOSFET 相比,所提出的器件结构在优势因子(包括击穿电压和导通电阻)方面提供了56.5%的改善,并分别在比电阻和反向恢复电荷方面减少了35.7%和55.5%。

文章的研究方法

- 该文章采用基于模拟的研究方法。

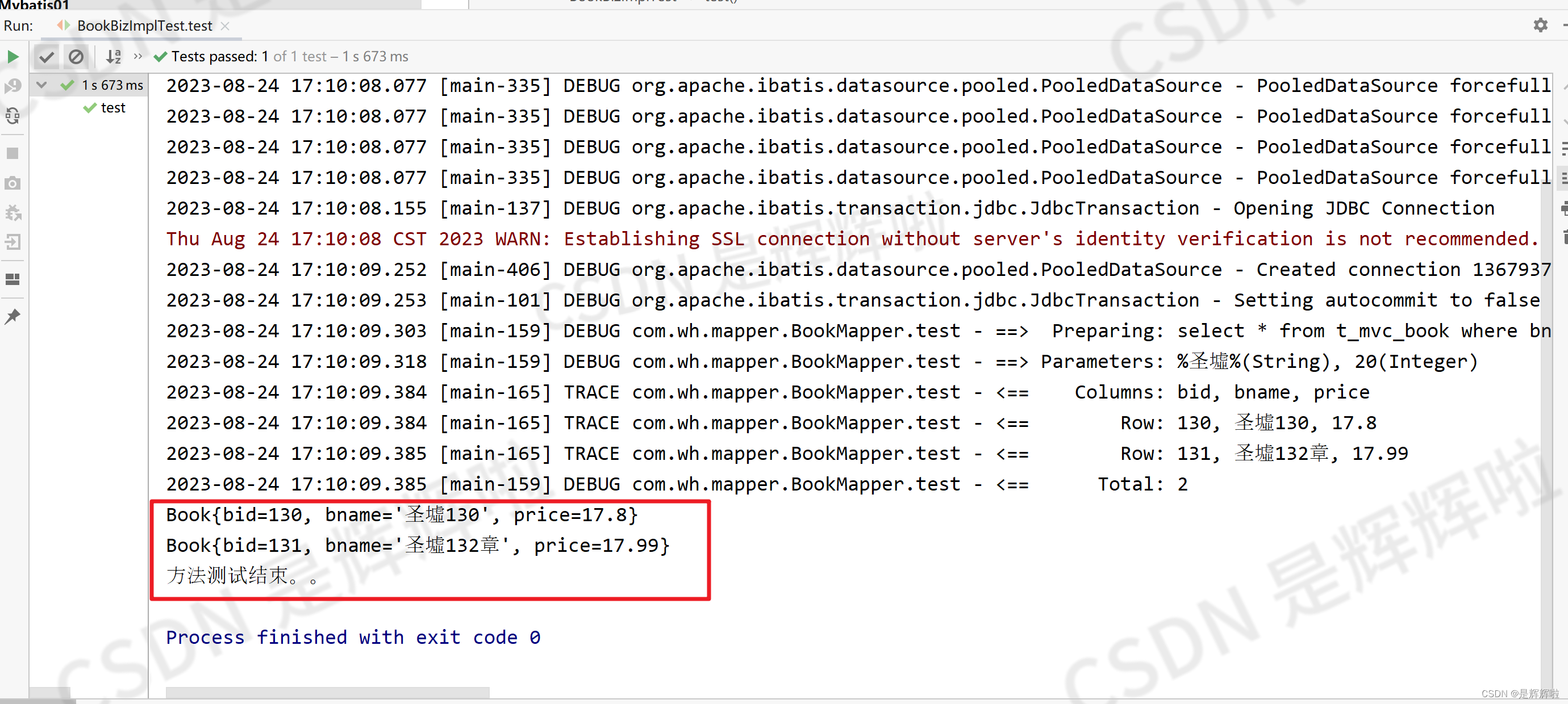

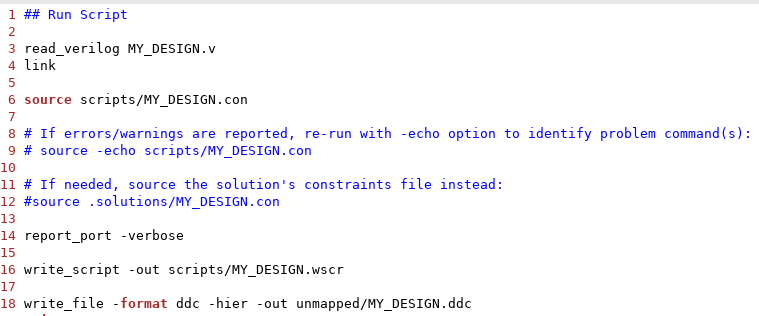

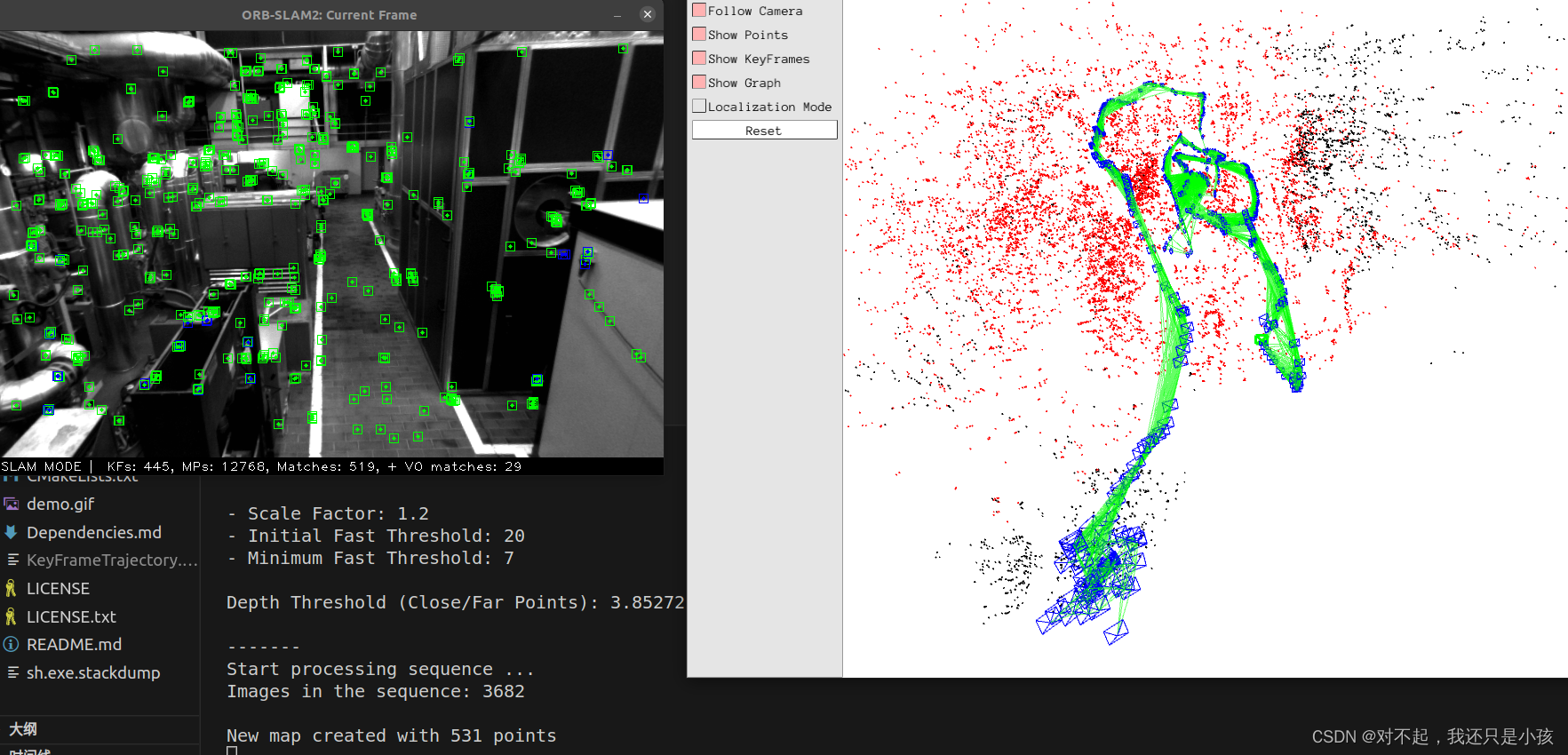

- 使用商业软件ATLAS SILVACO对所提出的沟槽栅4H-SiC MOSFET结构进行了模拟,并获得了器件的示意图剖面视图。

- 模拟过程基于多个物理模型,包括FLDMOB、ANALYTIC、SRH、AUGER、IMPACT SELB和INCOMPLETE模型。

- 模拟器件的详细参数列在表格I中。

- 通过模拟结果对比传统的p+ -SiC被屏蔽UMOSFET,评估了所提出的器件结构的性能。

- 研究了p-polySi/SiC被屏蔽区比例LpolySiLSiC对击穿电压(BV)和导通电阻(RON,sp)的影响。

- 分析了pn-SiC结和p-Sin-SiC结的能带图和耗尽区宽度,以了解所提出结构的行为。

文章的结论

- 该文章提出了一种具有 p+ -polySi/SiC 被屏蔽区的改进效率的4H-SiC UMOSFET结构。

- 所提出的结构相比传统的 p+ -SiC 被屏蔽 UMOSFET,在包括击穿电压和导通电阻在内的优势因子方面改善了56.5%。

- 它实现了35.7%的比电阻降低和55.5%的反向恢复电荷减少。

- 模拟结果表明,与 p+ -SiC 被屏蔽 UMOSFET 相比,p+ -polySi/SiC 被屏蔽 UMOSFET 的比电阻值减少了35.7%。

- 所提出结构的击穿性能保持不变。

- p+ -polySi/SiC 被屏蔽 UMOSFET 还改善了反向恢复特性,将反向恢复电荷减少了55.5%,相比于 p+ -SiC 版本。