GPMC并口简介

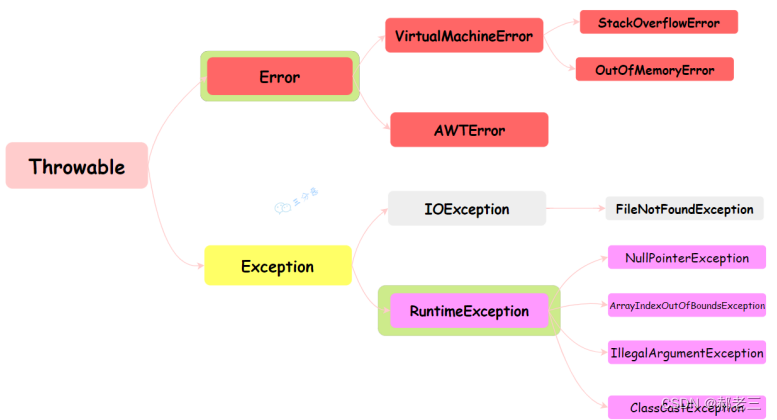

GPMC(General Purpose Memory Controller)是TI处理器特有的通用存储器控制器接口,支持8/16bit数据位宽,支持128MB访问空间,最高时钟速率133MHz。GPMC是AM62x、AM64x、AM437x、AM335x、AM57x等处理器专用于与外部存储器设备的接口,如:

(1)FPGA器件

(2)ADC器件

(3)SRAM内存

(4)NOR/NAND闪存

GPMC并口3大特点

(1)小数据-低时延

在工业自动化控制领域中,如工业PLC、驱控一体控制器、运动控制器、CNC数控主板、继电保护设备、小电流接地选线等,极其注重精确性与快速性,GPMC并口“小数据-低时延”的特点显得格外耀眼,能够很好地提高数据传输效率,降低传输成本。

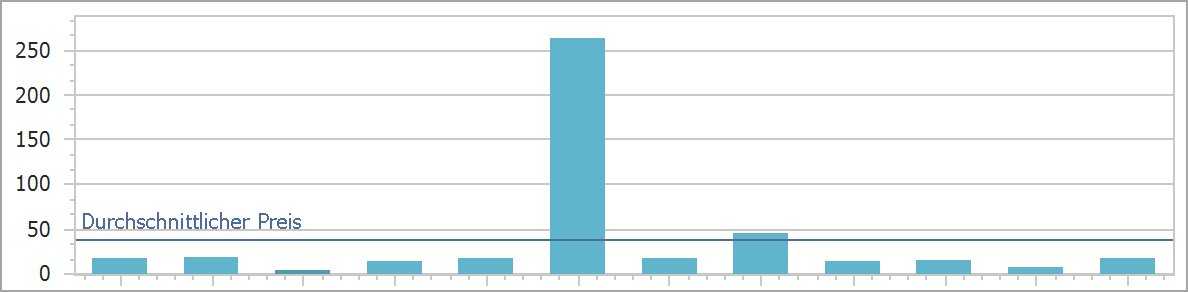

(2)大数据-高带宽大数据时代对能源电力领域的数据量传输、数据处理等方面提出了更高的要求。GPMC提供了最大的灵活性,以支持四个可配置片选中不同的时序参数和位宽配置。可根据外部设备的特点,使用最佳的片选设置。可通过配置GPMC接口的时序参数和不同工作模式,最大速率可超过100MB/s。因此,GPMC“大数据-高带宽”的特点在能源电力领域扮演着重要角色。

(3)低成本-低功耗“低成本、低功耗、高性能”是如今智能设备发展趋势,GPMC并口相对于PCIe串行接口,成本更低、功耗更低。两者都为常用的通信接口,均可满足高速通信要求,但在与FPGA通信的时候,用户往往更喜欢选用GPMC并口,因为:1、使用低成本FPGA即可实现高速通信,而具备PCIe接口的FPGA成本则成倍增长。2、具备PCIe接口的FPGA功耗往往较大,而低成本FPGA功耗较小。一般而言,低功耗器件的使用寿命也将更长。

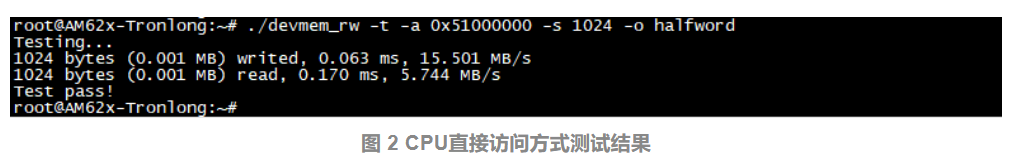

基于CPU直接访问方式

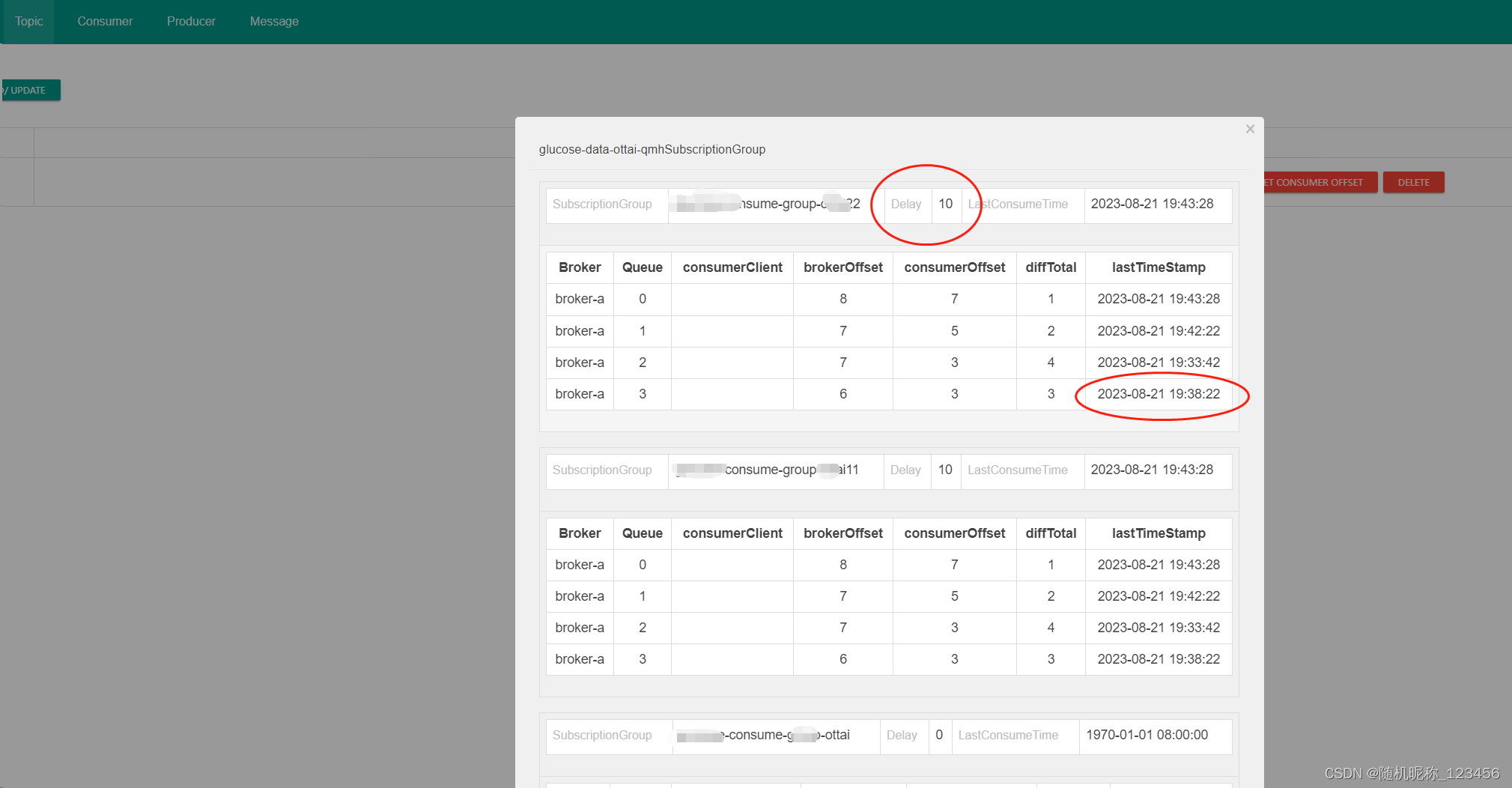

以AM62x为例,通过GPMC接口与FPGA连接,采用CPU直接访问方式读取FPGA端的数据,写速度可达15.501MB/s,读速度可达5.744MB/s。

此方式适合“小数据-低时延”场合。

程序流程说明:

(1)ARM端通过GPMC总线将数据写入FPGA BRAM;(2)ARM端通过GPMC总线从FPGA BRAM读取数据;(3)判断写入与读取数据的正确性,并计算读写速率。

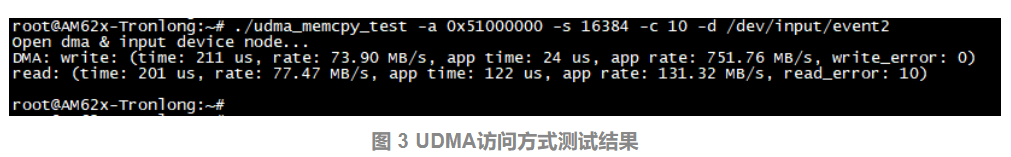

基于UDMA访问方式

以AM62x为例,通过GPMC接口与FPGA连接,采用UDMA的方式读取FPGA端的数据,写速度可达73.90MB/s,读速度可达77.47MB/s,实际上通过配置GPMC接口的时序参数和不同工作模式,最大速率可超过100MB/s。

此方式适合“大数据-高带宽”场合。

备注:由于测试受线材限制影响,因此测得误码率会过高。

程序流程说明

ARM端

:(1) 采用UDMA方式;

(2)将数据写入至dma_memcpy驱动申请的连续内存空间(位于DDR);

(3)配置UDMA,如源地址、目标地址、传输的数据大小等;

(4)写操作:通过ioctl函数启动UDMA,通过GPMC总线将数据搬运至FPGA BRAM;

(5)程序接收驱动上报input事件后,将通过ioctl函数获取UDMA搬运数据耗时,并计算UDMA传输速率(即写速率);

(6)读操作:通过ioctl函数启动UDMA,通过GPMC总线将FPGA BRAM中的数据搬运至dma_memcpy驱动申请的连续内存空间;

(7)程序接收驱动上报input事件后,将数据从内核空间读取至用户空间,然后校验数据,同时通过ioctl函数获取UDMA搬运数据耗时,并计算UDMA传输速率(即读速率)。

FPGA端:

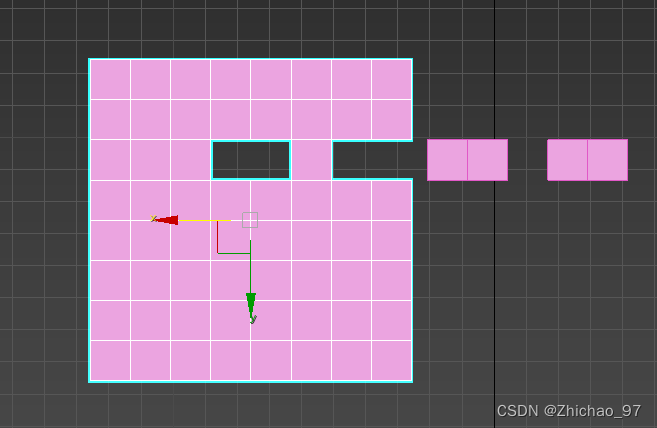

(1)根据ARM端GPMC时序解析数据,对FPGA内部BRAM资源进行访问。BRAM的地址位宽为10bit,数据位宽为16bit,内存空间大小为2KByte(1024 x 16bit)。

分类: 产品文章

好文要顶 关注我 收藏该文

![]()

![]()

![]()

创龙科技-黄工

粉丝 - 1 关注 - 0

0

0

« 上一篇: 【资料分享】全志科技T507工业核心板硬件说明书(下)

posted @ 2023-08-22 10:05 创龙科技-黄工 阅读(1) 评论(0) 编辑 收藏 举报

刷新评论刷