目录

一、IP芯片化

二、异质集成(HeteroMaterial Integration)

三、异构集成(HeteroStructure Integration)

四、IO增量化

五、总结

一、IP芯片化

IP(Intelligent Property)是具有知识产权核的集成电路的总称,是经过反复验证过的、具有特定功能的宏模块,可以移植到不同的半导体工艺中。到了SoC阶段,IP核设计已成为ASIC电路设计公司和FPGA提供商的重要任务,也是其实力的体现。对于芯片开发软件,其提供的IP核越丰富,用户的设计就越方便,其市场占用率就越高。目前,IP核已经变成SoC系统设计的基本单元,并作为独立设计成果被交换、转让和销售。IP核对应描述功能行为的不同分为三类,即软核(Soft IP Core)、固核(Firm IP Core)和硬核(Hard IP Core)。当IP硬核是以硅片的形式提供时,就变成了Chiplet。

我们可以这么理解:SiP中的Chiplet就对应于SoC中的IP硬核。Chiplet 就是一个新的 IP 重用模式,就是硅片级别的IP重用。设计一个SoC系统级芯片,以前的方法是从不同的 IP 供应商购买一些 IP,软核、固核或硬核,结合自研的模块,集成为一个 SoC,然后在某个芯片工艺节点上完成芯片设计和生产的完整流程。有了Chiplet以后,对于某些 IP,就不需要自己做设计和生产了,而只需要买别人实现好的硅片,然后在一个封装里集成起来,形成一个 SiP。所以 Chiplet 可以看成是一种硬核形式的 IP,但它是以芯片的形式提供的。因此,我们称之为IP芯片化。

注意:关于软核(Soft IP Core)、固核(Firm IP Core)和硬核(Hard IP Core)

软核是最灵活的,它可以根据需要进行完全定制,但需要更多的设计和验证工作。固核是次之,它有一定的可定制性,但已经经过了基本的验证和优化,可以提供更快的设计周期。硬核是最不可定制的,它没有任何可定制的部分,但可以提供最快的设计周期和最佳的性能。

在选择IP核时,需要根据设计的需求和要求来决定使用哪种类型的核。如果需要完全定制的功能,则需要使用软核;如果需要快速设计和优化性能,则可以使用固核或硬核。

二、异质集成(HeteroMaterial Integration)

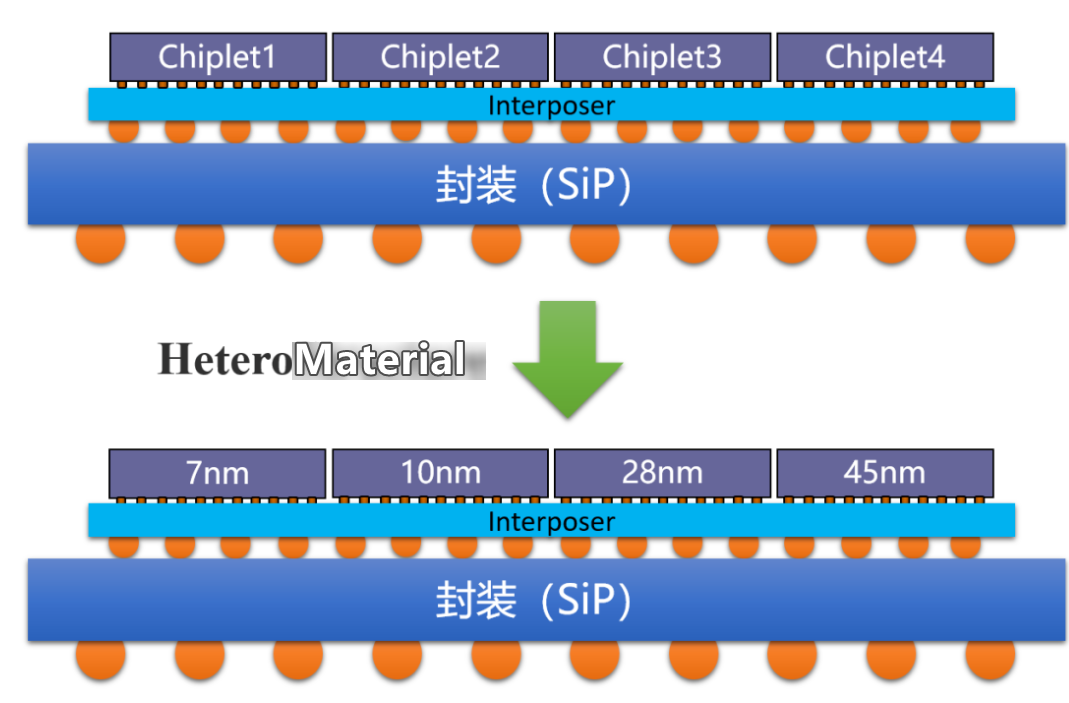

异质集成是指将不同材料或不同工艺制造的芯片集成在一起,构成一个完整的系统。这种集成方式的优点在于能够充分利用各种材料和工艺的优势,提高系统的性能和可靠性。

比如说,在处理器的设计中,可以使用异质集成的方式来制造Chiplets。每个Chiplet都可以使用不同的技术和制造工艺来制造,比如7nm和5nm等。然后,通过芯片联结器将这些Chiplets连接在一起,构成一个完整的处理器。通过使用异质集成的方式,可以让处理器拥有更高的性能和更好的可靠性。

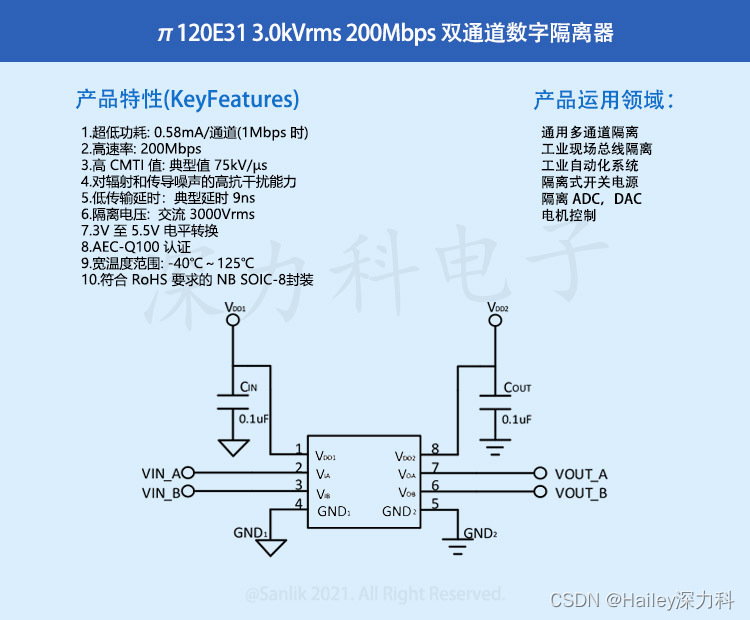

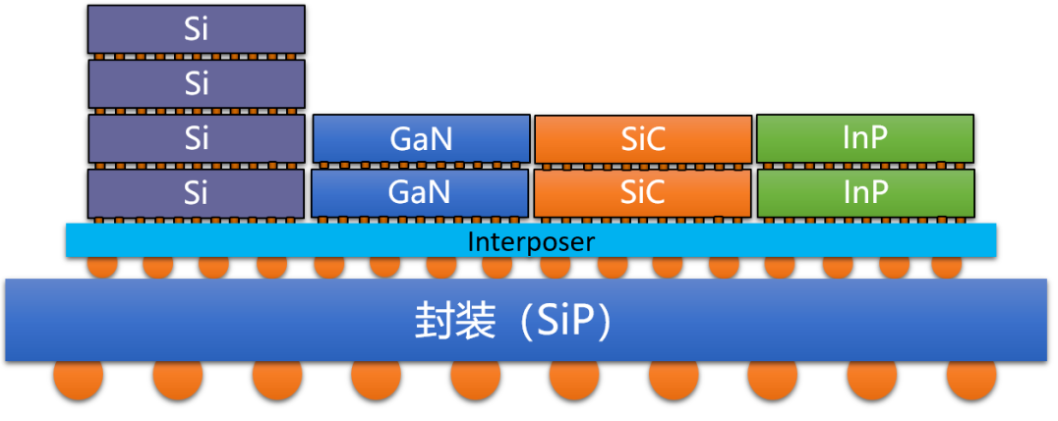

此外,各个芯片的材料可以是不同的,比如金属、绝缘材料、半导体材料等。通常来说,不同的材料具有不同的物理性质和电学性质,能够提供不同的功能和性能。例如,金属材料具有良好的导电性和导热性,可以用于制作电路的导电部分;而绝缘材料具有良好的绝缘性。 因此将不同材料的半导体集成为一体——即异质集成HeteroMaterial Integration,可产生尺寸小、经济性好、设计灵活性高、系统性能更佳的产品。如下图所示,将Si、GaN、SiC、InP生产加工的Chiplet通过异质集成技术封装到一起,形成不同材料的半导体在同一款封装内协同工作的场景。

在单个衬底上横向集成不同材料的半导体器件(硅和化合物半导体)以及无源元件(包括滤波器和天线)等是Chiplet应用中比较常见的集成方式。需要读者注意的是,目前不同材料的多芯片集成主要采用横向平铺的方式在基板上集成,对于纵向堆叠集成,则倾向于堆叠中的芯片采用同种材质,从而避免了由于热膨胀系统等参数的不一致而导致的产品可靠性降低,如下图所示。

总之,异质集成是一种常用的集成方式,它能够提高系统的性能和可靠性,是许多系统设计中的一个重要技术。

三、异构集成(HeteroStructure Integration)

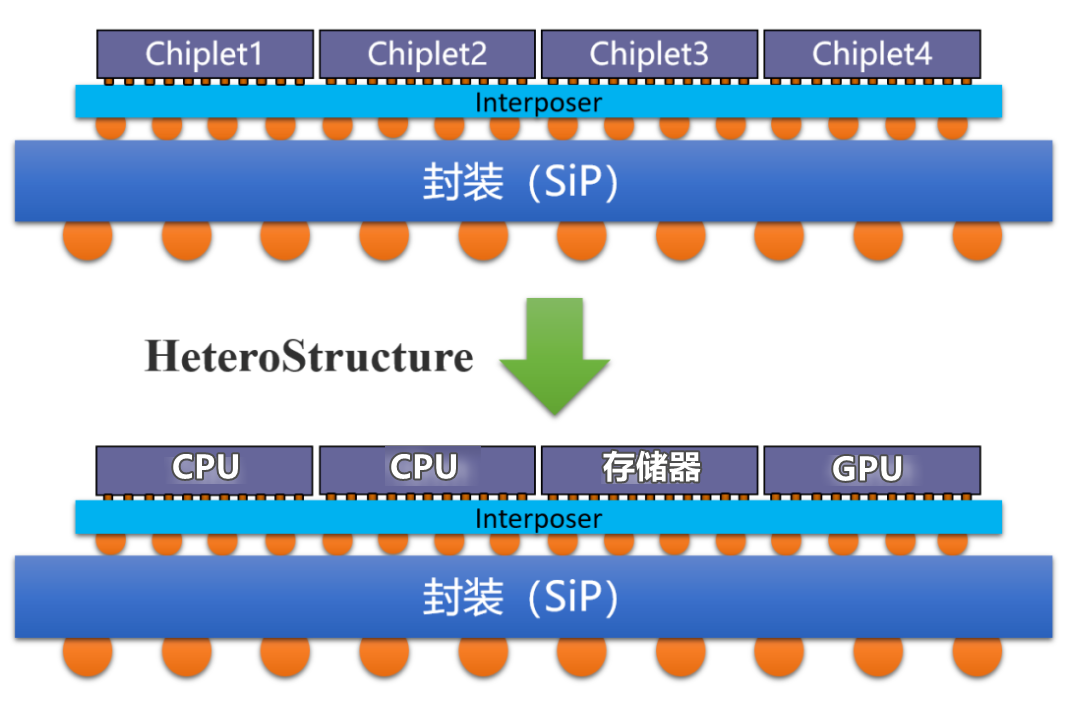

异构集成是指将不同类型的芯片集成在一起(指的是不同功能、不同架构、不同性能等),构成一个完整的系统。这种集成方式的优点在于能够充分利用各种芯片的优势,提高系统的性能和可靠性。

比如说,在处理器的设计中,可以使用异构集成的方式来制造Chiplets。每个Chiplet都可以使用不同类型的芯片来制造,常见的芯片类型包括CPU、GPU、FPGA、ASIC和SOC等。然后,通过芯片联结器将这些Chiplets连接在一起,构成一个完整的处理器。通过使用异构集成的方式,可以将不同类型的芯片有效地结合在一起,实现系统的协同工作,达到更高的性能水平。

四、IO增量化

如果说前面的“三化”是Chiplet技术的优势,那么,IO增量化则给Chiplet带来了挑战。IO增量化体现在水平互联(RDL)的的增量化,同时也体现在垂直互联(TSV)的增量化。

- 水平互联(RDL,Redistributed Layer)指的是在芯片表面的铺铜线路。通过增加水平互联的层数,可以增加芯片的IO端口数量。

- 垂直互联(TSV,Through-Silicon Via)指的是将芯片堆叠在一起时,在芯片之间连接的立体电路。通过增加垂直互联的层数,可以增加芯片的IO端口数量。

因此,通过增量化的方式来增加芯片的IO端口数量,可以在不影响整个系统性能的情况下提高芯片的能力。

在传统的封装设计中,IO数量一般控制在几百或者数千个,Bondwire工艺一般支持的IO数量最多数百个,当IO数量超过一千个时,多采用FlipChip工艺。在Chiplet设计中,IO数量有可能多达几十万个,为什么会有这么大的IO增量呢?(一些关于封装的知识点,我记录一些笔记,如下:)

傻白入门芯片设计,芯片键合(Die Bonding)(四)_好啊啊啊啊的博客-CSDN博客_die attach 设备

(20条消息) 傻白入门芯片设计,先进封装技术(五)_好啊啊啊啊的博客-CSDN博客

(20条消息) 傻白入门芯片设计,典型的2D/2D+/2.5D/3D封装技术(六)_好啊啊啊啊的博客-CSDN博客

我们知道,一块PCB的对外接口通常不超过几十个,一款封装对外的接口为几百个到数千个,而在芯片内部,晶体管之间的互联数量则可能多达数十亿到数百亿个。越往芯片内层深入,其互联的数量会急剧增大。Chiplet是大芯片被切割成的小芯片,其间的互联自然不会少,经常一款Chiplet封装的硅转接板超过100K+的TSV,250K+的互联,这在传统封装设计中是难以想象的。

由于IO的增量化,Chiplet的设计也对EDA软件提出了新的挑战,Chiplet技术需要EDA工具从架构探索、芯片设计、物理及封装实现等提供全面支持,以在各个流程提供智能、优化的辅助,避免人为引入问题和错误。

Cadence、Synopsys、Siemens EDA(Mentor)等传统的集成电路EDA公司都相继推出支撑Chiplet集成的设计仿真验证工具。

注释:关于EDA工具

EDA,也被称为电子设计自动化,是一种电子设计工具,可用于帮助工程师进行电路设计,仿真和分析工作。它包括一系列的软件和工具,可以帮助工程师快速和有效地设计电路板和电路,并且还可以帮助他们预测电路的性能,确保电路能够正常工作。EDA工具也可用于进行功能验证和测试,以确保电路符合设计要求。总而言之,EDA是电子设计工程师在电路方面工作时非常有用的工具。

五、总结

Chiplet是一种实现模块化设计的方法,每个Chiplet通常负责处理器的一个功能模块。因此,Chiplet可以通过异质集成的方式来实现,即将不同材料或不同工艺制造的芯片集成在一起,构成一个完整的处理器模块。

同时,Chiplet也可以通过异构集成的方式来实现,即将不同类型的芯片集成在一起,构成一个完整的处理器模块。例如,可以将CPU、GPU和FPGA等不同类型的芯片集成在一起,构成一个完整的处理器模块。

总结一下,Chiplet带给集成技术的新变化就是:IP芯片化、集成异构化、集成异质化、IO增量化,我们称之为Chiplet技术带来的新“四化”。

参考资料:

Chiplet技术带来的新“四化” - 与非网 (eefocus.com)