内容:TCL语言(PT),静态时序分析基础(工艺库、STA环境、时序检查方法、多时钟等特殊时序分析),SDC(tcl设计约束)

CTS:clock tree systhesis

Tsu建立时间/Th保持时间

TCL置换:变量置换$ 命令置换[] 反斜杠置换

Slack:回路时序延迟值

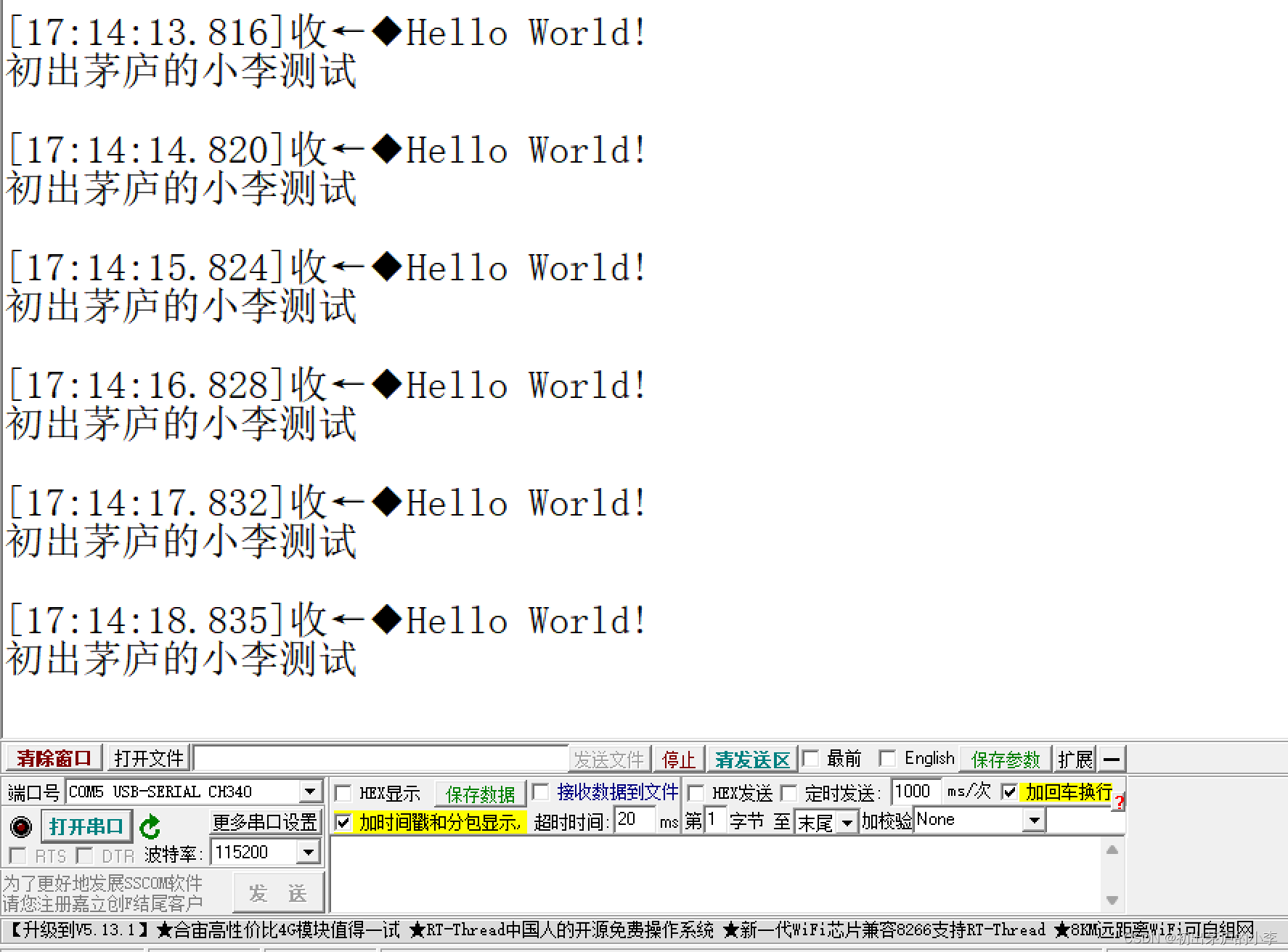

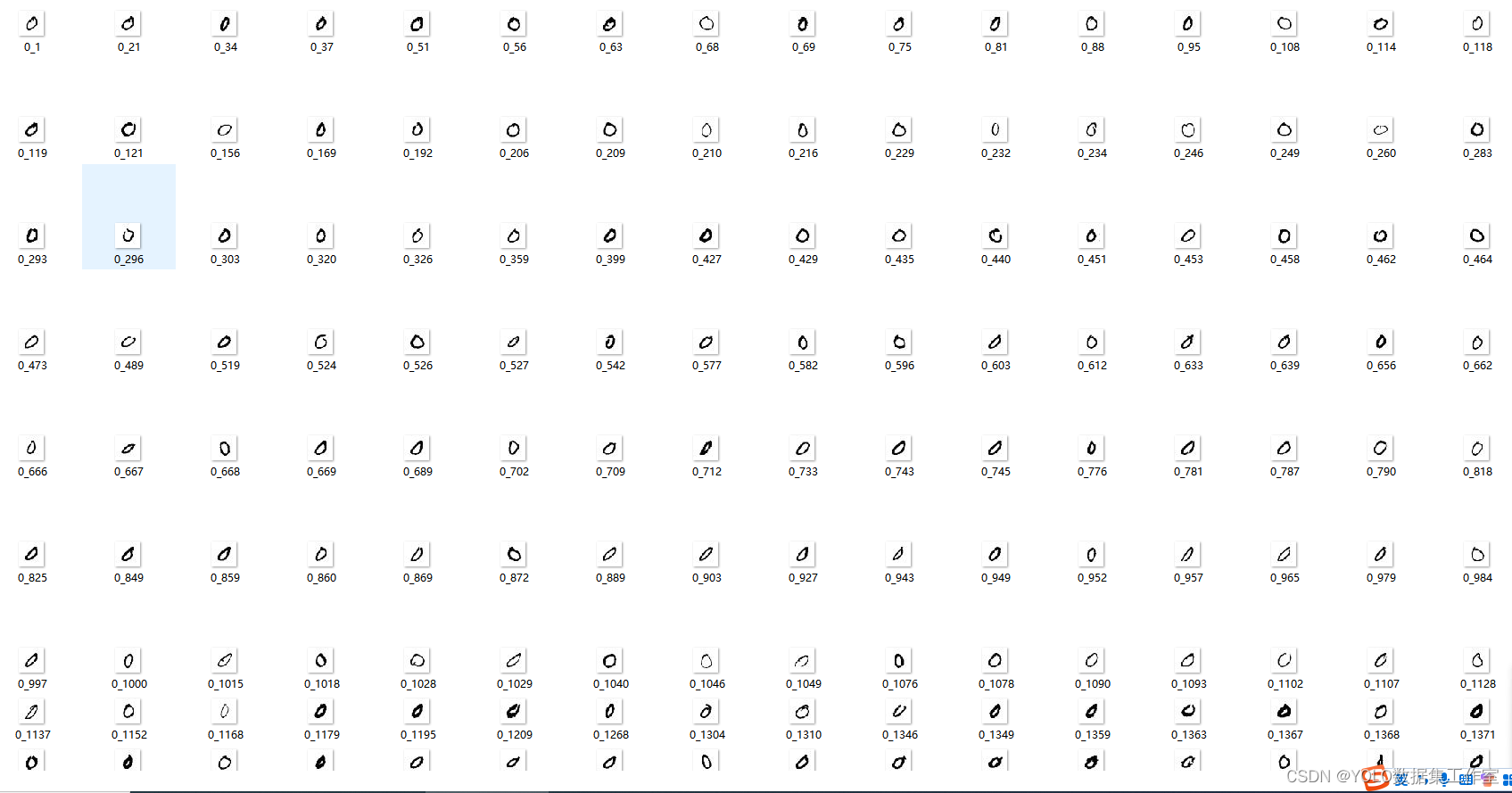

get_ports SPI

get_ports 所有ports

get_ports C C开头的ports

get_cells cellsname

get_cells 3

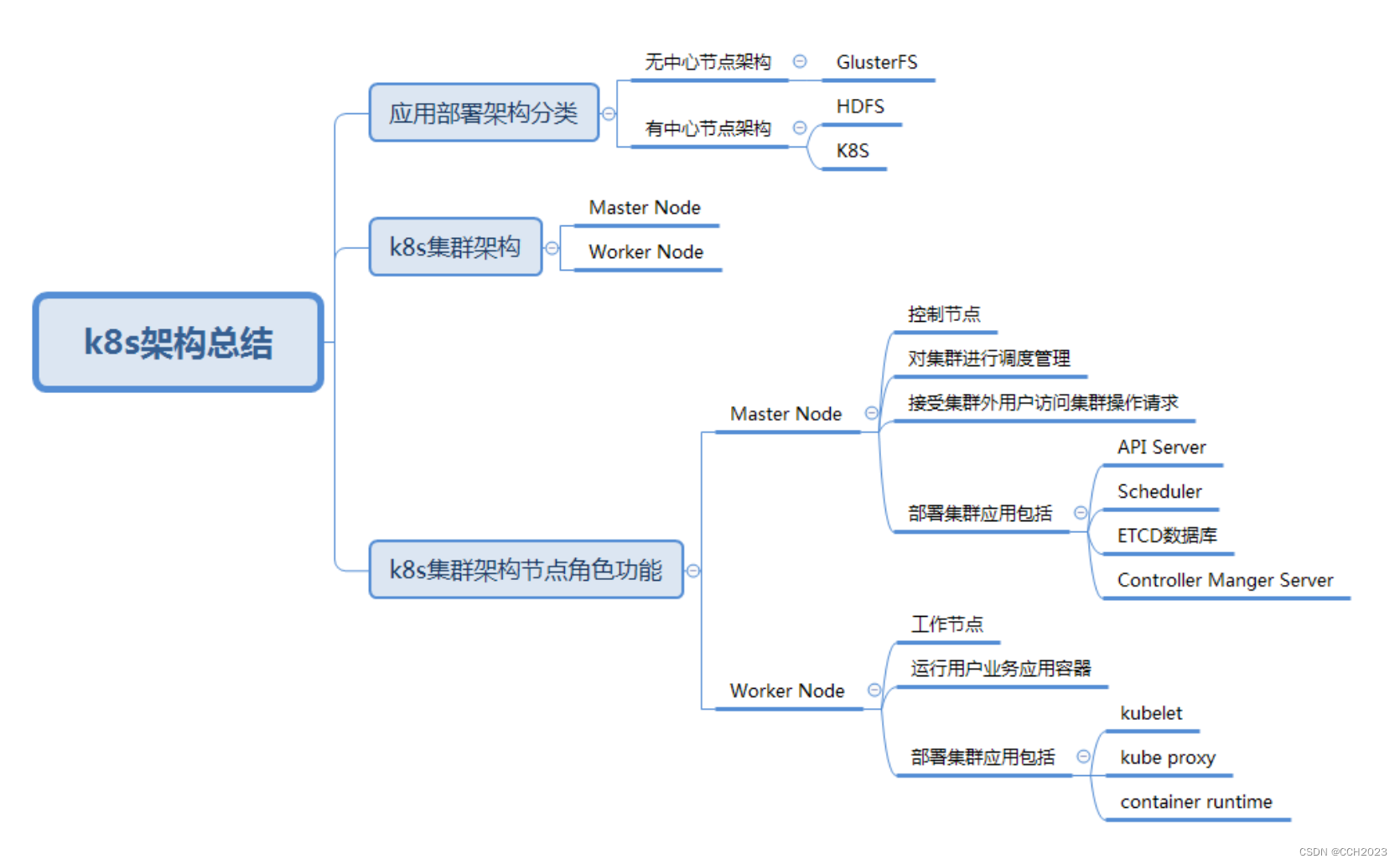

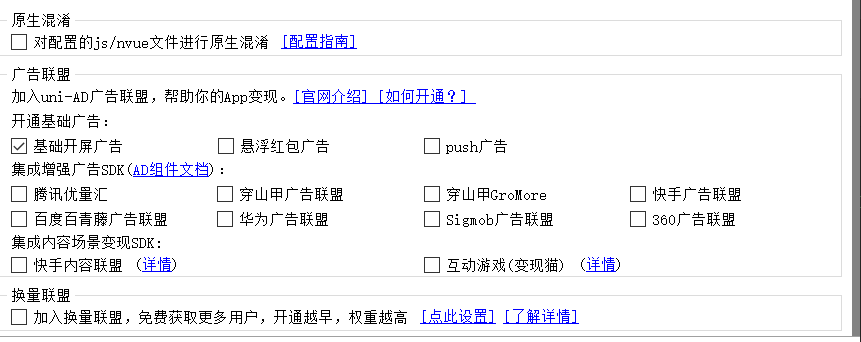

DC:design complier 逻辑综合 Flow流程

get_nets INV

llength [get_object_name [get_nets *]]net的个数

get_ports * -f "direction==in"所有方向是input的port

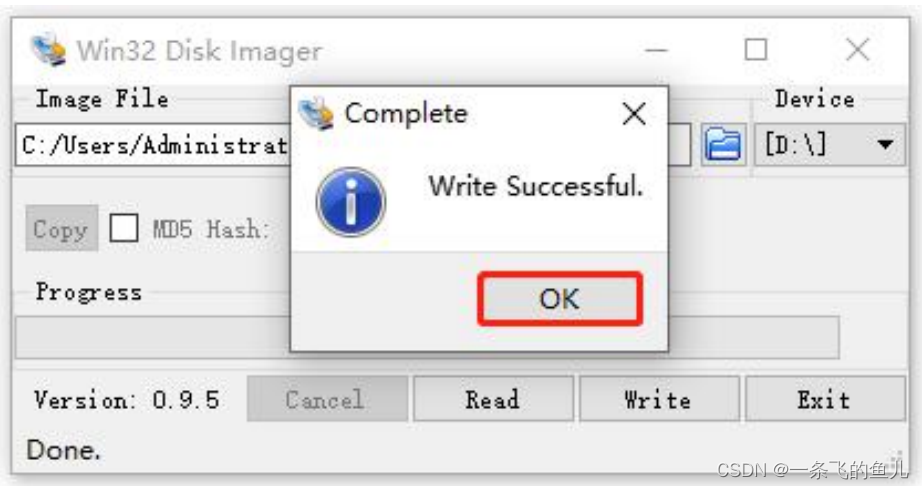

最终所有的约束都被写入script.tcl中,供DC读取,完成最终的逻辑综合过程

时序弧:连线延时和单元延时

两种起点:clock pin和input port

两种终点:data input pin(D触发器的D端)和output port

有四种组合方式

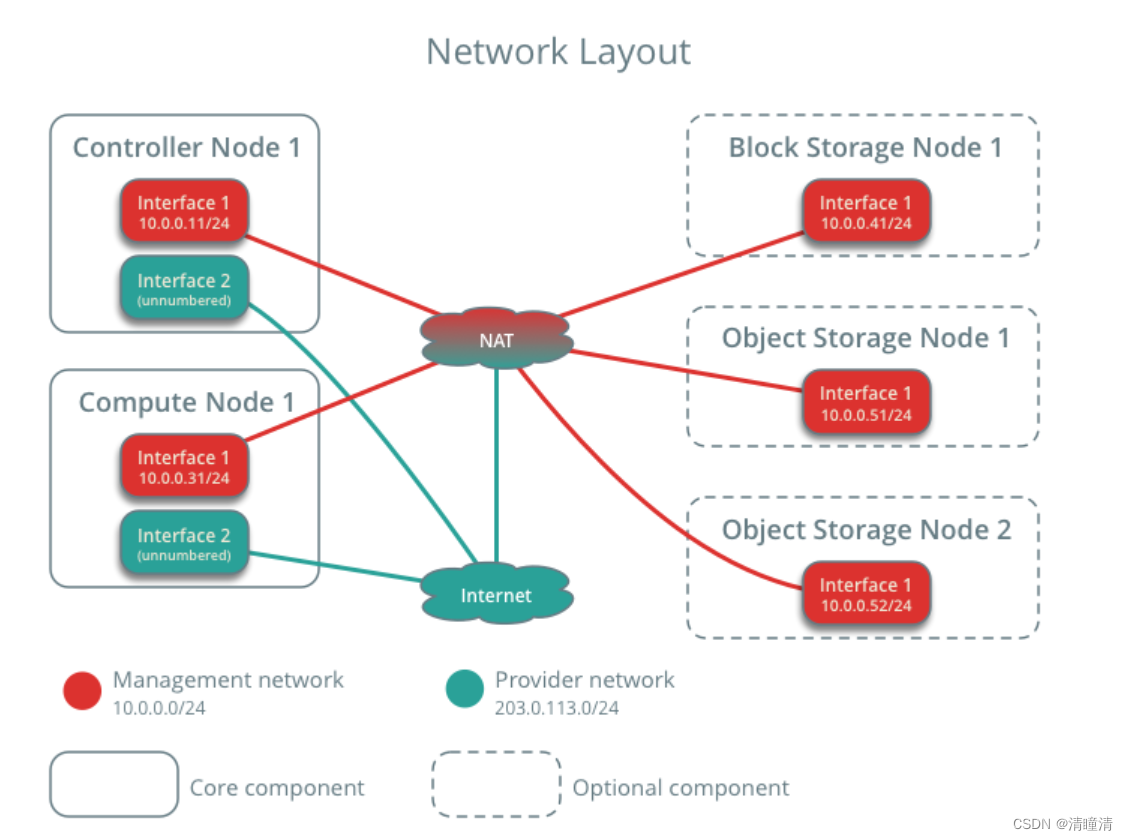

时钟域(全局异步,局部同步)

工作环境:PVT

最慢的条件检查setup,最快的条件检查hold

SS(低压高温)→setup

FF(高压低温)→hold

标准单元库

延迟模型:线性和非线性

线性延迟D=D0+D1S(输入传输时间)+D2C(输出负载电容)

非线性:高斯消元法,利用周围的四个点(插值)

30%到70%线性好,库里面是90%到10%

时序模型 组合逻辑和时序逻辑

线载模型

STA环境配置

时钟偏差 时钟抖动jitter 时钟延迟

latency:network latency和source latency

生成时钟 master clock和generated clock看情况定义时钟类型

约束输入路径和输出路径

时序组

set_drive 0 UCLK:理想化

DRC:set_max_transition set_max_capacitance

虚拟时钟

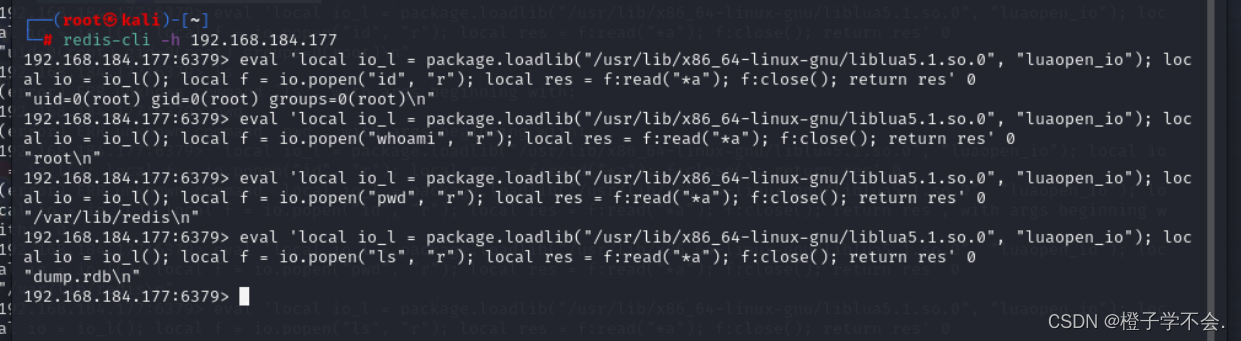

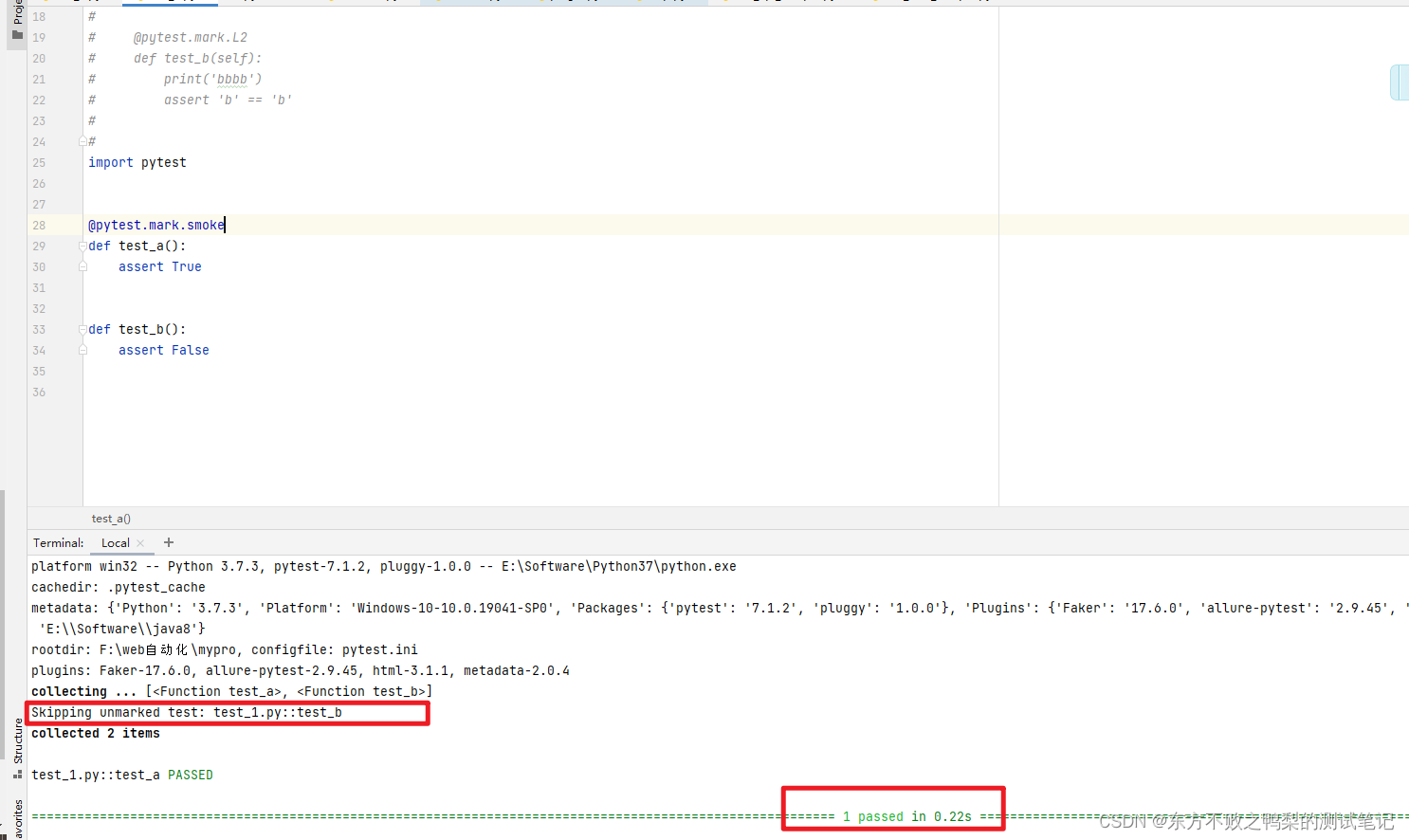

STA更精细化:set_case_analysis set_disable_timing set_false_path set_multicycle_path

异步无法进行STA

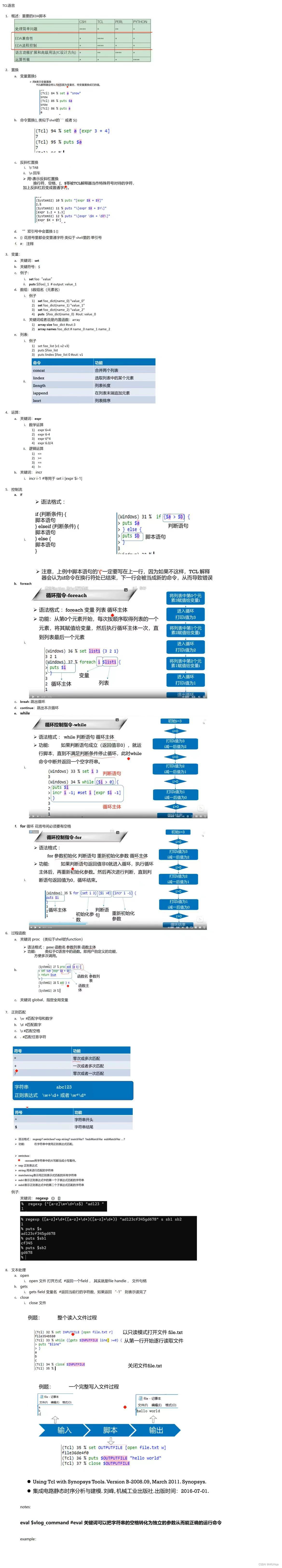

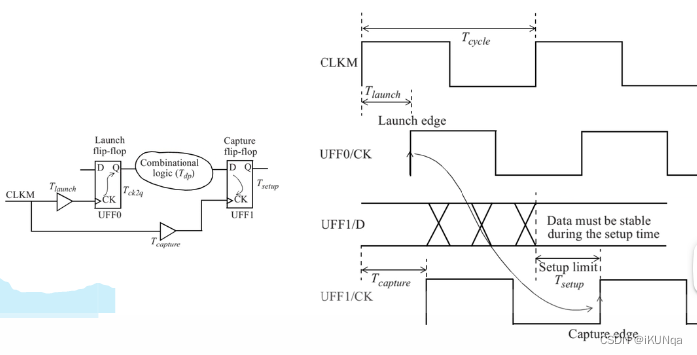

建立时间与保持时间检查

绝大多数时序路径:ck→D

setup:

Tlaunch+Tck2q+Tdp(max)<Tcapture+Tcycle-Tsetup

data required time>data arrival time满足

hold:

Tlaunch+Tck2q+Tdp(min)>Tcapture+Thold

特殊时序检查(同步)

同时钟:多周期:N setup /N-1 hold

半周期:setup紧hold松

伪路径

多时钟(multicycle):slow to fast -end/fast to slow -start