1.

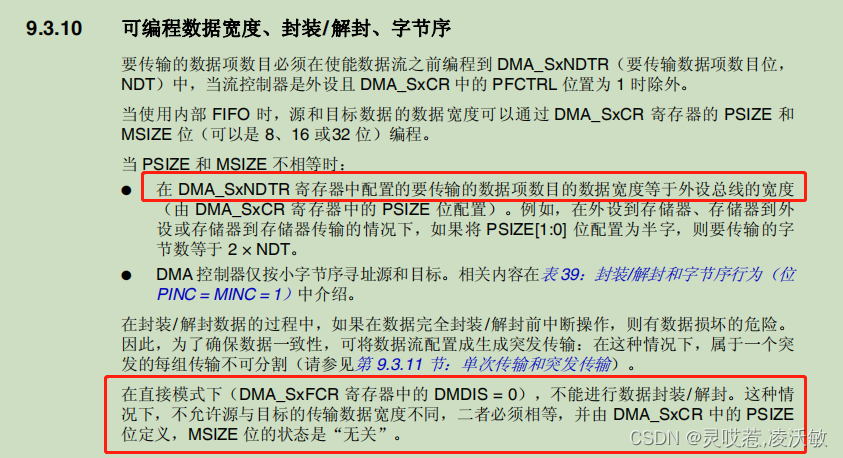

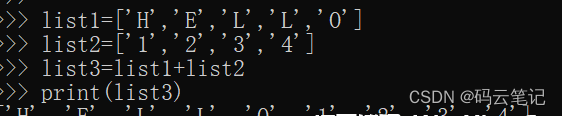

从以上截图信息可以看出:

1.当外设数据宽度和内存数据宽度不相等时,要传输的数据项数目的数据宽度由外设数据宽度确定;

2.在直接模式下(不使用FIFO),不能进行数据的封装/解封,且源数据宽度和目标数据宽度必须相等,且等于外设数据宽度(实际上此时内存数据宽度无效)

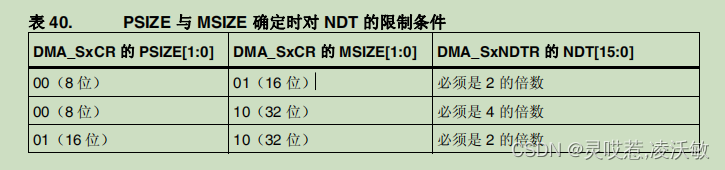

2.

即当PSIZE小于MSIZE时,NDTR必须是(MSIZE/PSIZE)的整数倍,很好理解,因为此时要传输的数据项数目的数据宽度由PSIZE确定,假设PSIZE是8位而MSIZE是16位,然后此时NDTR是9的话,就表示总共只需要传输9字节的数据,那对于memory那边来说的话就会少一个字节。

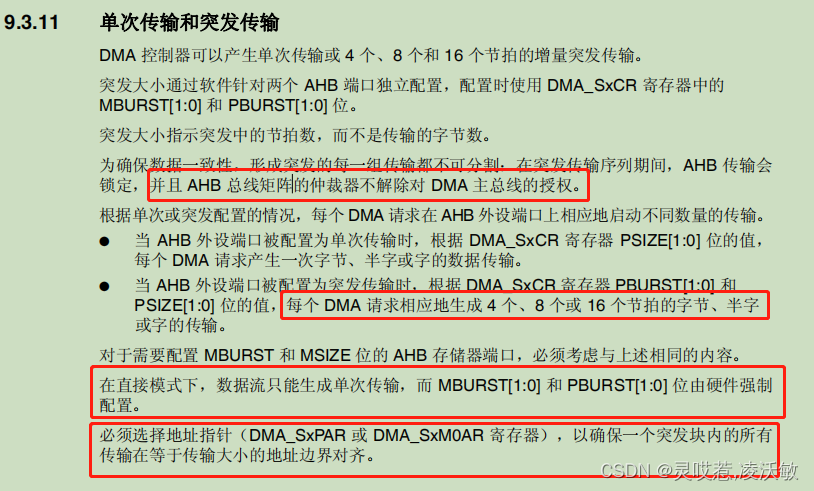

3.

1.突发传输的意思就是每个DMA请求传输多少次,比如DMA_PeripheralBurst_INC4(外设突发4次传输)则表示每个DMA请求传输4次,每次的数据大小由PSIZE决定;突发传输的数据会暂存在FIFO中;

2.在直接模式下(不使用FIFO)突发传输的配置无效,只能进行单次传输;

3.如果使用了突发传输,则相应的字节对齐要倍乘,如PSIZE为字节的话,对于单次传输传输地址只需要4字节对齐就行,如果是突发4次传输,则需要16字节对齐;

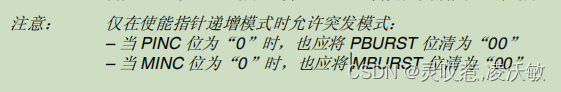

4.如果内存地址不递增,则内存突发传输位应该为0;如果外设地址不递增,则外设突发传输位应该为0;

4.总结:FIFO的作用

1.用于PSIZE和MZISE不同时作数据的封装/解封;

2.用于配置了突发传输时暂存数据用;

所以,当FIFO关闭时候,不能做数据的封装/解封,PSIZE和MSIZE也就需要一样;并且不能配置为突发传输(硬件强制为单次传输);

5.突发大小与数据大小的乘积不得大于FIFO大小(FIFO的最大大小为4字),即若突发大小是4,数据大小是字,那么此时应该开启全部的FIFO;若数据大小是半字,则应该开启至少1/2的FIFO;

6.貌似只有SDIO外设能够向DMA发出结束传输指令;

7.每次DMA传输最多只能传65535个数据项(注意不是字节),所以每次最多可以传输65535*4字节的数据;

8.每个DMA下面有8个数据流,每个数据流下有8个通道;但是每个数据流同时只能配置为采集一个通道的数据;每个数据流都有4个优先级可配置,当两个优先级相同的数据流产生DMA请求时优先响应数据流号低的(如数据流2优先与数据流3);

9.当使能FIFO时,只有当存入FIFO的数据量达到FIFO的阈值级别时才会将数据传输到目标地址,如FIFO的阈值级别时1/2FIFO(2个字),则只有在存入FIFO的数据量达到8字节时才会触发DMA将数据传输到目标地址;

10.在传输方向为存储器到存储器时,使用的是DMA流控,由软件触发DMA传输,每次传输的字节数由NDTR和PSIZE决定(NDTR*PSIZE);这种模式必须使用FIFO,并且只有DMA2能够使用这种模式;此时拷贝的源地址应该写到外设地址寄存器处,目的地址写到内存地址寄存器处。

![[附源码]Nodejs计算机毕业设计基于web技术的米其林轮胎管理系统Express(程序+LW)](https://img-blog.csdnimg.cn/6efdff7c0e0940d0aac0f050ebd28860.png)