verilog典型电路设计之FIR滤波器的设计

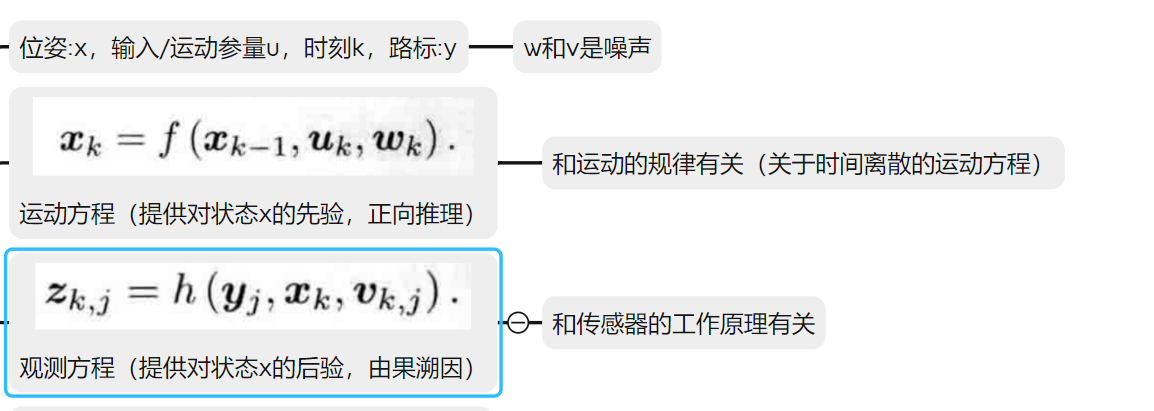

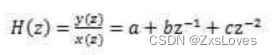

我们常用的FIR滤波器称为有限冲激响应 是一种常用的数字滤波器 ,采用对已输入样值的加权和来形成它的输出。

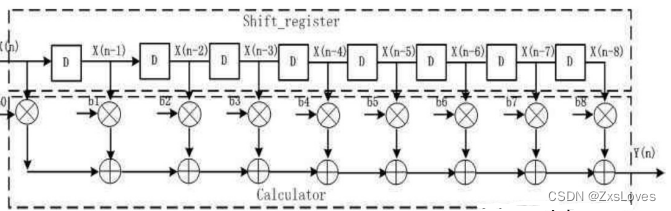

对于输入序列X[n] 的FIR滤波器可用下图所示的结构示意图来表示,其中X[n] 是输入数据流。各级的输入连接和输出连接被称为抽头,并且系数(b0,b1,…,bn)被称为抽头系数。一个M阶的FIR滤波器将会有M+1个抽头。通过移位寄存器用每个时钟边沿n(时钟下标)处的数据流采样值乘以抽头系数,并将它们加起来形成输出Y[n] 。

下面是verilog代码

module FIR (Data_out,Data_in,clock,reset);

output[9:0] Data_out;

input[3:0] Data_in;

input clock, reset;

wire[9:0] Data_out;

wire [3:0]samples_0,samples_1,samples_2,samples_3,samples_4,samples_5,samples_6,samples_7,samples_8;

shift_register U1(.Data_in(Data_in),.clock(clock),.reset(reset),.samples_o(samples_o),.samples_1(samples_1),.samples_2(samples_2),.samples_3(samples_3),.samples_4(samples_4),.samples_5(samples_5),.samples_6(samples_6),.samples_7(samples_7),.samples_8(samples_8));

caculatorU2(.samples_0(samples_O),.samples_1(samples_1),.samples_2(samples_2),.samples_3(samples_3),.samples_4(samples_4),.samples_5(samples_5),.samples_6(samples_6),.samples_7(samples_7),.samples_8(samples_8),.Data_out(Data_out));

endmodule

module shift_register(Data_in,clock,reset,samples_0,samples_1,samples_2,samples_3,samples_4,samples_5,samples_6,samples_7,samples_8);

input [3:0] Data_in;

input clock,reset;

output [3:0] samples_0,samples_1,samples_2,samples_3,samples_4,samples_5,samples_6,samples_7,samples_8;

reg [3:0] samples_0,samples_1,samples_2,samples_3,samples_4,samples_5,samples_6,samples_7,samples_8;

always@(posedge clock or negedge reset)

begin

if(reset)begin

samples_O<=4'b0;

samples_1<=4'b0;

samples_2<=4'b0;

samples_3<=4'b0;

samples_4<=4'b0;

samples_5<=4'b0;

samples_6<=4'b0;

samples_7<=4'b0;

samples_8<=4'b0;

end

else

begin

samples_0<=Data_in;

samples_1<=samples_0;

samples_2<=samples_1;

samples_3<=samples_2;

samples_4<=samples_3;

samples_5<=samples_4;

samples_6<=samples_5;

samples_7<=samples_6;

samples_8<=samples_7;

end

end

endmodule

module caculator(samples_0,samples_1,samples_2,samples_3,samples_4,samples_5,samples_6,samples_7,samples_8,Data_out);

input [3:0] samples_0,samples_1,samples_2,samples_3,samples_4,samples_5,samples_6,samples_7,samples_8;

output [9:0] Data_out;

wire [9:0] Data_out;

wire [3:0] out_tmp_1,out_tmp_2,out_tmp_3,out_tmp_4,out_tmp_5;wire [7:0] out1,out2,out3,out4,out5;

parameter b0=4'b0010;

parameter b1=4'b0011;

parameter b2=4'b0110;

parameter b3=4'b1010;

parameter b4=4'b1100;

mul_addtree U1(.mul_a(b0),.mul_b(out_tmp_1),.mul_out(out1));

mul_addtree U2(.mul_a(b1),.mul_b(out_tmp_2),.mul_out(out2));

mul_addtree U3(.mul_a(b2),.mul_b(out_tmp_3),.mul_out(out3));

mul_addtree U4(.mul_a(b3),.mul_b(out_tmp_4),.mul_out(out4));

mul_addtree U5(.mul_a(b4),..mul_b(samples_4),.mul_out(out5));

assign out_tmp_1=samples_O+samples_8;

assign out_tmp_2=samples_1+samples_7;

assign out_tmp_3=samples_2+samples_6;

assign out_tmp_4=samples_3+samples_5;

assign Data_out=out1+out2+out3+out4+out5;

endmodule

下面是testbench

module FIR_tb;

reg clock,reset;

reg [3:0] Data_in;

wire [9:0] Data_out;

FIRU1(.Data_out(Data_out),.Data_in(Data_in),.clock(clock),.reset(reset);

initial

begin

Data_in=0;

clock=0;

reset=1;

#10 reset=0;

end

always

begin

#5 clock<=~clock;

#5 Data_in<=Data_in+1;

end

endmodule