前一篇博客我们提到在线调试的时候, 可执行文件只要烧进板子,程序它就会自己跑起来,不会等你点

这个按钮,它才开始跑。我们测试的模块中,里面可能有几个我们关心的信号,它会在程序刚运行很短的时间内发生状态跳变。 当我们打算去捕获它的状态变化的时候,这个时候程序已经跑过了,这导致我们无法抓取到。那这个时候我们应该怎么办呢? 引入VIO这个工具,用VIO的输出信号作为我们测试模块的使能信号,这样我们就能控制待测试的模块什么时候运行。

VIO是个特别简单的IP核,丝毫不用有畏难情绪。

1 VIO是什么

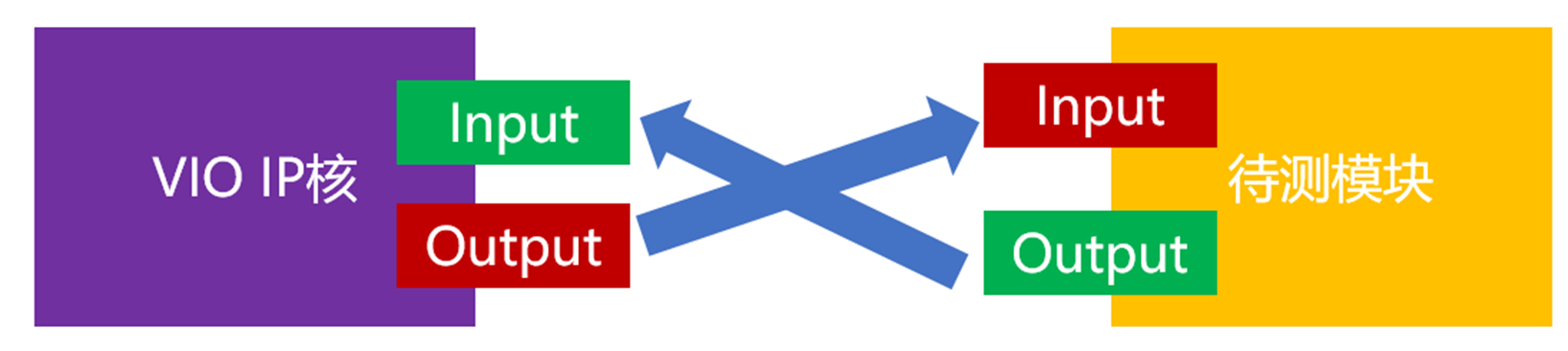

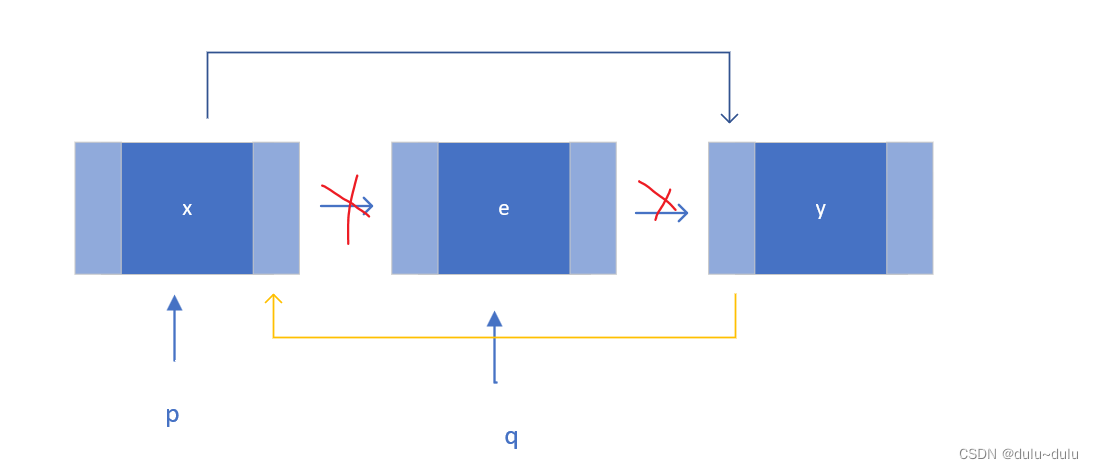

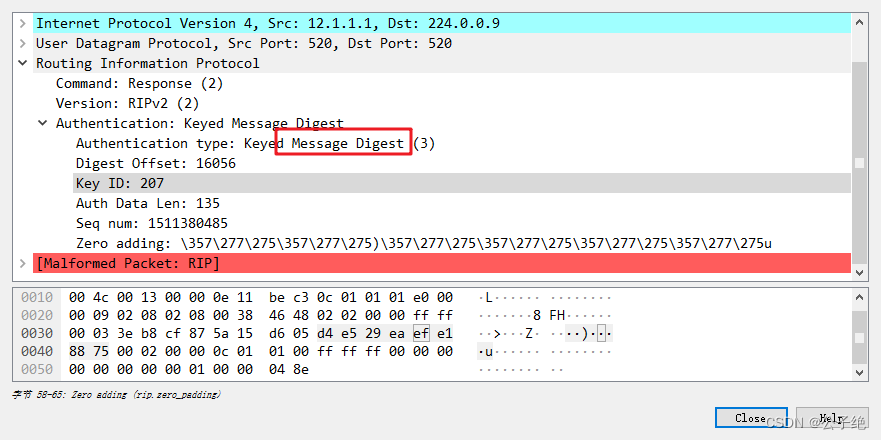

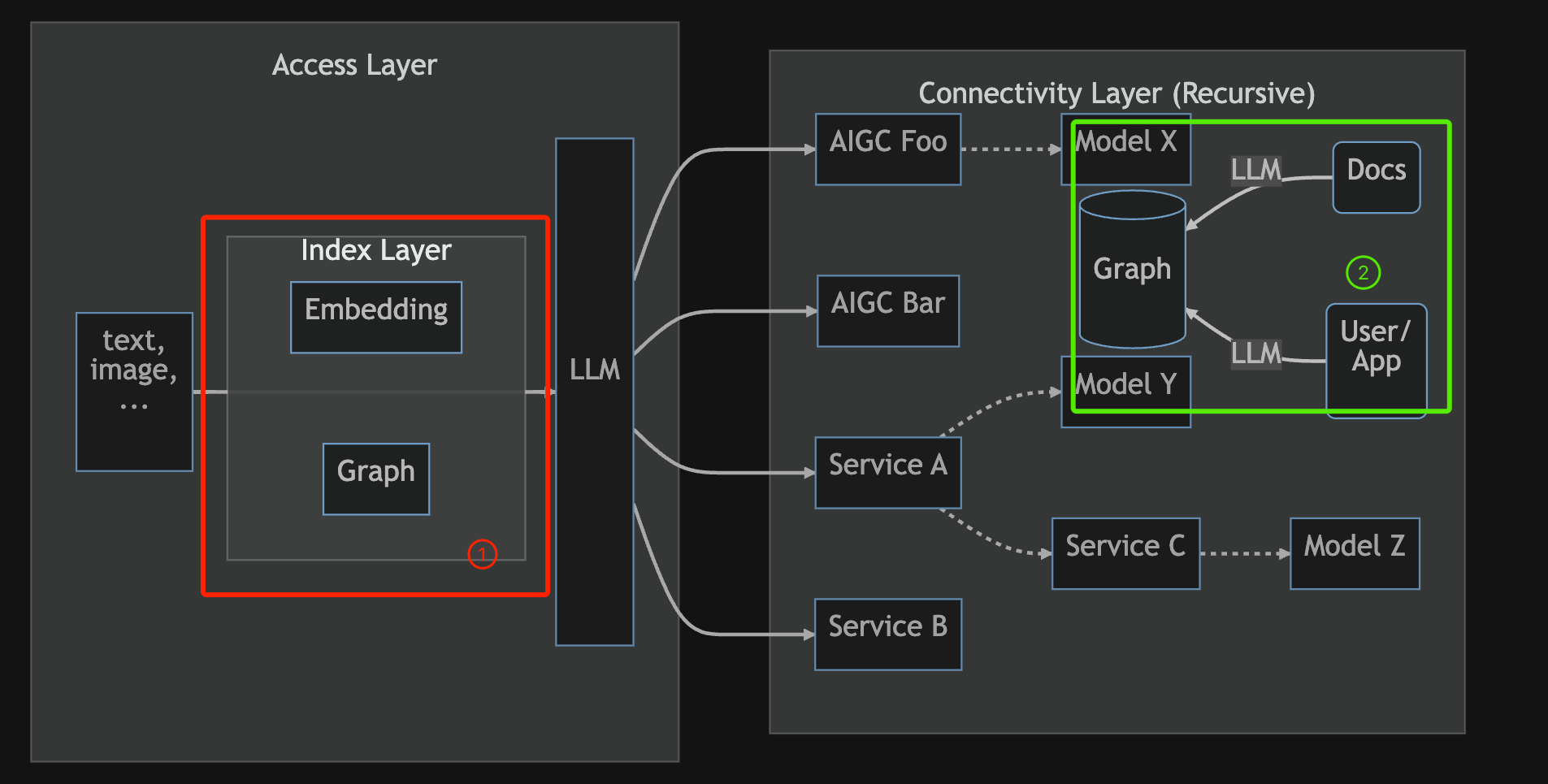

VIO是虚拟输入/输出(Virtual Input/Output),可以实时监测和驱动FPGA内部信号。 在线调试的时候,Vivado会提供一个VIO的界面,你可以修改VIO对待测模块的输出,也可以监测待测模块对VIO的输入。VIO和待测模块的信号如下图所示,就行串口通信一样,你的Tx要接到我的Rx,

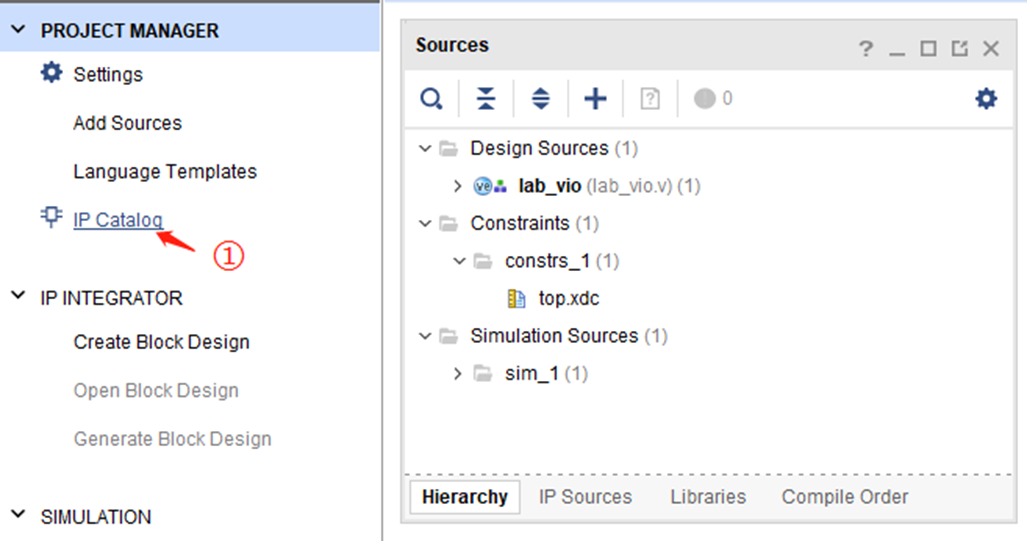

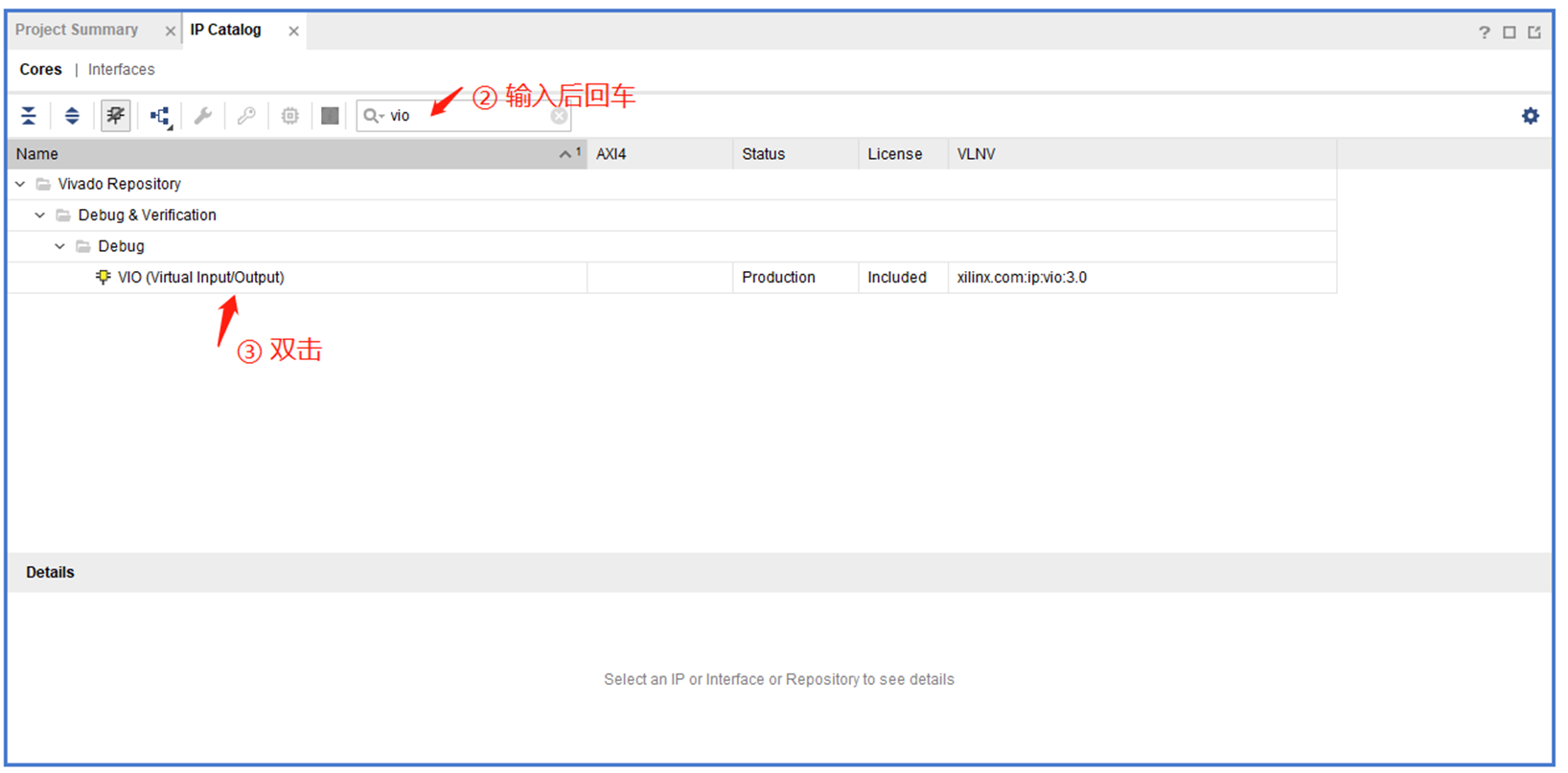

2 VIO IP 配置

截图警告!

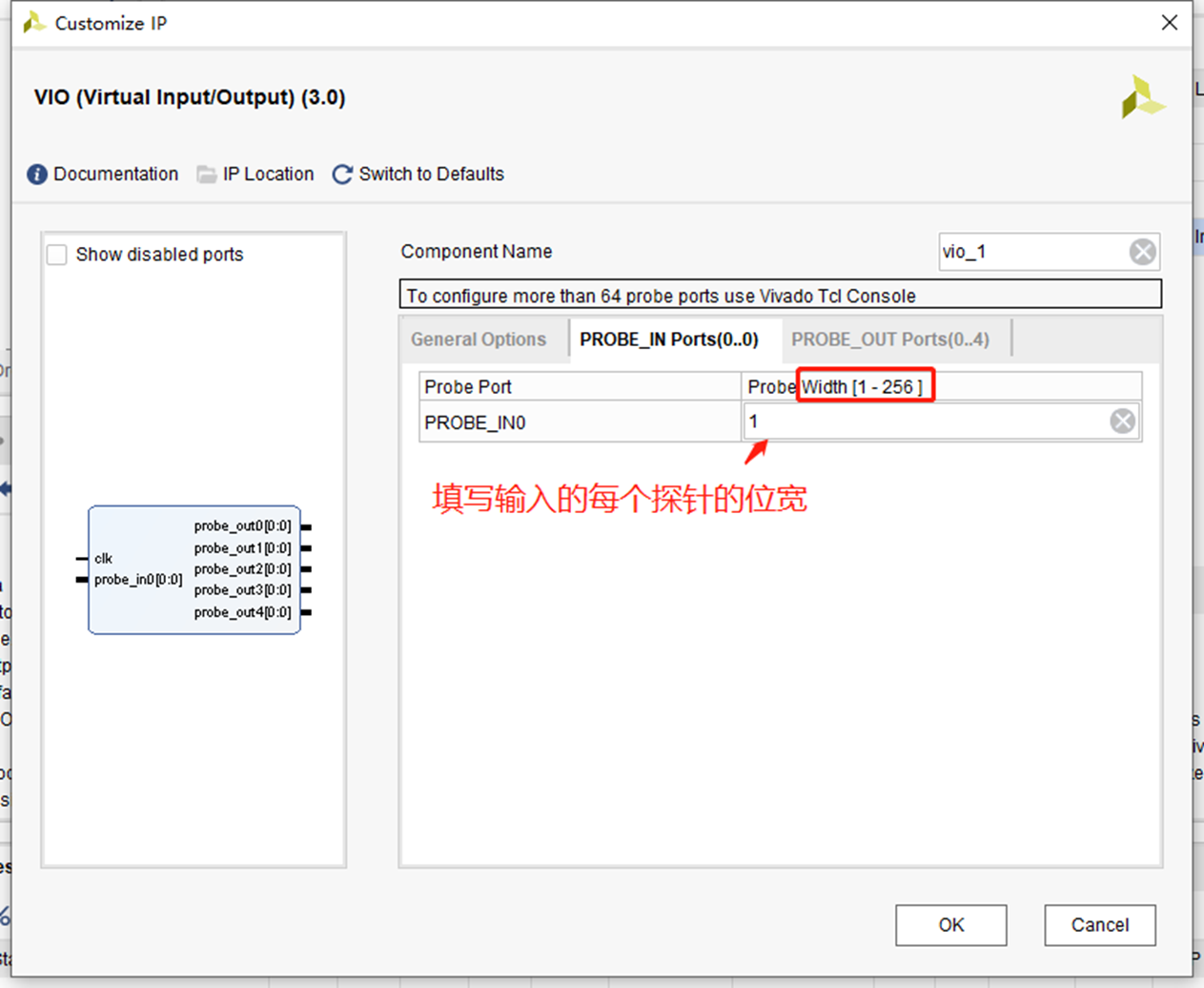

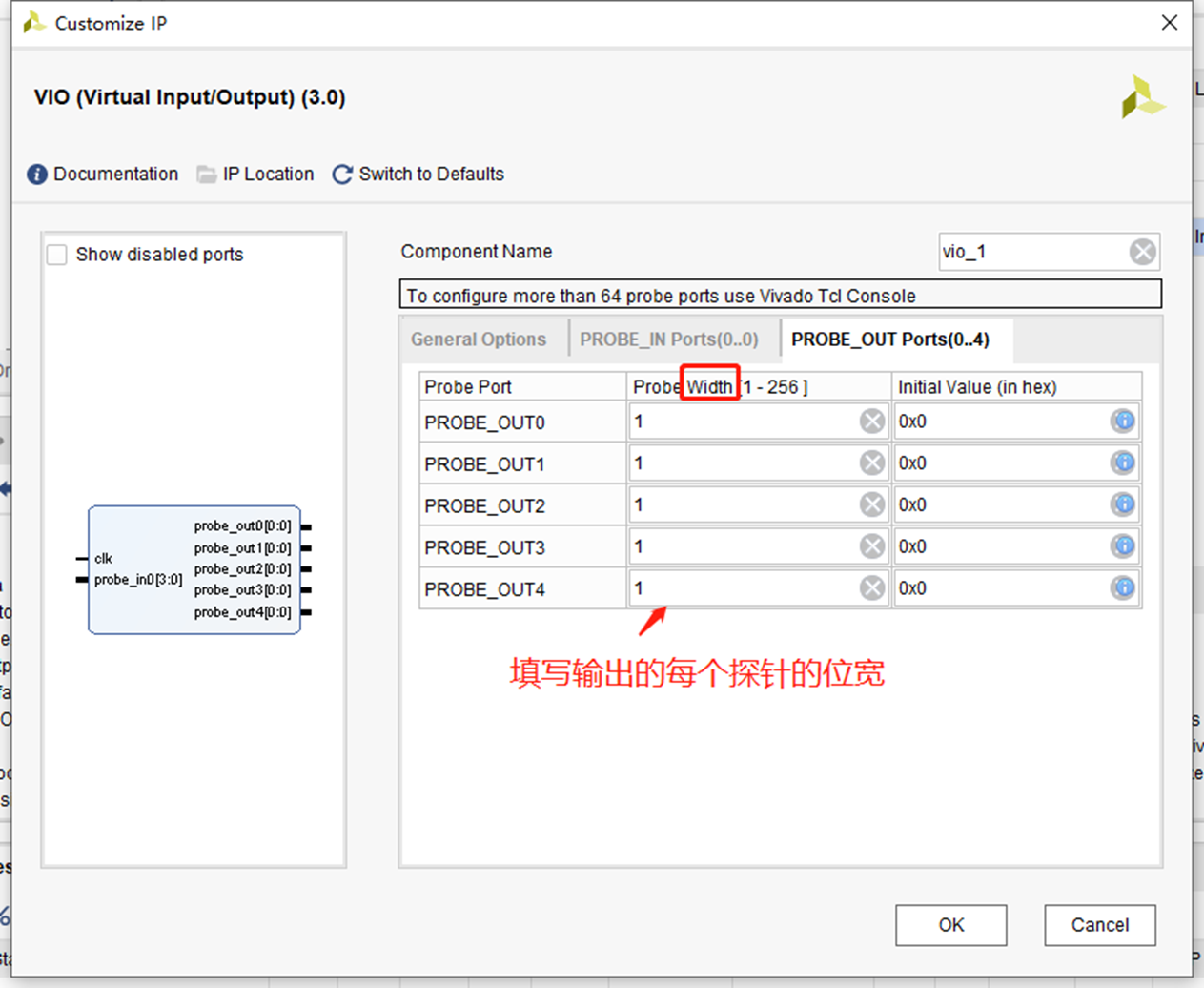

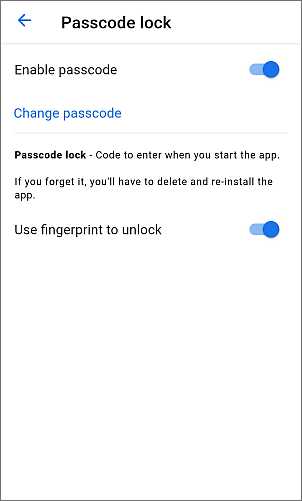

我对下面这个截图稍微补充一下哈, 截图只是在介绍这个东西是什么,而我们的VIO例程里,这输入探针数量是1,输出探针数量是5。 IP核名称是vio_0。

我对下面这个截图稍微补充一下哈, 截图只是在介绍这个东西是什么,而我们的VIO例程里,这输入探针位宽是4。

我对下面这个截图稍微补充一下哈, 截图只是在介绍这个东西是什么,而我们的VIO例程里,这5个输出探针位宽是2。

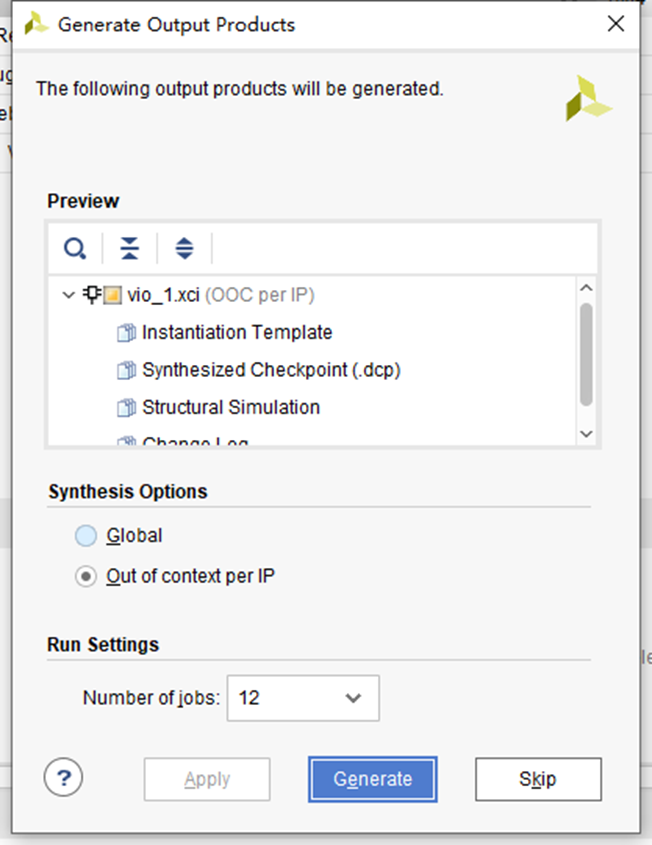

Ok之后直接Generate

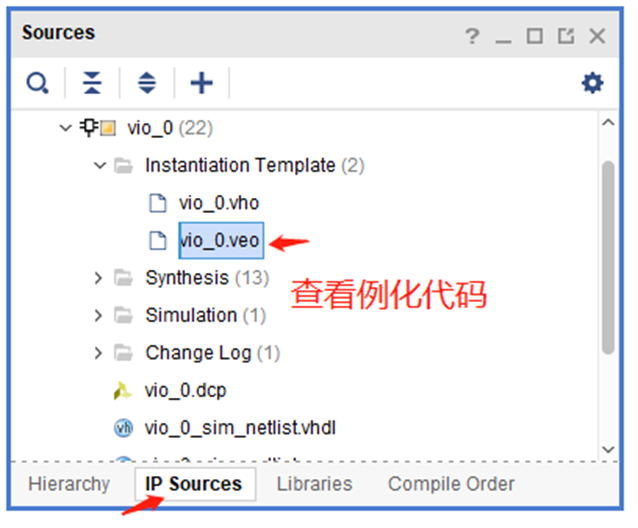

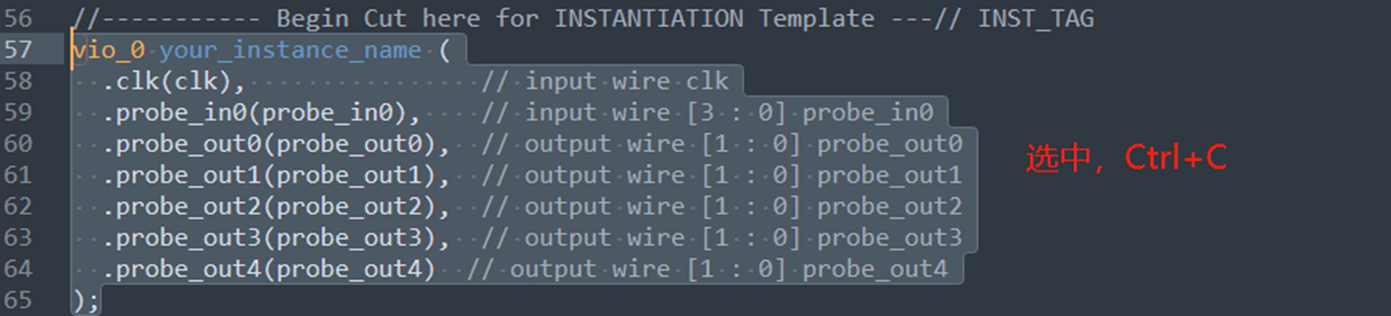

IP核生成完了之后,都要去抄一下怎么例化。

3 VIO测试用例:4选1-选择器

`timescale 1ns / 1ps

module lab_vio(

input wire clk

);

reg [3:0] out; // 待测模块的输出 VIO的输入

wire [1:0] a, b, c, d; // VIO的输出 待测模块的输入

wire [1:0] sel; // VIO的输出 待测模块的输入

always @(*) begin

case(sel)

2'b00: out <= a;

2'b01: out <= b;

2'b10: out <= c;

2'b11: out <= d;

default: out <= 2'bx;

endcase

end

vio_0 vio_0_inst (

.clk(clk), // input wire clk

.probe_in0(out), // input wire [3 : 0] probe_in0

.probe_out0(a), // output wire [1 : 0] probe_out0

.probe_out1(b), // output wire [1 : 0] probe_out1

.probe_out2(c), // output wire [1 : 0] probe_out2

.probe_out3(d), // output wire [1 : 0] probe_out3

.probe_out4(sel) // output wire [1 : 0] probe_out4

);

endmodule

管脚约束代码,我们只用到了clk

create_clock -period 20.000 [get_ports clk]

set_property PACKAGE_PIN N18 [get_ports clk]

set_property IOSTANDARD LVCMOS33 [get_ports clk]4 在线调试

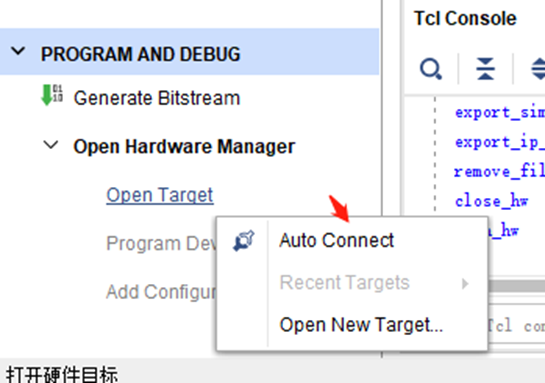

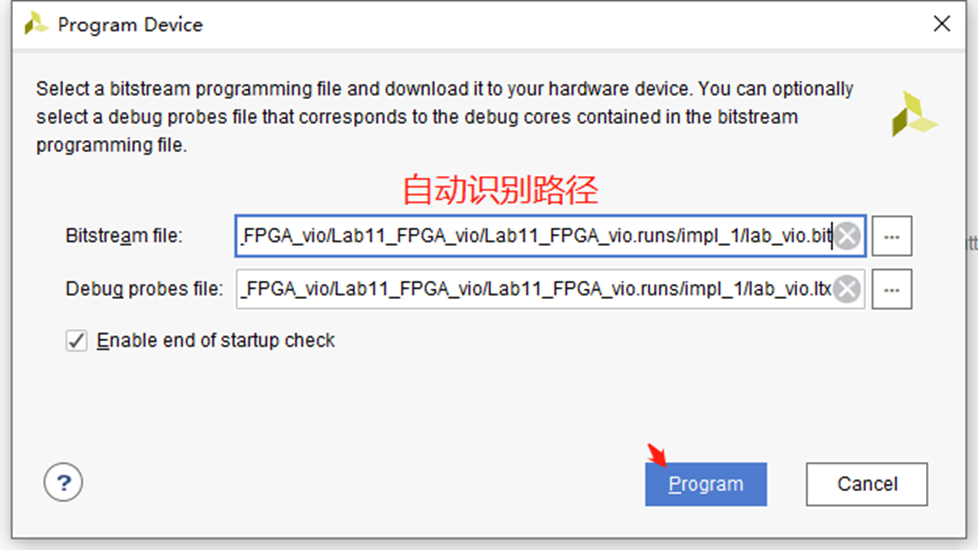

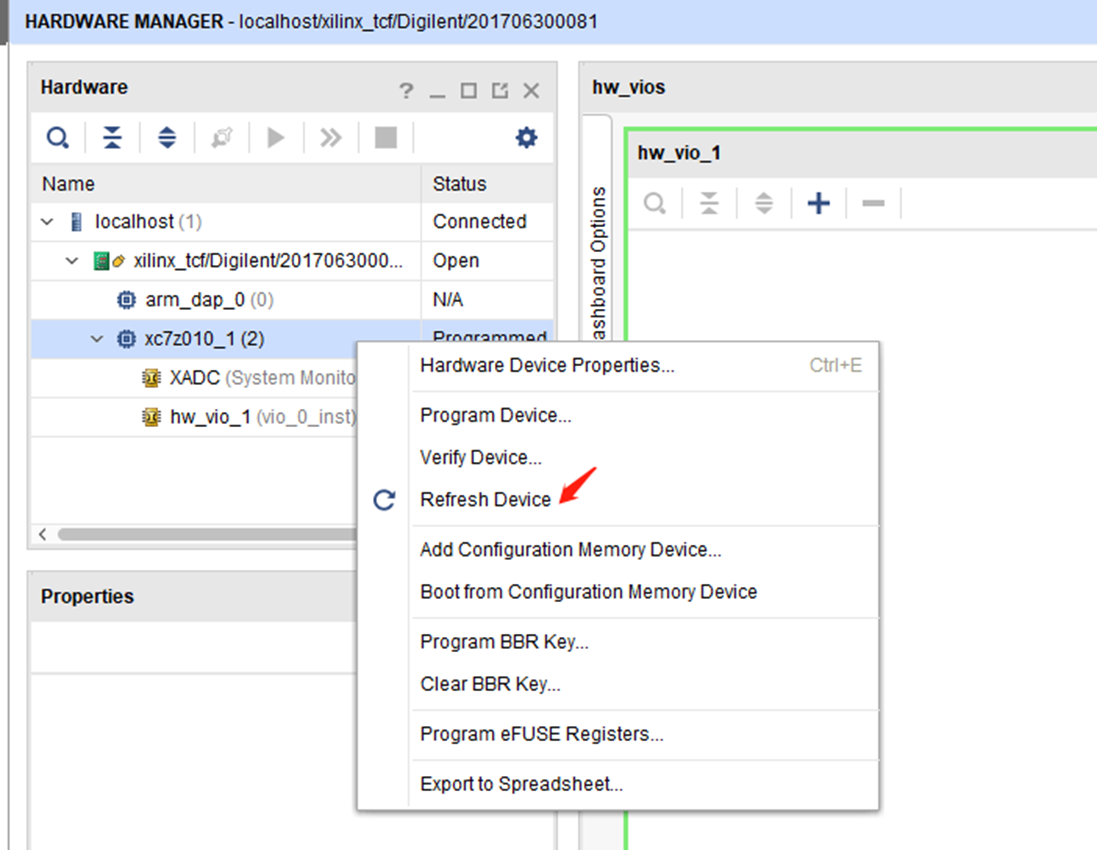

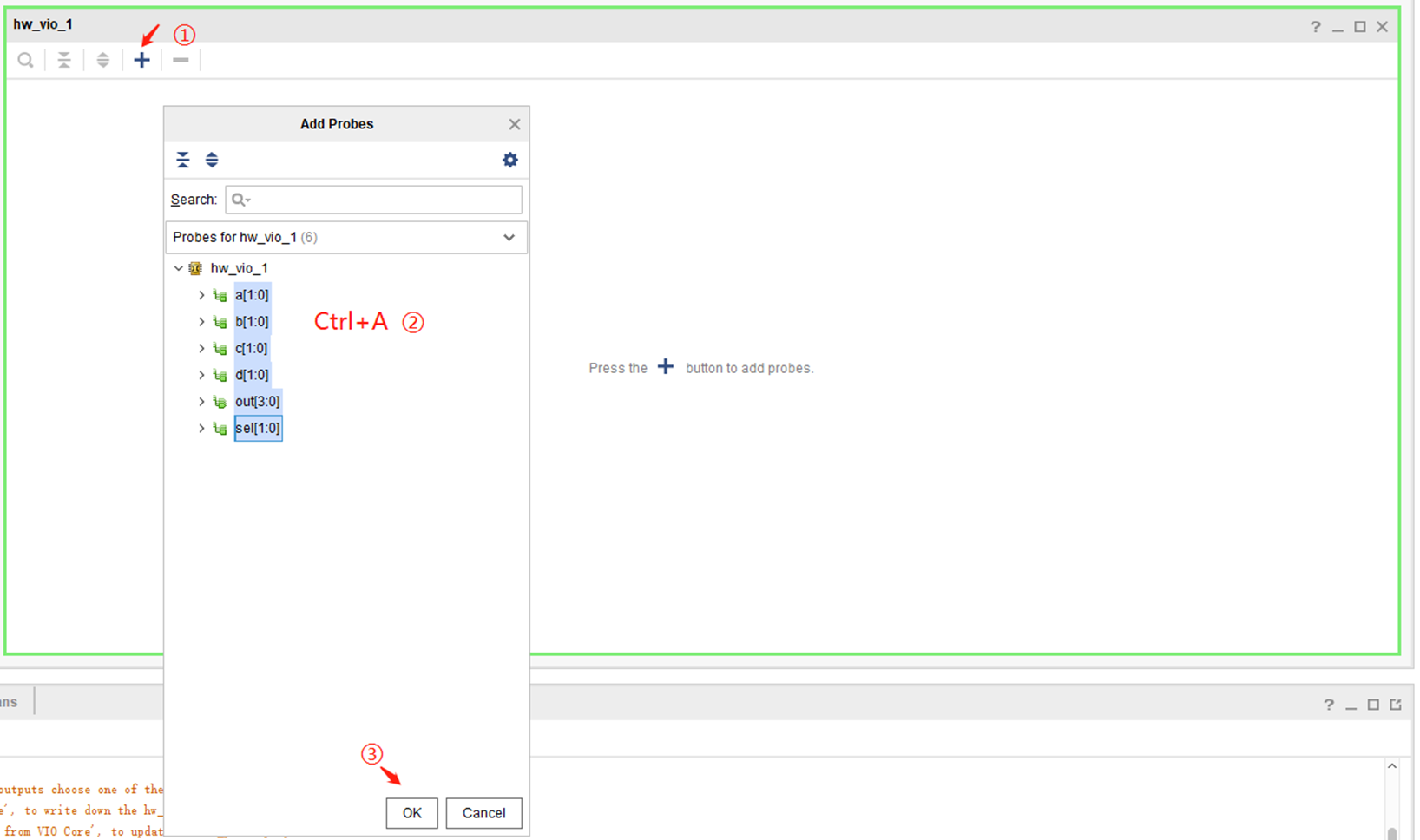

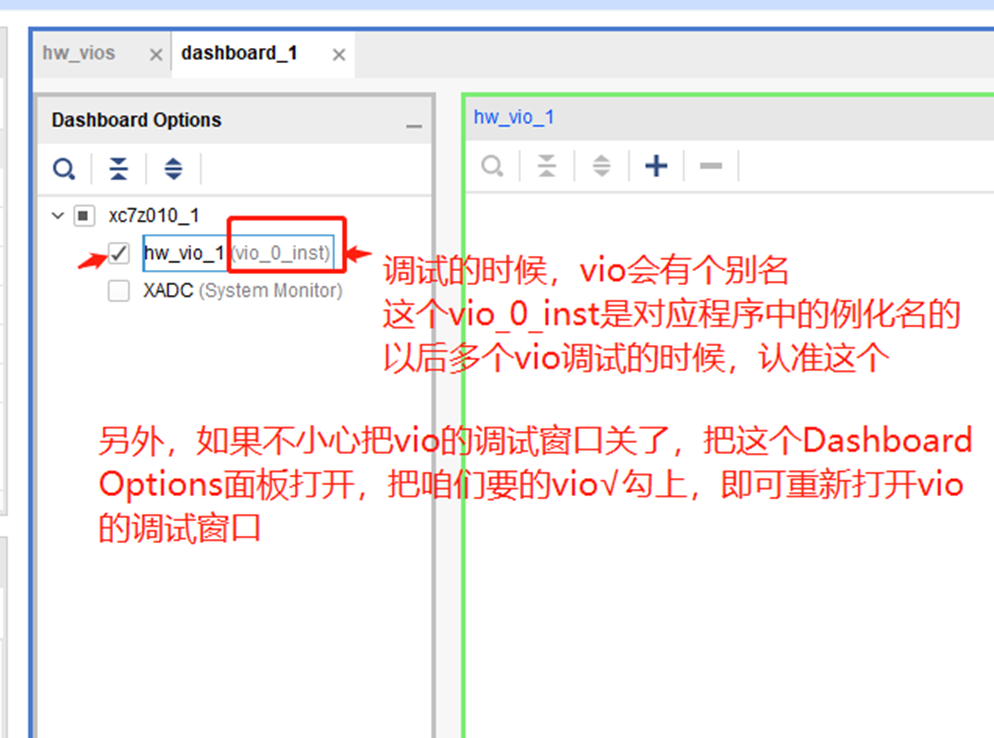

截图警告!

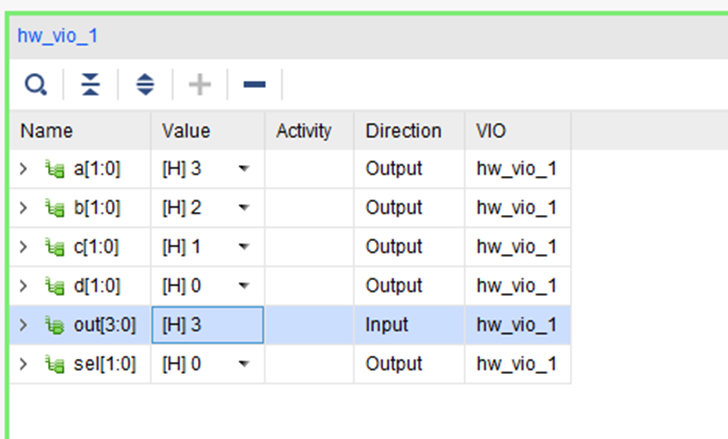

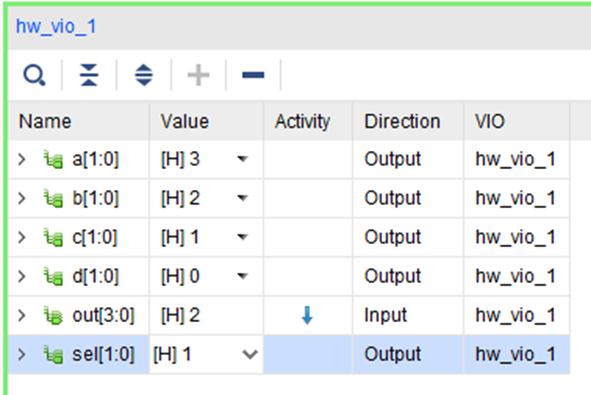

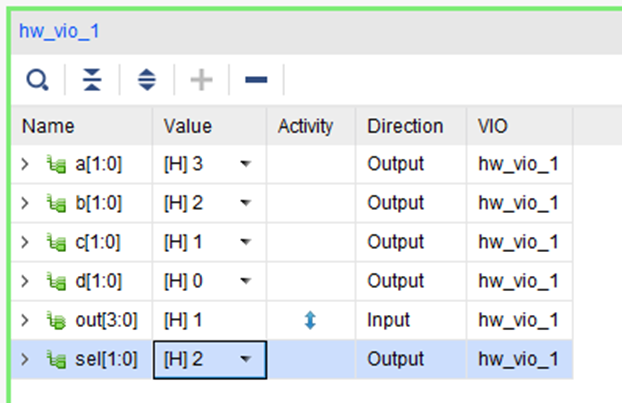

假设我设置 a b c d 分别为3 2 1 0, 然后分别设置sel为0 1 2 3,检测out的变化

|  |

|  |

通过以上的小实验呢,我们就算是基本掌握VIO的用法了,是不是很简单呢?

参考文献

Vivado调用VIO核_vio vivado_素年锦什的博客-CSDN博客

![[PyTorch][chapter 50][自定义网络 ResNet18]](https://img-blog.csdnimg.cn/185f52e9161c48079ecbf9670ae1c4e3.png)