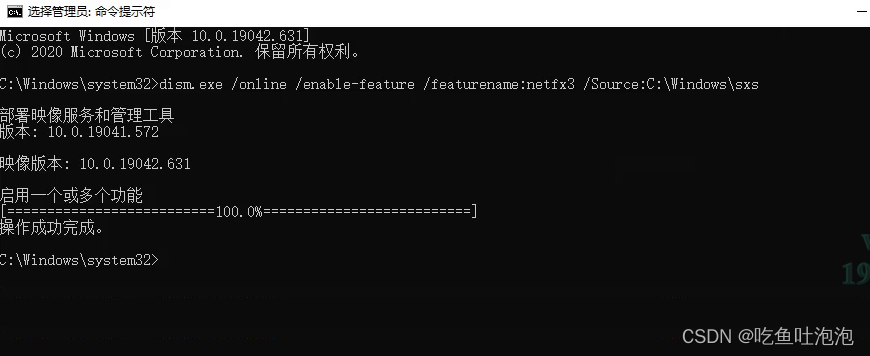

verilog典型电路设计之复数乘法器

典型电路设计之复数乘法器

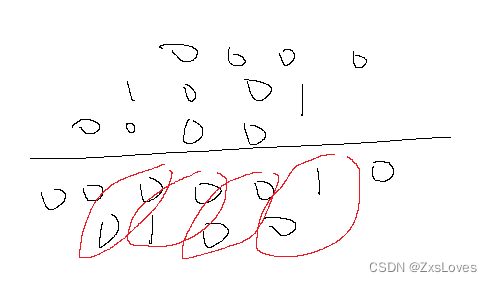

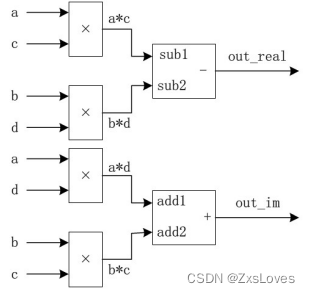

复数乘法的算法是: 设复数x=a+bi ; y=c+di; 则复数乘法结果 x.y=(a+bi)(c+di)=(ac-bd) +i(ad+bc)

复数乘法器 我们可以将复数x y 的实部与虚部相乘,减去 x与y的虚部相乘 得到输出结果的实部 就是ac-bd 同理我们得到结果的虚部是 ad+bc

其实这里的使用更多的是用在了数学的技巧上了

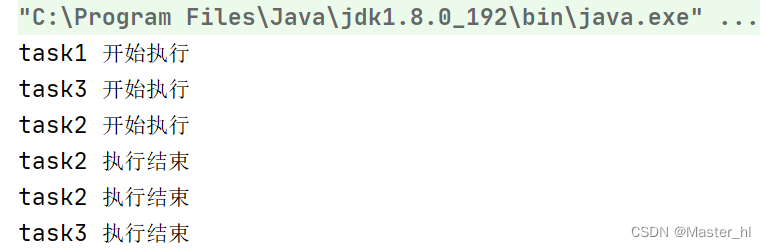

我们下面展示代码 更多的也是 调用4次乘法器 然后直接输出结果

下面是复数乘法器的一般性代码

module complex(a,b,c,d,out_real,out_im);

input [3:0]a,b,c,d;

output [8:0] out_real,out_im;

wire [7:0] sub1,sub2,add1,add2;

wallace U1(.x(a)..y(c),.out(sub1));

wallace U2(.x(b)..y(d),.out(sub2));

wallace U3(.x(a),..y(d),.out(add1));

wallace U4(.x(b)..y(c),.out(add2));

assign out_real=sub1-sub2;

assign out_im=add1+add2;

endmodule