与、或、与非、或非、异或门、三态门、OD门(OC门)和传输门等的结构与使用

逻辑门是基于半导体器件形成的,开始学习逻辑门之前应具备半导体器件的相关知识

可阅读如下文章进行先导学习

半导体器件:

https://blog.csdn.net/weixin_52308622/article/details/132199369?spm=1001.2014.3001.5501

MOS管的分类:

http://www.kiaic.com/article/detail/1735.html#:~:text=mos%E7%AE%A1%E7%9A%84%E5%9B%9B%E7%A7%8D%E7%B1%BB,P%E6%B2%9F%E9%81%93%E8%80%97%E5%B0%BD%E5%9E%8B%E7%AE%A1%E3%80%82

CMOS反相器的静态功耗几乎为零,MOS管导通电阻低,截止电阻高。使充、放电时间常数小,开关速度更快,具有更强的带负载能力。 MOS管的,IG≈0,输入电阻高。 理论上可以带任意同类门,但负载门输入杂散电容会影响开关速度。

下面依次介绍逻辑门器件

与门、或门

与门和或门由两级电路构成,且用的器件较多,即影响速度又降低集成度,所以用与非门和或非门多。

https://zhidao.baidu.com/question/276357992.html

非门

也称COS反相器,主要理解下图的红框位置,电路结构、真值表、逻辑图、逻辑表达式、工作原理(右上角)

或非门

与非门

异或门

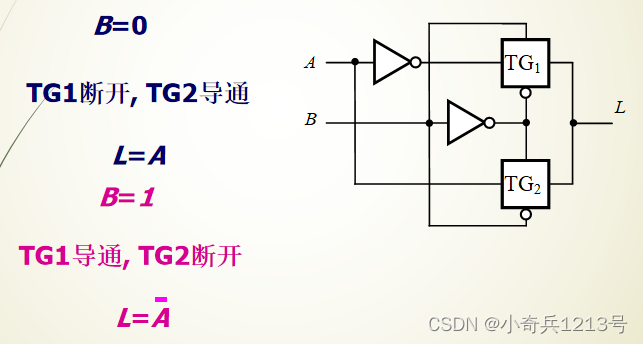

传输门

传输门的结构及工作原理

传输门(双向模拟开关)的应用

组成异或门

组成的数据选择器

三态门

三态指导通、截止、高阻三种状态,三态门主要用于数据总线复用时的分配,提高总线的利用率,实现总线上多组信号的传输且不相互影响

三态(TSL)输出门电路

OD门(漏极开路门)

CMOS漏极开路门(OD门)的提出

主要用于解决CMOS电路中的漏电流问题。在CMOS电路中,由于晶体管的特性,即使在关断状态下,也会存在一定的漏电流。这些漏电流可能会导致功耗增加、温度升高以及电池寿命缩短等问题。输出短接,在一定情况下会产生低阻通路,大电流有可能导致器件的损毁,并且无法确定输出是高电平还是低电平

CMOS漏极开路门通过在CMOS电路中添加特殊的晶体管结构,可以有效地阻止漏电流的流动,提高电路的综合性能。该结构通常由NMOS和PMOS两个晶体管组成,通过控制这两个晶体管的开关状态,可以实现对漏电流的控制和隔离。

a)工作时必须外接电源和电阻;

b)与非逻辑不变;

c) 可以实现线与功能;

上拉电阻对OD门动态性能的影响:

(1)Rp的值愈小,负载电容的充电时间常数亦愈小,因而开关速度愈快。但功耗大,且可能使输出电流超过允许的最大值IOL(max) 。

(2)Rp的值大,可保证输出电流不能超过允许的最大值IOL(max)、功耗小。但负载电容的充电时间常数亦愈大,开关速度因而愈慢。

OD门与OC门的区别

https://blog.csdn.net/m0_46642108/article/details/120222040

类NMOS门电路

MOS集成电路分为PMOS、NMOS和CMOS;NMOS比PMOS速度快。

CMOS有静态功耗低、抗干扰能力强等诸多优点成为主流器件。但CMOS电路增加一个输入端必须增加一个PMOS和一个NMOS管,在某些希望芯片面积小的应用,仍采用NMOS。

类NMOS电路可与CMOS电路相匹配。

类NMOS电路只用NMOS管串并联构成逻辑功能块,上拉通路用一个常导通的PMOS管代替复杂的PMOS逻辑功能块。 因此,对于n输入逻辑门,类NMOS电路只需要n+1个MOS管。

类NMOS反相器

当v1=0 :时NMOS管截止, PMOS管导通,输出高电平

当v1=VDD 时NMOS管和PMOS管均导通, NMOS管比PMOS管导通电阻小很多,输出低电平。

类NMOS与非门和或非门

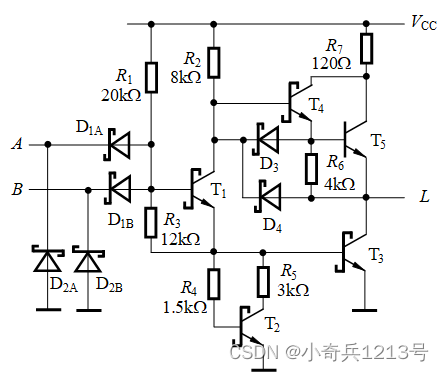

BiCMOS门电路

特点:功耗低、速度快、驱动力强

工作原理:

v1为高电平:

Mn、M1和T2导通,MP、M2和T1截止,输出Vo为低电平。

M1的导通,迅速拉走T1的基区存储电荷; M2截止, MN的输出电流全部作为T2管的驱动电流, M1 、 M2加快输出状态的转换

v1为低电平::

MP、M2和T1导通,MN、M1和T2截止,输出Vo为高电平。M1截止,MP的输出电流全部作为T1的驱动电流

T2基区的存储电荷通过M2而消散。M1、M2加快输出状态的转换电路的开关速度可得到改善

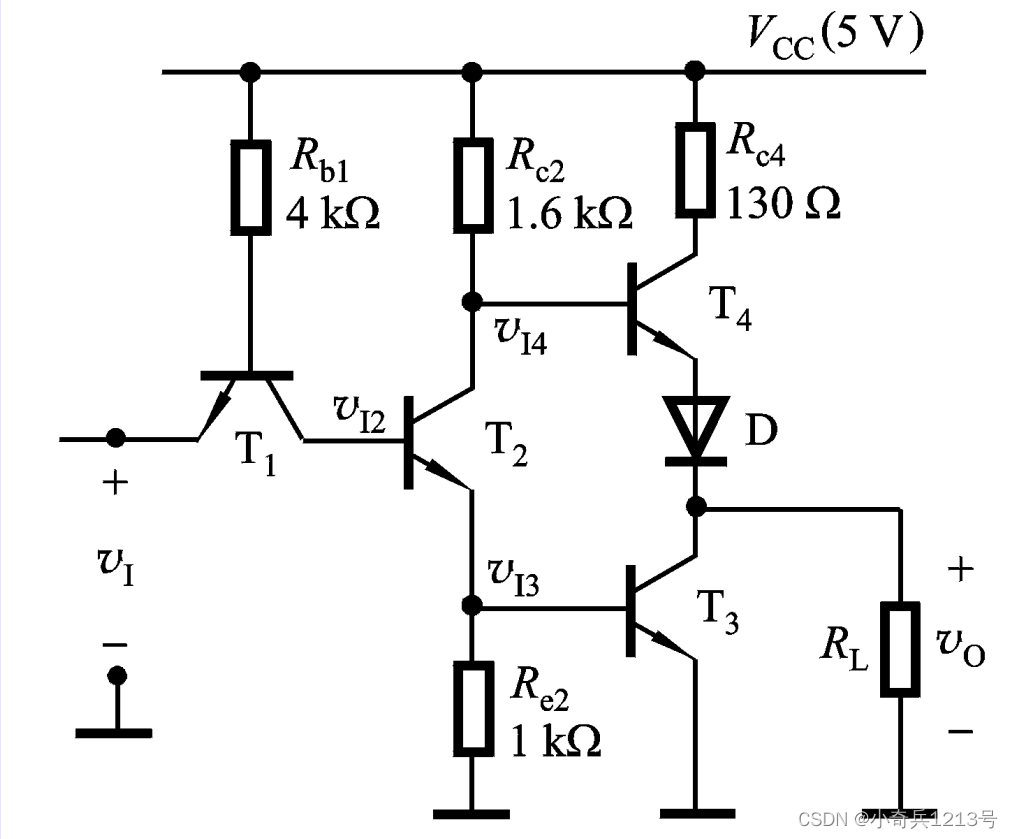

TTL门电路

电路组成:输入级------T1和电阻Rb1组成。用于提高电路的开关速度

中间级-----T2和电阻Rc2、Re2组成,从T2的集电结和发射极同时输出两个相位相反的信号,作为T3和T4输出级的驱动信号;

输出级------T3、D、T4和Rc4构成推拉式的输出级。用于提高开关速度和带负载能力。

工作原理:

i)输入低电平时(Vi=0.2V)-----T1 深度饱和,VB1=0.9V,要使T2 、T3导通则要求,VB1=2.1V。T2 、 T3截止,T4 、D导通。

ii)当输入为高电平(Vi= 3.6 V)--------T2、T3饱和导通,T1:倒置的放大状态,T4和D截止。使输出为低电平Vo=Vc3=Vces3=0.2V

抗饱和TTL门电路-改进型TTL门电路------采用肖特基势垒二极管SBD 限制BJT导通时的饱和深度。SBD导通电压为0.4V。使BJT的c、e间正偏电压钳位在0.4V,而不进入深度饱和。

肖特基TTL与非门 电路如图所示。

数字集成电路:

CMOS集成电路------广泛应用于超大规模、甚大规模集成电路

TTL 集成电路------广泛应用于中大规模集成电路

![Java并发编程(五)线程同步 下 [CAS/原子类/同步容器类/同步工具类]](https://img-blog.csdnimg.cn/75d33836f5834a47ad455d40c0d485d7.png)

![[C语言] 指针](https://img-blog.csdnimg.cn/7ddf4693bdd240649bd29576419ad7bf.png)