目录

- 标题:An Improved 4H-SiC Trench-Gate MOSFET With Low ON-Resistance and Switching Loss

- 摘要

- 信息解释

- ICP-RIE

- LPCVD

- ac

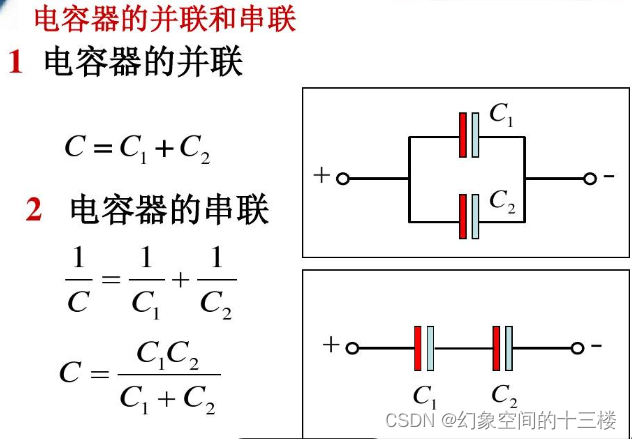

- 电容的串并联

- 研究了什么

- 文章的创新点

- 文章的研究方法

- 文章的结论

标题:An Improved 4H-SiC Trench-Gate MOSFET With Low ON-Resistance and Switching Loss

摘要

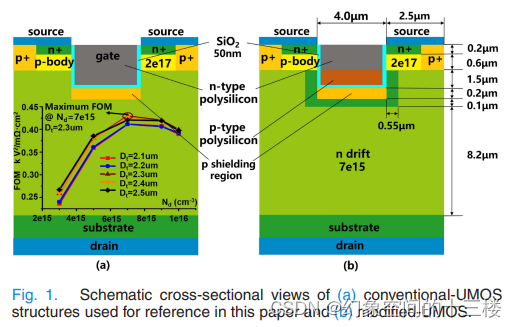

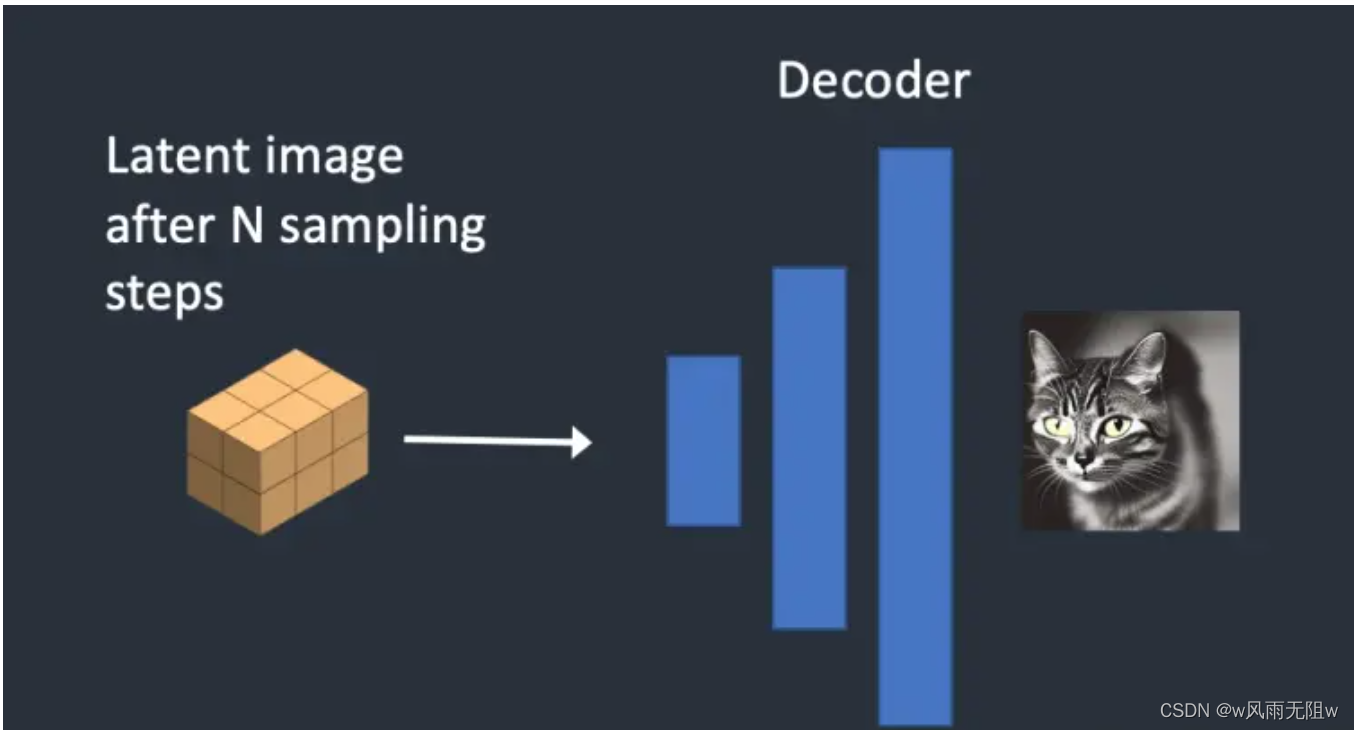

在这篇论文中,提出了一种改进的4H-SiC U型沟槽栅金属-氧化物-半导体场效应晶体管(UMOSFETs)结构,具有低导通电阻(RON)和开关能损耗。这种新型结构具有一个额外的n型区域,显著降低了器件的导通电阻,同时保持击穿电压(VBR)。此外,改进结构的栅极被设计为一个p-n结,以减小开关能损耗。通过Sentaurus TCAD进行模拟,揭示了这种改进结构的工作机制。对于静态性能,与没有额外n型区域和修改栅极的传统沟槽MOSFET相比,优化结构的导通电阻和优势系数(FOM = V2BR/RON)分别提高了40%和44%。对于动态性能,所提出结构的开启时间(TON)和关闭时间(TOFF)均短于传统结构,从而使开启能损耗和总开关能损耗(ESW)分别减少了43%和30%。

信息解释

ICP-RIE

ICP-RIE是一种常用的微纳加工技术中的缩写,代表了Inductively Coupled Plasma Reactive Ion Etching(感应耦合等离子体反应离子刻蚀)的意思。它是一种高精度、高选择性的刻蚀方法,常用于制备微纳米器件和集成电路的加工过程中。

ICP-RIE通常使用感应耦合等离子体(Inductively Coupled Plasma,ICP)和反应离子刻蚀(Reactive Ion Etching,RIE)的结合来进行刻蚀。感应耦合等离子体是一种通过高频电场激发气体产生等离子体的技术,而反应离子刻蚀则是利用这个等离子体来刻蚀材料。

在ICP-RIE中,等离子体首先被产生并加热到高温,然后被引导到待加工的材料表面。通过选择合适的气体和工艺参数,可以使等离子体中的离子与待加工材料发生化学反应,从而将材料表面的原子或分子逐渐刻蚀掉。由于ICP-RIE具有高离子密度、低能量的优势,可以实现高精度、高选择性和均匀性的刻蚀,适用于制备微细结构和纳米器件。

总的来说,ICP-RIE是一种用于微纳加工中的刻蚀技术,通过感应耦合等离子体和反应离子刻蚀的结合,实现高精度、高选择性的材料刻蚀。

LPCVD

LPCVD是Low-Pressure Chemical Vapor Deposition(低压化学气相沉积)的缩写。它是一种常用的薄膜沉积技术,用于在半导体工艺中沉积多晶硅(polysilicon)等材料。

LPCVD使用化学气相沉积的原理,在控制的气氛中将薄膜材料沉积在基片表面。在多晶硅的情况下,LPCVD通常使用硅源气体(如二硅氯化物)和稀释氢气作为反应气体。沉积过程中,气体被引入到低压环境下,往往在几百至几千帕的范围内,并通过热解化学反应使硅源气体分解,将硅沉积在基片表面上。同时,通过控制沉积温度、气体流量和沉积时间等参数,可以调节多晶硅薄膜的特性和厚度。

LPCVD具有以下特点:

- 低压环境下进行,适用于对基片材料和结构有特殊要求的制程。

- 可以在较低的温度下进行,有利于保护基片的热稳定性。

- 沉积速率较慢,可以实现较好的薄膜均匀性和控制性。

- 适用于大面积和复杂结构的沉积,如半导体器件制造中的多晶硅薄膜。

因此,LPCVD是一种通过低压化学气相沉积技术在半导体工艺中沉积多晶硅等材料的方法。

ac

The ac small signal is set to 1 MHz to extract the capacitance in this paper [6], [7].

在这个上下文中,“ac” 是交流信号的缩写。在电子电路中,交流信号是指频率可变的信号,与直流信号(恒定频率)相对。在这篇论文中,作者设置了1 MHz的交流小信号来提取电容。

交流信号的英文全称是 “alternating current signal”。

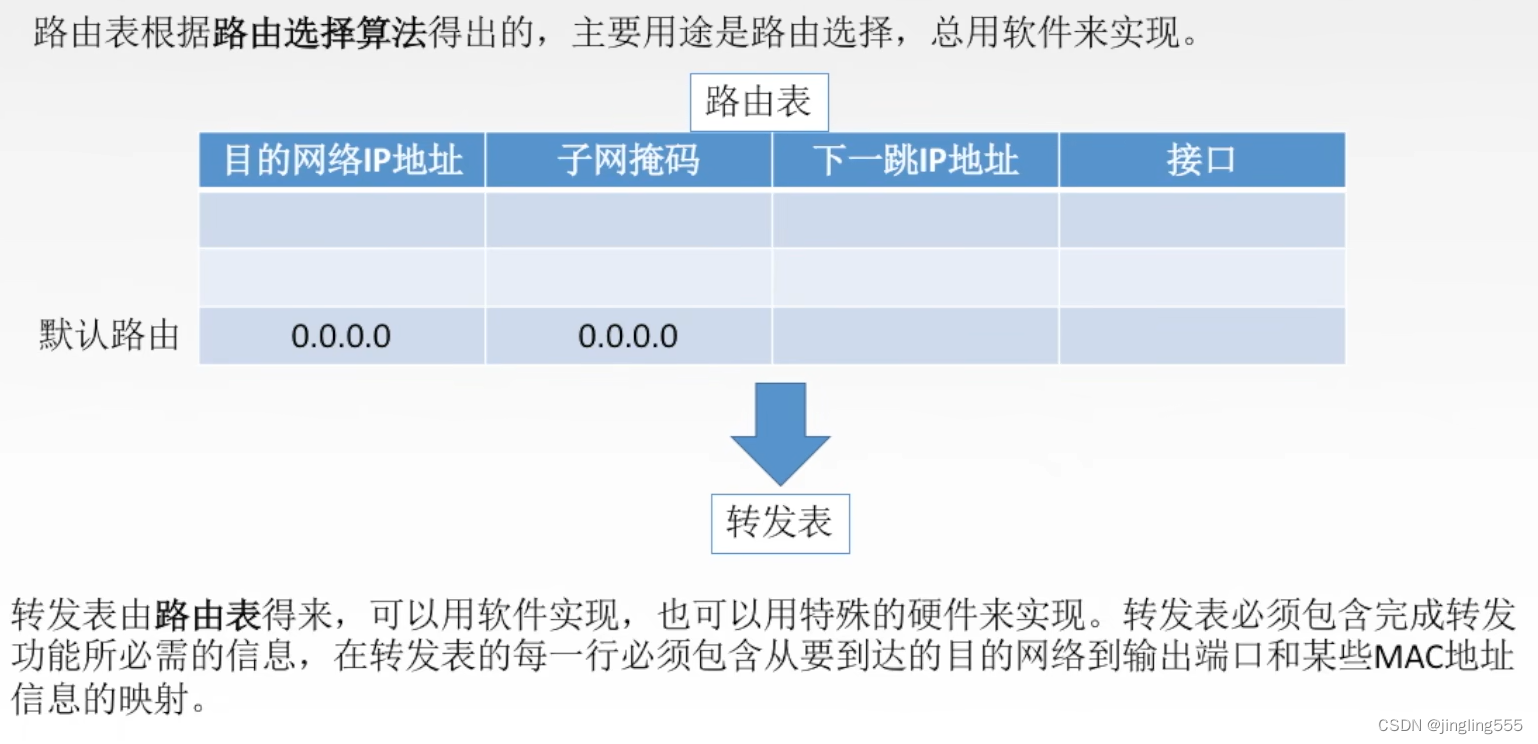

电容的串并联

研究了什么

该文章研究了一种改进的4H-SiC U型沟槽栅金属氧化物半导体场效应晶体管(UMOSFET)结构,具有低开通电阻和开关能量损失。该提出的结构具有一个添加的n型区域,显著降低了开通电阻,同时保持了击穿电压。此外,改进结构的栅极设计为一个p-n结,以减小开关能量损失。该研究使用Sentaurus TCAD进行了仿真,揭示了改进结构的工作机制。与传统结构相比,改进后的UMOS的静态和动态性能都得到了显著提高。

文章的创新点

该文章的创新点包括:

- 提出的4H-SiC UMOSFET结构具有一个添加的n型区域,可以显著降低开通电阻,同时保持击穿电压。

- 改进结构的栅极设计为一个p-n结,以减小开关能量损失。

- 由于漂移层中添加的n型区域减小了耗尽区域的大小,改进后的UMOS具有显著降低的开通电阻。

- 改进后的UMOS提高了动态性能并减小了开关能量损失。

- 静态性能参数RON 和 FOM 分别提高了40%和44%,而动态仿真结果显示改进后的UMOS的TON 和 TOFF 分别从22.2 ns 改善到12.2 ns 和 22.3 ns 改善到16.3 ns,能量损失减少了30%。

文章的研究方法

该文章使用Sentaurus TCAD进行仿真来揭示改进结构的工作机制。其中,求解了电子/空穴连续性方程和泊松方程,并考虑了奥杰复合、肖克利-里德-霍尔复合、不完全掺杂离子化、掺杂依赖的迁移率、高场饱和迁移率、带宽缩窄和冲击电离等物理效应。文章讨论了添加的n型区域的关键参数对器件特性的影响,并对沟槽中的p-n结进行了分析。此外,文章还提出了一种可能的工艺流程,以展示改进UMOS在制造上的可行性。

文章的结论

该文章的结论是,相比传统的UMOS结构,提出的改进UMOS结构具有添加的n型区域和通过p-n结减小的沟槽栅体积,显著改善了静态和动态性能。添加的n型区域降低了开通电阻,而沟槽中的p-n结提高了动态性能并减少了开关能量损失。仿真结果清楚地显示了该结构的优势,包括RON 、FOM、TON 、TOFF 和能量损失的改善。该文章展示了改进UMOS在制造方面的可行性,并提供了一种可能的工艺流程。

![[管理与领导-11]:IT基层管理者 - 目标与落实 - 过程管理失控,结果总难达成的问题思考:如何把过程管控做得更好?](https://img-blog.csdnimg.cn/88c92e3da77844a9b8b522b4a344dc39.png)