什么是cpu cacheline

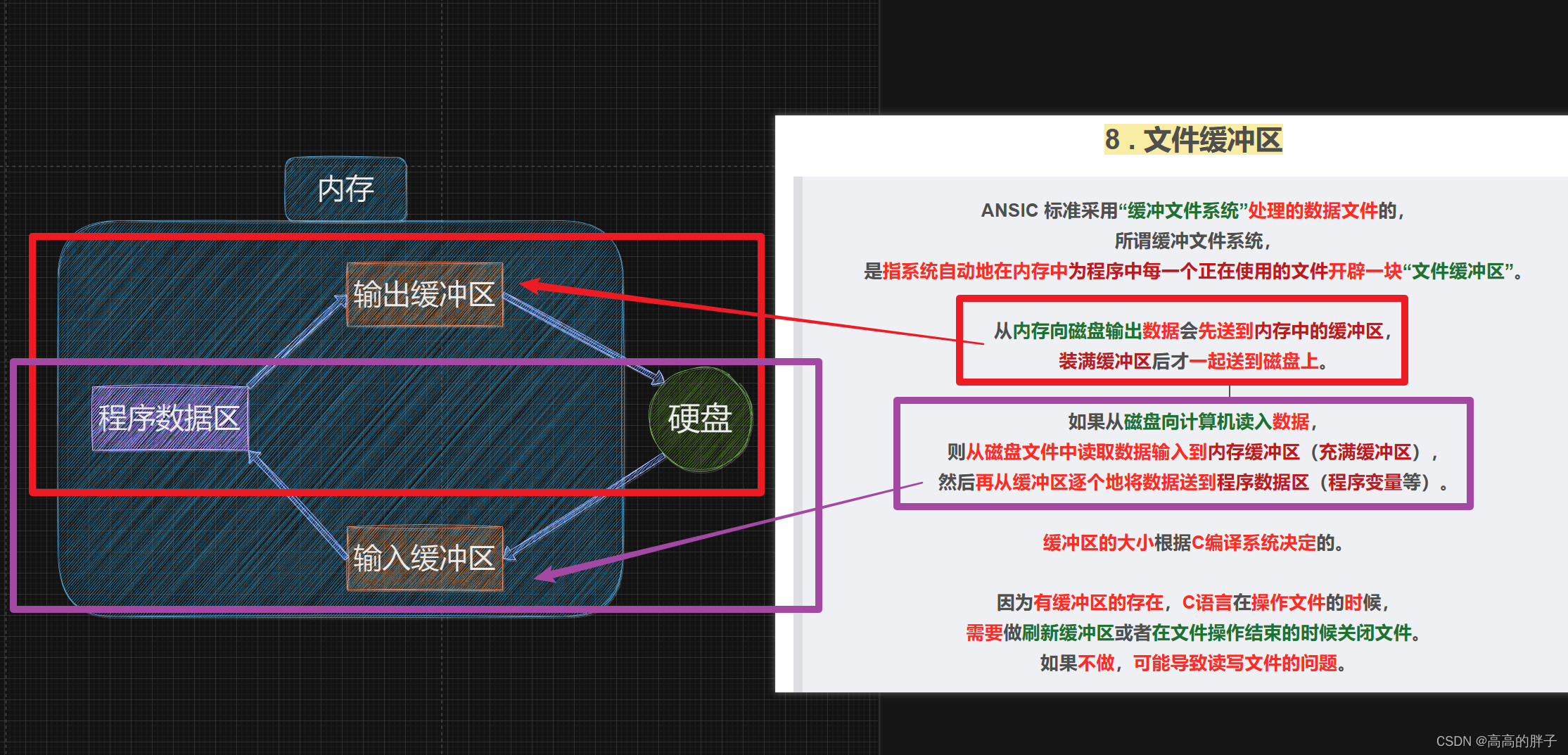

CPU的缓存行(Cache Line)是存储器层次结构中的一部分,用于在CPU缓存和主存之间传输数据。缓存行是缓存的最小单位,也是处理器从主存中读取数据到缓存或将数据从缓存写回主存的最小数据块。

缓存行的大小是由硬件设计决定的,通常是2的幂次方大小,例如32字节、64字节或128字节。具体的缓存行大小取决于CPU架构和实现。

当处理器需要访问内存中的数据时,它会首先检查该数据是否已经存在于缓存中。如果数据在缓存中,即发生了缓存命中,处理器可以快速从缓存中读取或写入数据,因为缓存访问速度比主存访问速度快得多。

如果数据不在缓存中,即发生了缓存未命中,处理器需要从主存中加载整个缓存行大小的数据到缓存中,并将所需数据返回给请求者。这样,在后续对同一缓存行内其他数据的访问中,可以直接从缓存中获取,而无需再次访问主存,从而提高访问速度。

缓存行的存在可以提高数据访问的效率,尤其是对于具有空间局部性和时间局部性的访问模式,即访问的数据很可能与之前或之后的访问数据在空间上或时间上接近。通过利用缓存行的大小,处理器可以更好地预取和缓存数据,减少对主存的访问次数,提高整体性能。

在编写程序时,合理利用缓存行对齐和缓存友好的访存模式可以帮助提高程序的性能,减少缓存未命中的次数,从而充分利用CPU的缓存系统.

使用注意

缓存行对齐适用于大部分类型的数据访问,但并不是适用于所有类型的数据访问。以下是一些需要考虑的情况:

-

原子操作:对于需要进行原子操作的数据访问,缓存行对齐可能不适用。原子操作要求对数据的访问是原子的,而缓存行对齐可能导致对多个数据的访问,从而破坏了原子性。在这种情况下,可能需要使用特殊的原子操作指令或者使用其他同步机制来确保数据的一致性和原子性。

-

数据结构的内存对齐:某些数据结构可能有特定的对齐要求,与缓存行大小不一致。例如,某些硬件设备可能要求特定数据结构的内存地址按照设备要求对齐。在这种情况下,需要遵循设备的对齐要求,而不是仅仅考虑缓存行对齐。

-

小规模数据访问:对于小规模的数据访问,缓存行对齐可能不会带来显著的性能优势。如果访问的数据量很小,无法充分利用缓存行的大小,则缓存行对齐的效果可能有限。

总的来说,缓存行对齐通常适用于大规模数据访问或连续数据访问的情况,可以最大程度地利用缓存的特性提高性能。但在特定的情况下,如原子操作或特定的内存对齐要求,可能需要采取其他策略来确保数据的正确性和一致性。在编写程序时,要根据具体的需求和限制,综合考虑对齐要求和性能优化的因素。