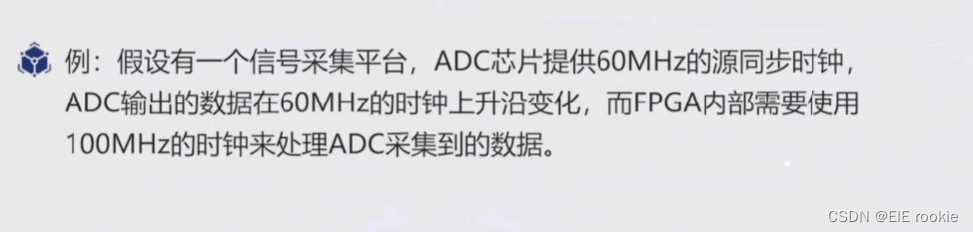

60m写入异步ram,再用100M从ram中读出

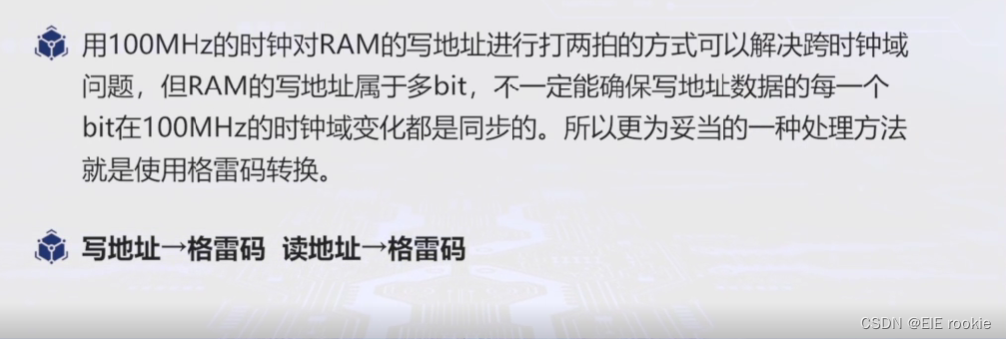

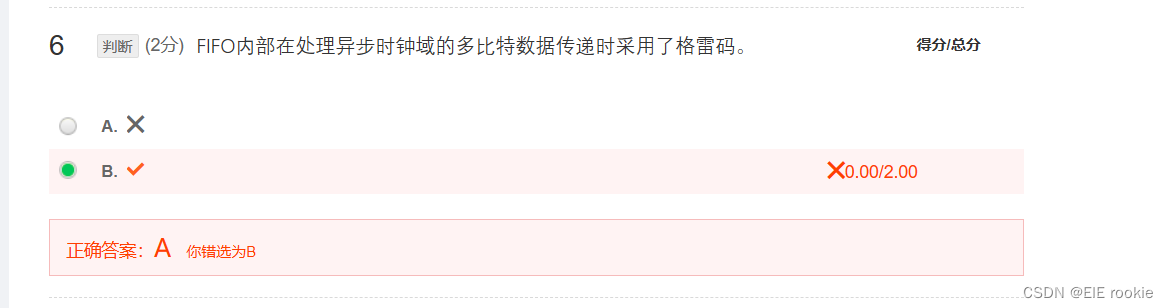

写地址转换为格雷码后,打两拍和读地址判断是否空产生。相反读地址来判断是否满产生。

分割同步模块

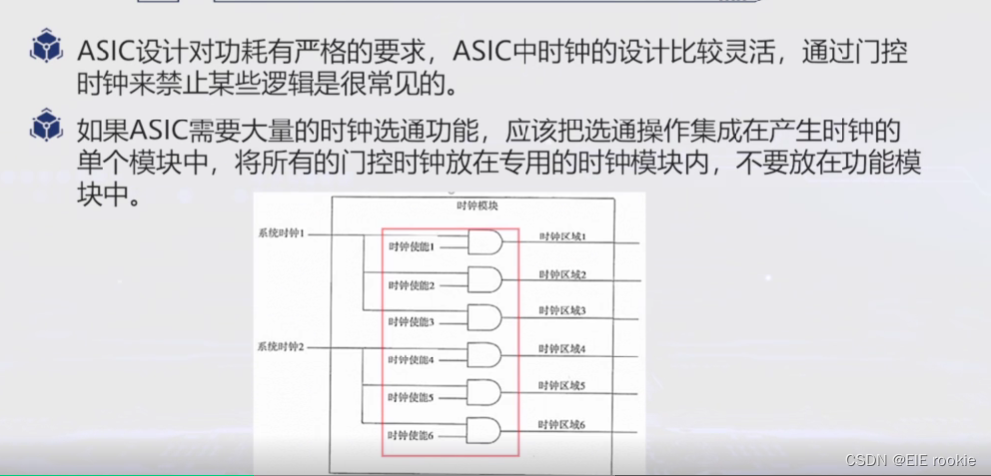

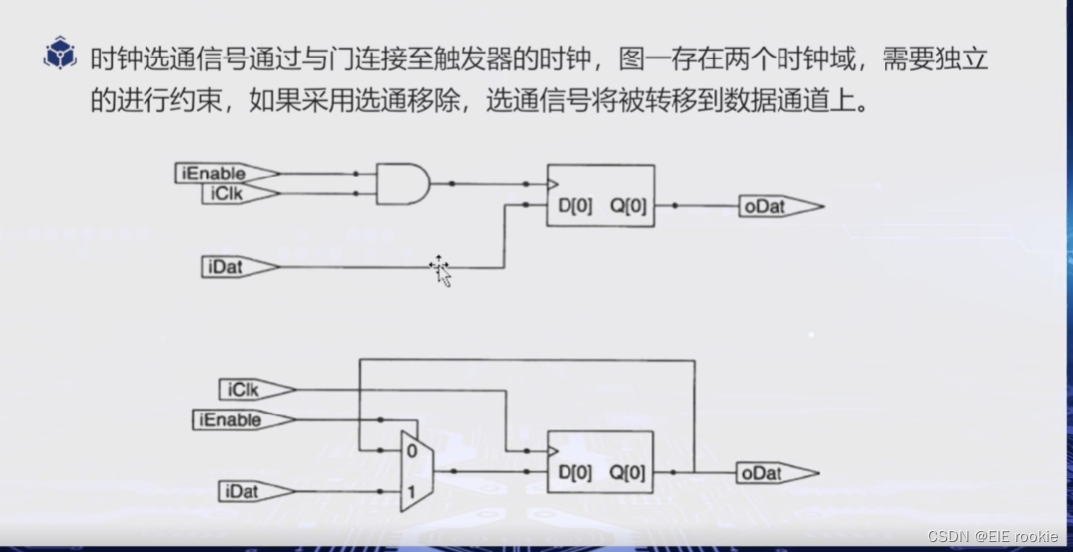

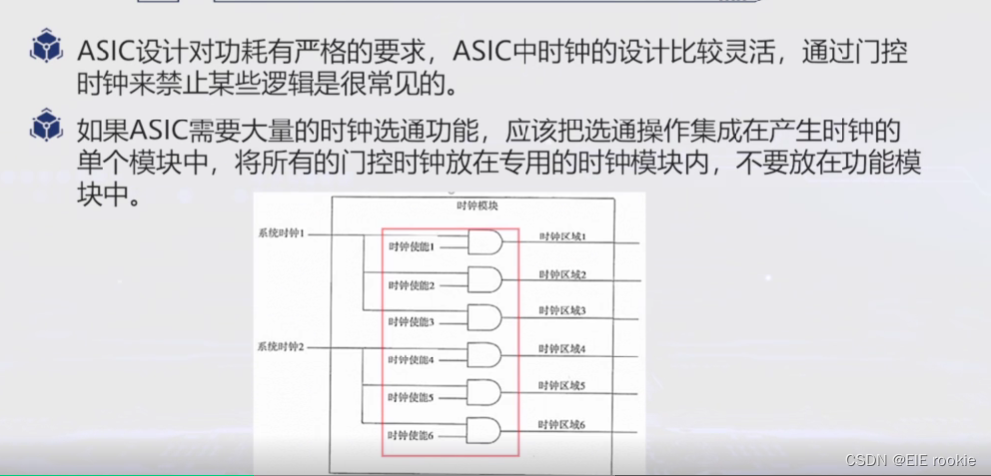

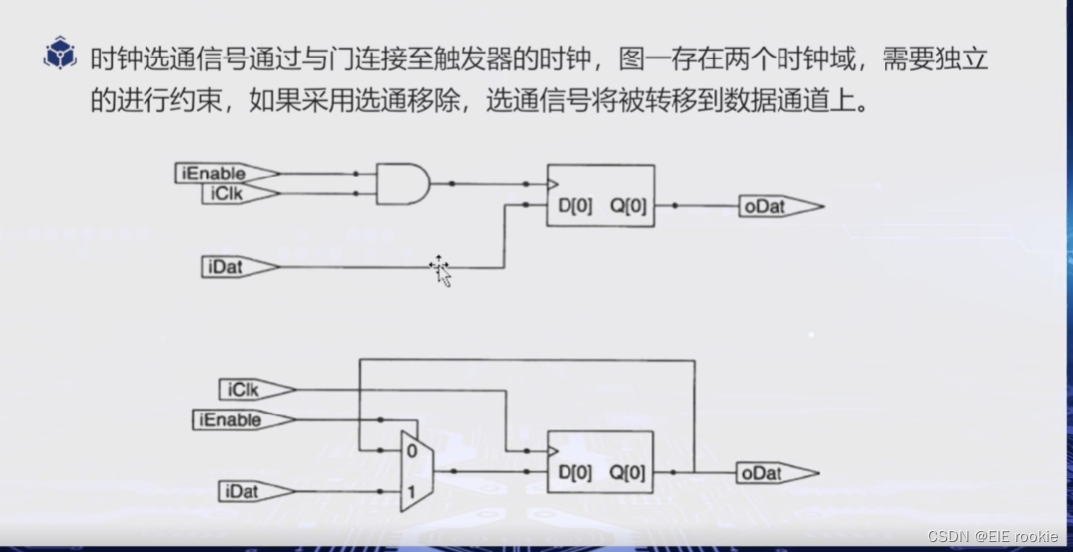

asic时钟的门控时钟,fpga是不推荐采用门控时钟的,有很多方法移除fpga的时钟选通。

如果是asic采用门控,fpga不采用

不是在内部

内部就一个ram双口的

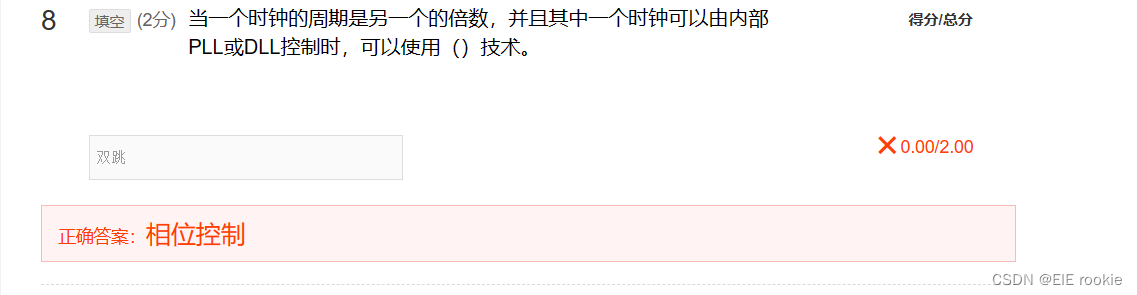

相位控制!!!

60m写入异步ram,再用100M从ram中读出

写地址转换为格雷码后,打两拍和读地址判断是否空产生。相反读地址来判断是否满产生。

分割同步模块

asic时钟的门控时钟,fpga是不推荐采用门控时钟的,有很多方法移除fpga的时钟选通。

如果是asic采用门控,fpga不采用

不是在内部

内部就一个ram双口的

相位控制!!!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如若转载,请注明出处:http://www.coloradmin.cn/o/858291.html

如若内容造成侵权/违法违规/事实不符,请联系多彩编程网进行投诉反馈,一经查实,立即删除!