文章目录

- 前言

- 一、乒乓操作简介

- 二、双端口RAM配置

- 三、RAM控制模块设计

- 四、乒乓操作验证

前言

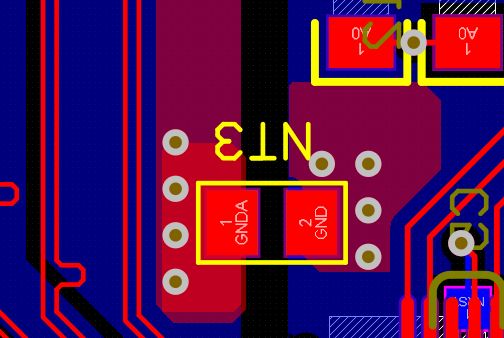

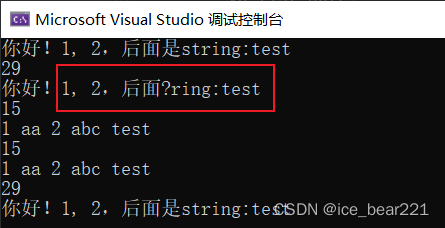

本文将介绍基于双端口RAM的乒乓操作测试,并探索如何在AWC_C4MB开发板上实现这一测试。双端口RAM作为一种性能出色且功能强大的存储器设计,为我们提供了并发访问和数据交互的重要工具。AWC_C4MB开发板作为一款先进的硬件平台,拥有强大的处理能力和丰富的外设资源,通过在该开发板上进行乒乓操作测试,可以更好地理解并发读写操作对系统性能的影响,并找出性能瓶颈和优化策略。开发板实物图如下:

在本次测试中,我们将详细介绍如何调用AWC_C4MB开发板的双端口RAM IP核,实现并发的读写操作,通过50MHZ时钟分别向两个不同的RAM里面写入100个数据,然后通过25MHZ时钟连续无间断将数据读出,了解其如何支持高速数据交换和并行处理。

一、乒乓操作简介

乒乓操作是一种特殊的内存访问模式,通常用于并发读写操作。它在计算机系统中扮演着重要角色,尤其在多处理器系统、实时应用和高性能计算领域。乒乓操作的基本思想是同时进行并发的读和写操作,实现快速的数据交换和共享。它的名称源自于乒乓球比赛中球的来回传递,类似地,在乒乓操作中,数据在不同的访问者之间来回传递和交换。

以两个缓存器RAM1和RAM2进行乒乓操作为例,初始时刻数据写入端口将数据写入进RAM1内,不进行其它操作,如下图所示:

RAM1内数据写入完成后,数据读出端口就可以开始读取出RAM1内数据了,同时数据写入端口继续向RAM2内写入数据,如下图所示:

当RAM1内的数据读出完成,RAM2内的数据写入完成,此刻对两个存储器的读写操作进行交换,数据写入端口继续向RAM1内写入数据,数据读出端口开始读出RAM2内的数据,如下图所示:

因此,在乒乓操作中,涉及到多个访问者或处理器同时访问内存。通常情况下,一个访问者进行读操作,而另一个访问者同时进行写操作。这种并发的读写操作可以提高内存访问效率,减少等待时间,提高整个系统的性能。

二、双端口RAM配置

双端口RAM(Dual-Port RAM)是一种具有两个独立数据端口的随机存取存储器(RAM),它可以同时支持两个不同的读写操作。每个端口都可以独立地访问内存单元,无需等待其他端口的操作完成。这使得双端口RAM能够实现高效的并发读写操作,广泛应用于需要同时进行多个数据访问的系统中。双端口RAM示意图如下:

在Quartus里面配置双端口RAM IP核,①在IP核目录下输入RAM,②点击RAM:2-PORT,③为双端口RAM IP核指定一个存放路径并命名,本工程给该IP核命名为ram_gen。操作步骤如下图所示:

针对弹出的界面:

①是选择RAM的端口类型,可以选择单个读端口和单个写端口,也可以选择两个读端口和两个写端口,在本工程中,只需要一个写端口和一个读端口对数据进行写入和读出即可,因此选择第一个选项;

②是设定用什么来定义存储器的大小,可以选择按字节定义,也可以选择按比特数定义,这里设定按照字节定义;

按照下图配置,配置完成后点击Next:

针对弹出的界面:

①是设置输入的信号深度,本工程写入到RAM内的数据是100个,数据位宽为8,因此选择128即可;

②是设置输入输出数据位宽是否相同,这里要设置不相同,因为写入数据时钟是50MHZ,写入的数据位宽设置为8,读时钟为25MHZ,所以读出的数据位宽要为16,才能满足处理速度与处理面积相等的原则,实现数据的无缝传输与处理;

③是存储单元类型的选择,这里保持默认设置即可。

按照下图配置,配置完成后点击Next:

针对弹出的界面:

①是时钟的设置,可以设置读写端口时钟相同,也可以设置读写端口时钟不相同,也可以设置写入数据时钟和读出数据时钟不相同,这里设置写入和读出数据时钟不相同;

②是创建读数据使能信号,这里保持勾选;

③是创建端口字节使能信号,这里选择不勾选;

按照下图配置,配置完成后点击Next:

针对弹出的界面:

①是设置是否选择对读出的数据进行寄存,如果选择寄存,则在读使能信号有效时,数据会延迟一个时钟周期才输出,反之则在读使能信号有效时,数据马上输出,这里选择不勾选;

②是创建时钟使能信号,勾选此选项后,只有当时钟使能信号有效时,时钟才能正常工作,这里选择不勾选;

③是创建清零信号,该信号有效时,RAM内的数据清零,这里选择不勾选。

按照下图配置,配置完成后点击Next:

针对弹出的界面:

该界面是设置是否初始化RAM,即向RAM内初始时存入数据,这里设置不提前存入。按照下图配置,完成后点击一直点击Next:

跳转到下图时,选择生成例化模板,配置完成后点击Finish。

三、RAM控制模块设计

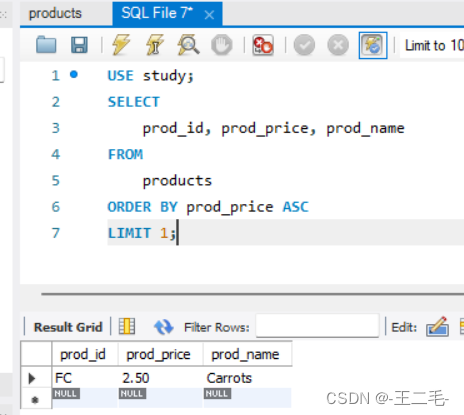

首先设计一个数据生成模块,在50MHZ工作时钟下,复位信号无效时,每个时钟周期生成一个待写入的数据,并产生数据写入使能信号。RAM控制模块则是对写入到两个FIFO里面的信号进行定义,根据设计需要绘制的信号波形图如下图所示:

对照上述信号波形图编写代码,即可实现基于双端口RAM的乒乓操作。

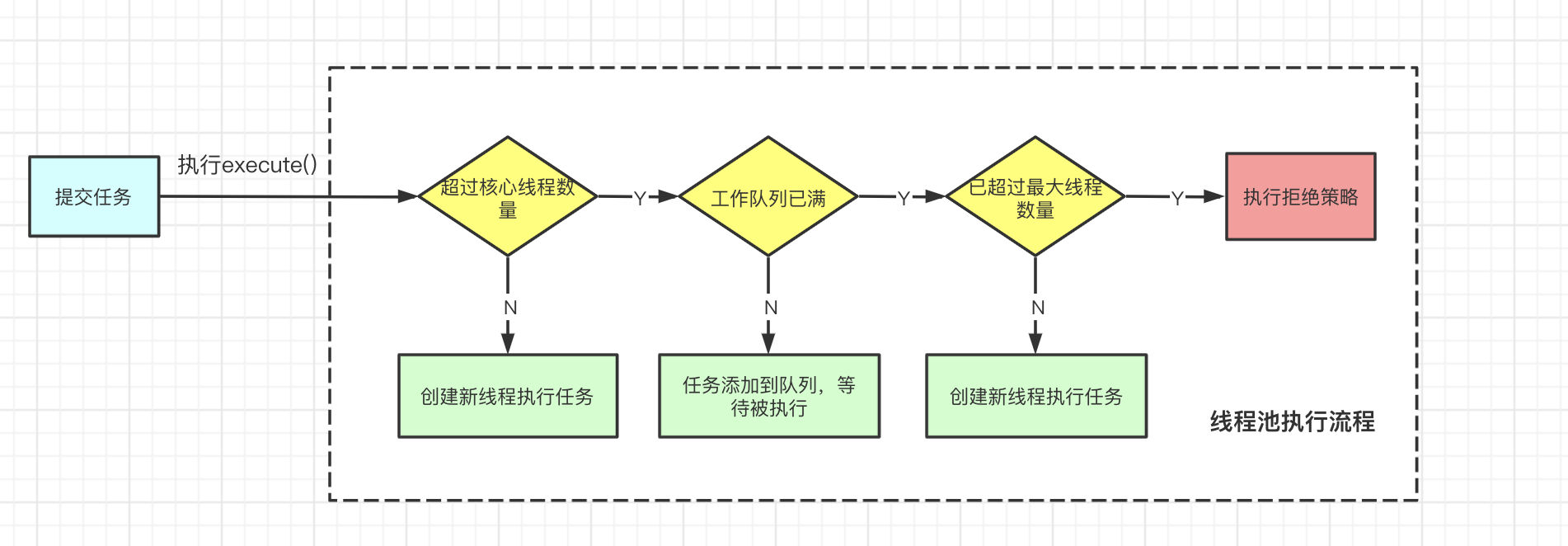

四、乒乓操作验证

如图,读出的数据为rd_data,根据波形图可知已经实现数据无缓冲读出,基于双端口RAM的乒乓操作测试成功。