衬底电流容易导致寄生三极管导通(衬底电阻+衬底电流=》衬底压差),更容易触发latchup;

一般常用的实际产品中会用衬底隔离的器件来做负压器件;用DNW&NBL组成一个隔离盆将整个负压区和正常电路分开,DNW&NBL接高电压;

你可以试试把负压区的NMOS单独放一个NW中,负压区的PMOS单独放另一个NW中,2个NW之间加地tap,

常压区&负压区通过NW-ring&p tap ring隔开,也能一定程度上减小lachup的风险;

有助于防止闩锁效应,增加背栅的连接有助于减小图中R1和R2的阻值,但是不可能无限减小,R1/R2减小了有助于提高latchup的防护性能

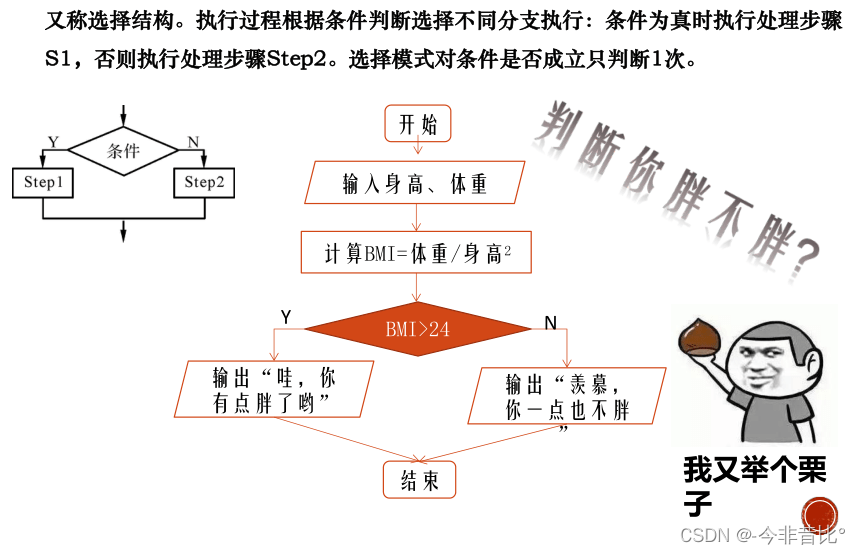

都知道latch up是VDD到GND的低阻大电流通路,结构图也清楚,但是在版图上要求nmos与pmos隔得比较远,就是为了防止latch up,这样做是为什么呢?减小衬底的电阻吗?求各位大神讲解一下

拉远是为了增大Rw2和Rs2,这样分压后,两个三极管不容易开启。

距离拉大是为了增加三极管的基极宽度,降低β。

请问:

1、保护环应该在什么时候加才合适?

2、多子保护环事实上就是衬底接触跟井接触对吗?

3、只用到PMOS或者NMOS的电路需要加保护环吗?

4、一般加保护环都是加多子保护环吗?少子保护环常用吗?

5、多子保护环跟少子保护环相比,那个效果比较好呢?

6、看了几篇关于说明Latch-up的文章,都发现其中的举例都是把P管和N管的漏极连在一起的,如果P管和N管只是相互靠近,但它们的漏极没连在一起,会出现Latch-up吗?

这是小弟看到保护环时的一些迷惑,请前辈们不吝赐教!

保护环一般要求不高可以采用衬底大面积接地(如环形衬底接地其实也就是保护环了),要求高的话可以采用double guadring的形式,即:以chrt35工艺为例,在NMOS 外加一圈P+guadring(PCOMP+CONTACT+METAL1),再加一圈N+ GUADRING(NCOMP+CONTACT+METAL1),至于是不是就是衬底接触,不同的工艺可能要求不一样,尤其是有的用的是pdiff,浓度可能不同罢了,可以参考设计规则手册,上面一般都会有说明。

自己的想法啦,不对地方恳请各位给予纠正…

1.衬底电位和阱电位应该是必须要的吧,抗noise和防latch -up时均需要吧

2.多子和少子的定义应该是和保护环收集的载流子有一定的相关性吧

3.呵呵 需要的 这个问题有点…

4.也用啊,特别是在防latch up时

5. 楼主可能需要明白latch up发生的机理,能看到PNPN架构吗?能满足latch up发生的条件吗?

很简明的回复,如果是双保护环的话,那么里边的环对应少子保护环,外边的环对应多子保护环,是这样的吗?

latchup的机理首先是局部区域大电流。没有大电流发生,latch-up发生概率就很小。

最可靠的是增加NP管间距15um。guardring必须的,但不是最有效的。

去看《模拟电路版图的艺术》第4章少子注入那一节你就能明白第一个问题了。

加背栅是防止源/漏与衬底的PN结正偏,也就是防止寄生晶体管开启,管子不开启,就没有闩锁效应了撒~

在mos晶体管中,有几个端口,分别命名为s(源极),d(漏极),g(栅极),bg(背栅)。比如PMOS的背栅是NWELL