目录

一、背景说明

二、工程设计

2.1 工程代码

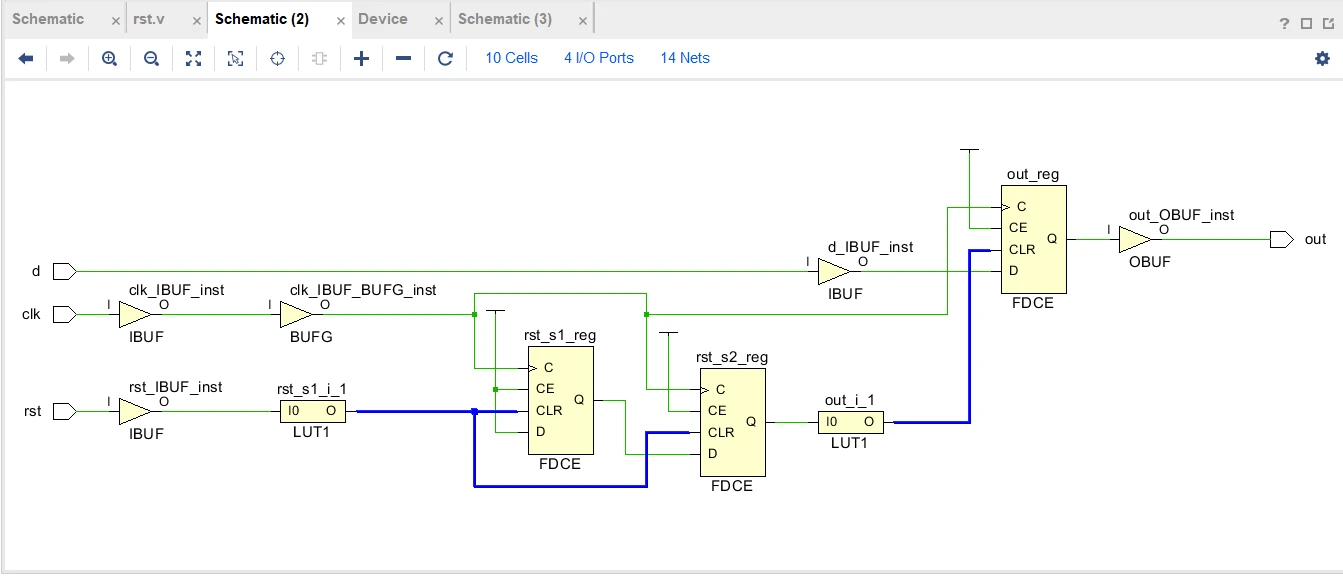

2.2 综合结果

一、背景说明

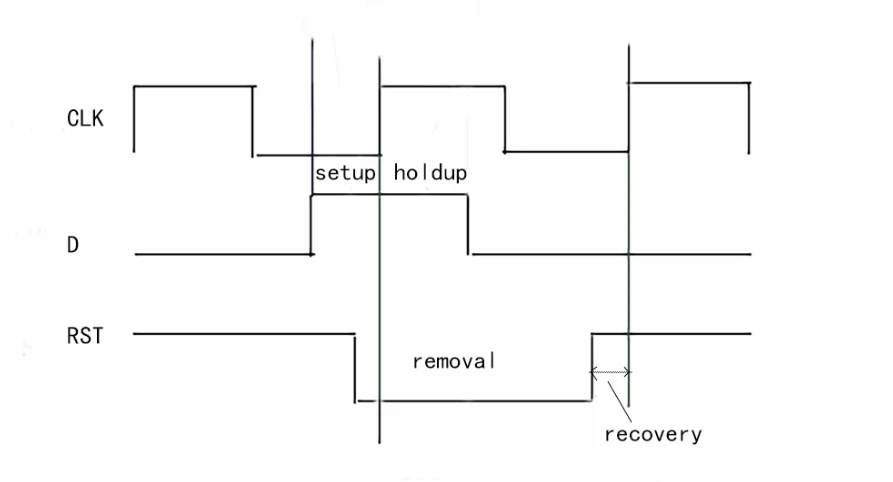

恢复时间recovery和去除时间removal和setup、holdup类型,不同点是数据信号为控制信号,如复位,清零,使能信号,更多的是异步的复位信号,并且是针对复位信号取消时的上升沿。

recovery: 复位取消信号需在时钟信号到达之前的recovery时间内稳定下来,保证复位完全释放

removal: 复位消信号需在时钟信号到达后保持至少removal时间,保证复位信号有效

二、工程设计

目前寄存器都采用异步复位,同步释放,复位可以不依靠时钟,实现简单,同时可以稳定释放复位信号,不出现亚稳态问题

2.1 工程代码

module RST (clk,rst,d,out);

input clk;

input rst;

input d;

output reg out;

reg rst_s1,rst_s2;

always @(posedge clk or negedge rst) begin

if(!rst) begin

rst_s1<= 1'b0; //异步复位操作

rst_s2<= 1'b0;

end

else begin

rst_s1<= 1'b1; //同步释放

rst_s2 <= rst_s1; //对同步释放后的复位信号延迟一拍,即最终复位信号为rst_s2

end

end

always@(posedge clk,negedge rst_s2)

begin

if (!rst_s2)

out <= 1'b0;

else

out <= d;

end

endmodule2.2 综合结果

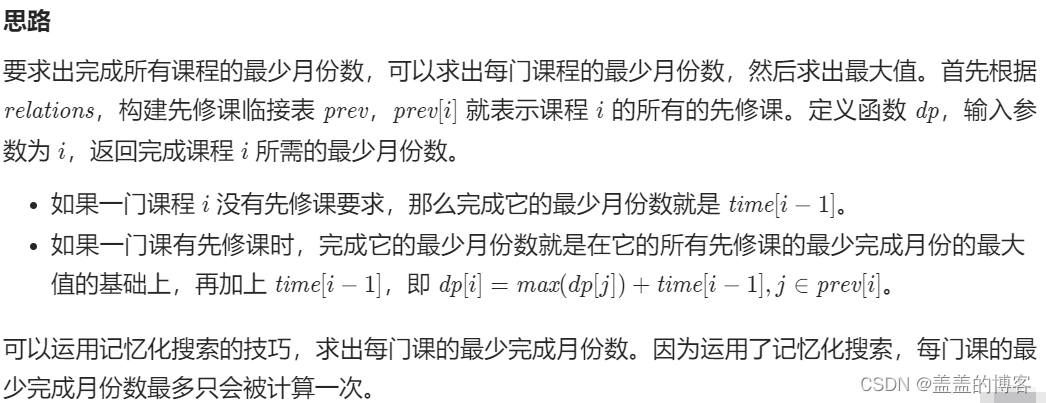

在3个FDCE的CLR端口前面都插入了LUT1,作用是作为反相器,因为FDCE的CLR是高电平有效,源码设计中为低电平进行有效复位。复位信号rst是经过两拍之后在out_reg中使用。