微信公众号上线,搜索公众号小灰灰的FPGA,关注可获取相关源码,定期更新有关FPGA的项目以及开源项目源码,包括但不限于各类检测芯片驱动、低速接口驱动、高速接口驱动、数据信号处理、图像处理以及AXI总线等

三、xilinx的AXILite的ip组件生成及使用

本章内容介绍工程中使用的AXI Crossbar ip以及Block Design中可使用的AXI interconnect组件,通过搭建工程使用。

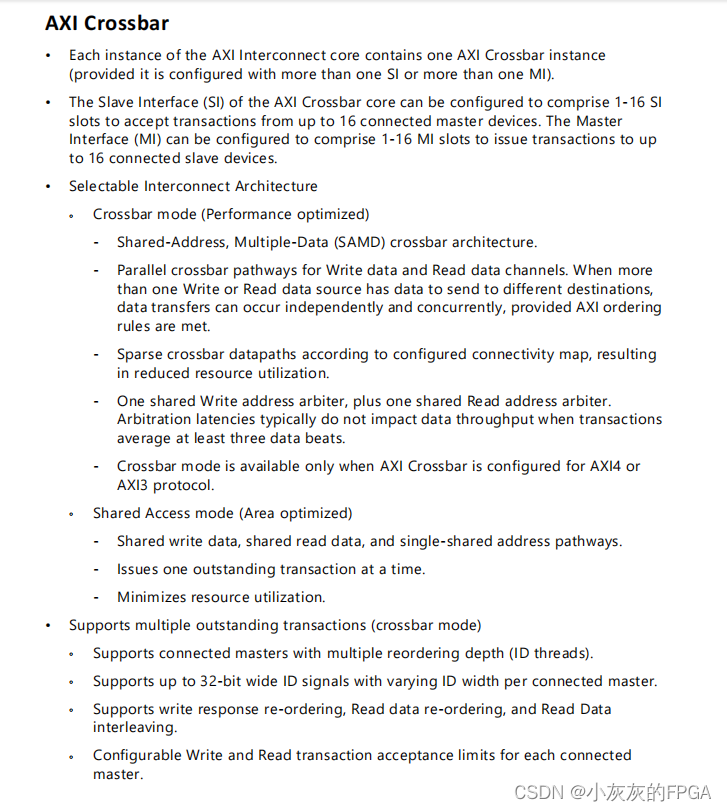

1、AXI Crossbar IP介绍使用及仿真

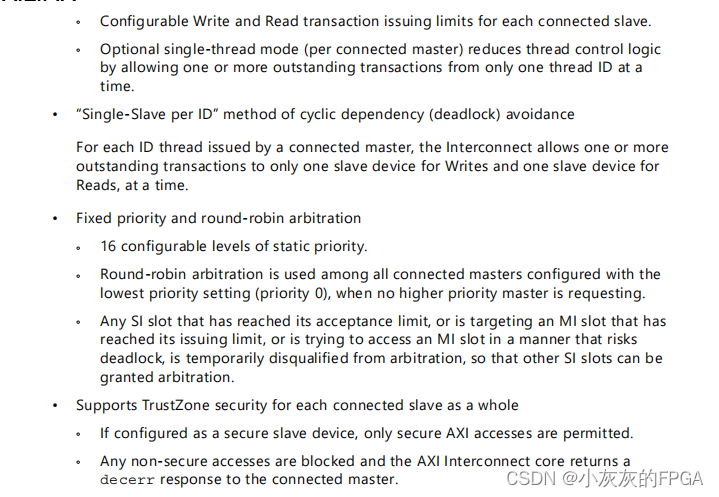

①手册知识

AXI Crossbar是一种可选择的互联模式,支持地址共享,多数据路径访问模式

②各类型器件的AXI性能

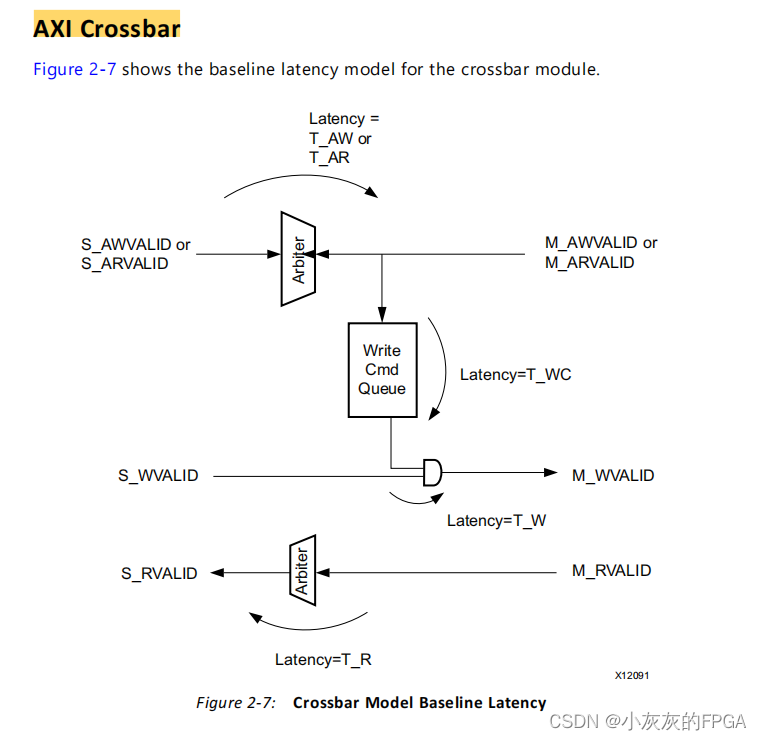

各类信号的延迟,可通过工程仿真观察

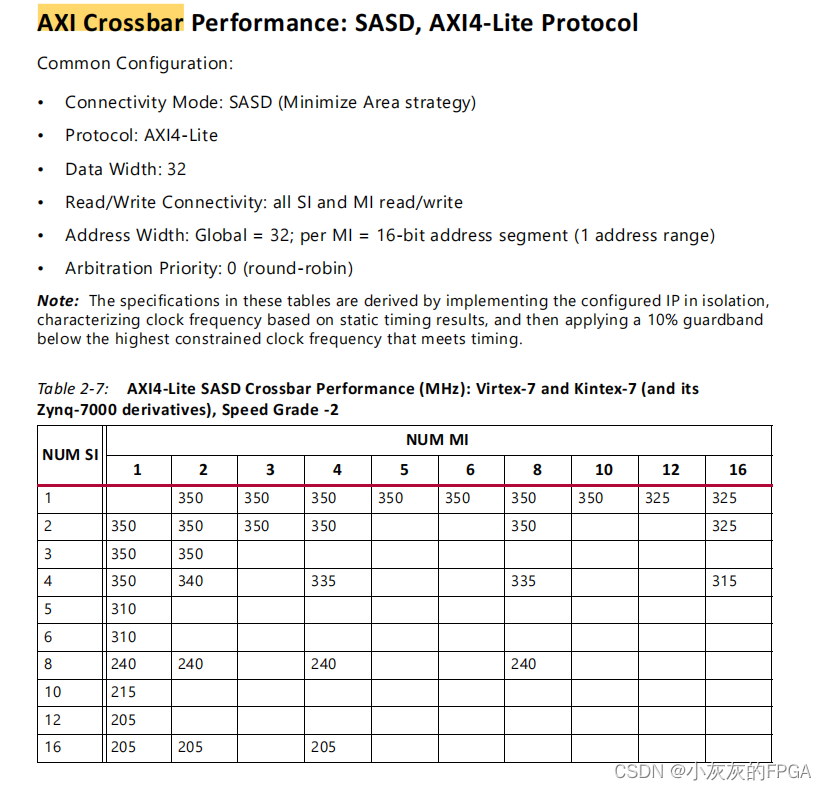

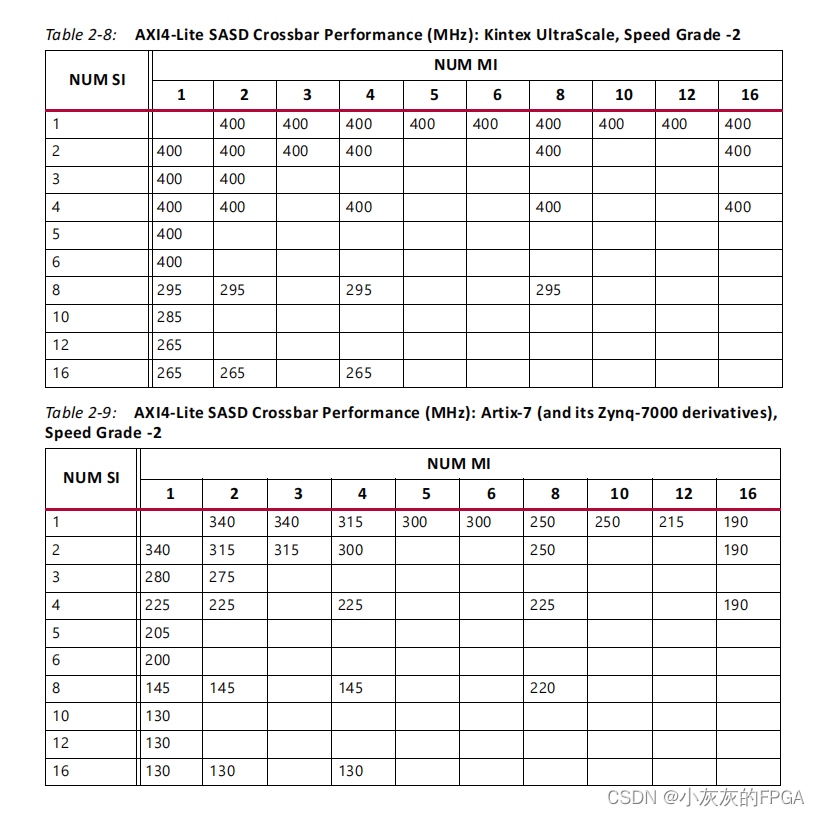

不同器件的AXI Crossbar可运行的频率要求

③具体操作及仿真

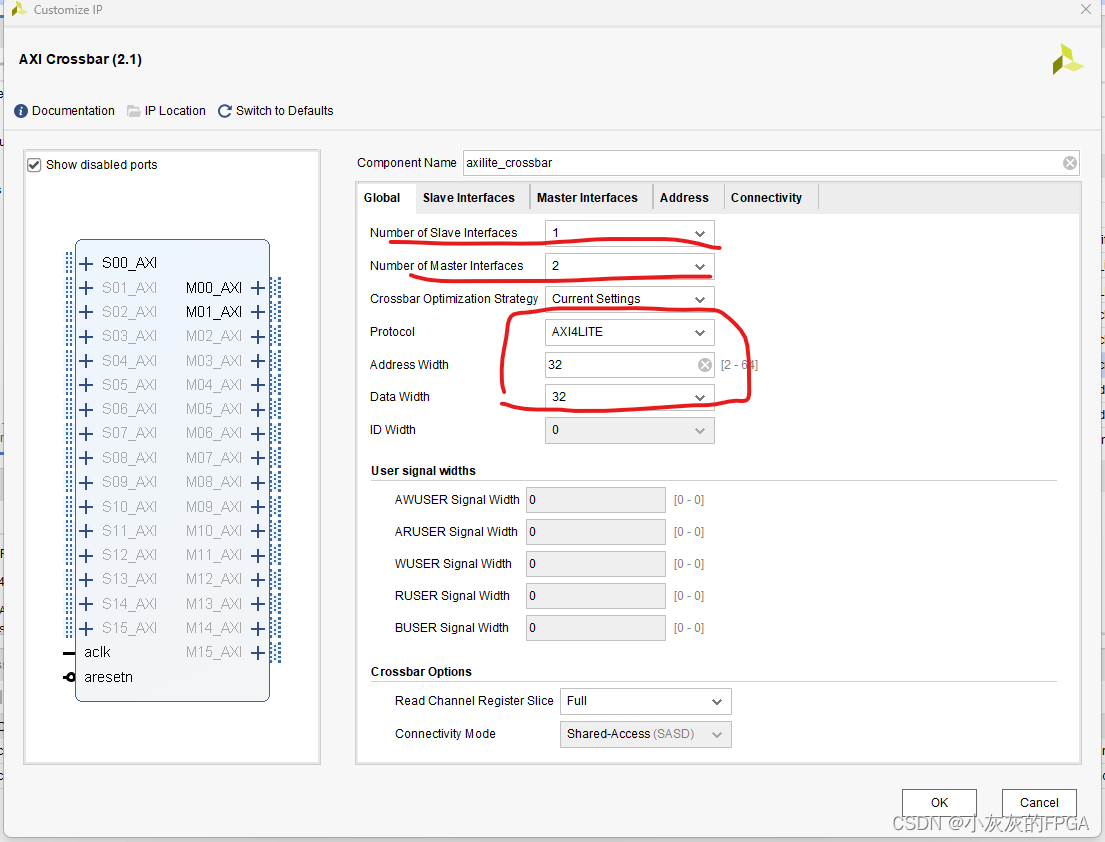

AXI Crossbar IP生成,尤其是基地址仲裁选择,需要注意适配项目的应用场景,本文采用1Master2Slaver应用场景,

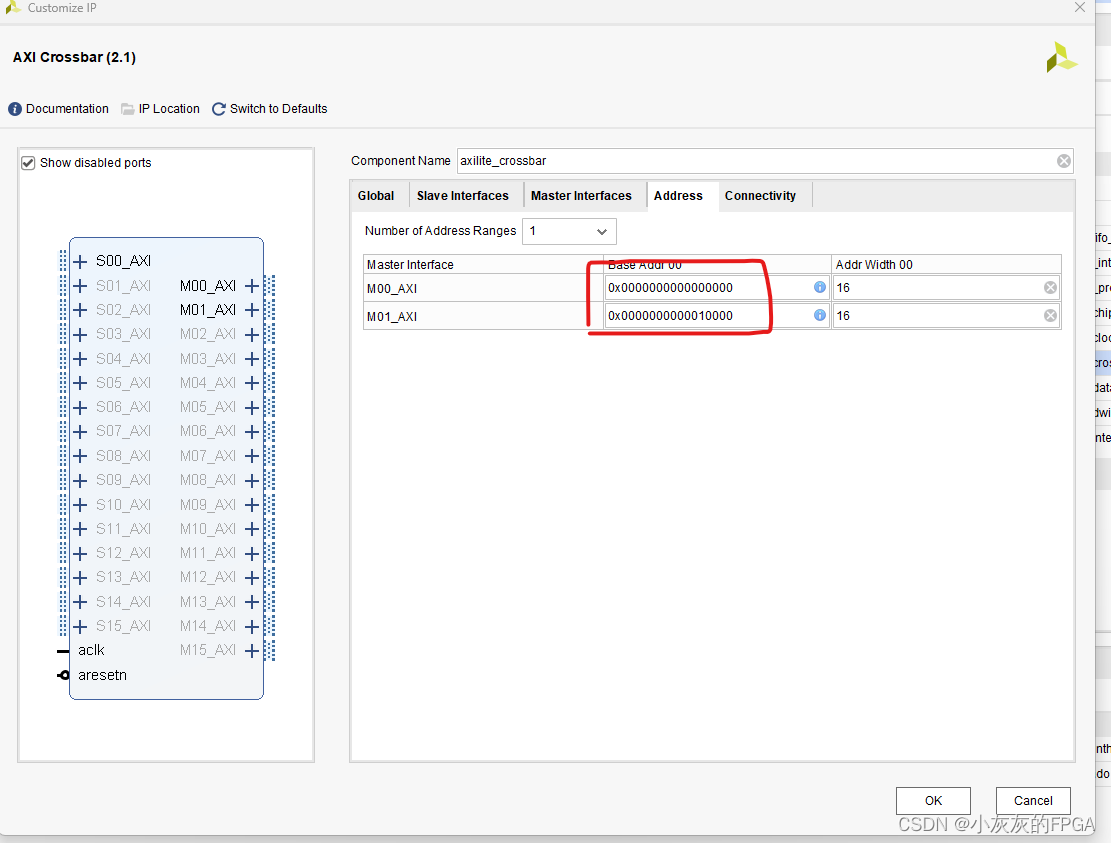

具体IP生成以及配置注意界面

工程1个Master对应至AXI Crossbar IP的slaver互联,即1个Slaver

工程2个Slaver对应至AXI Crossbar IP的两个Master互联,即2个Master

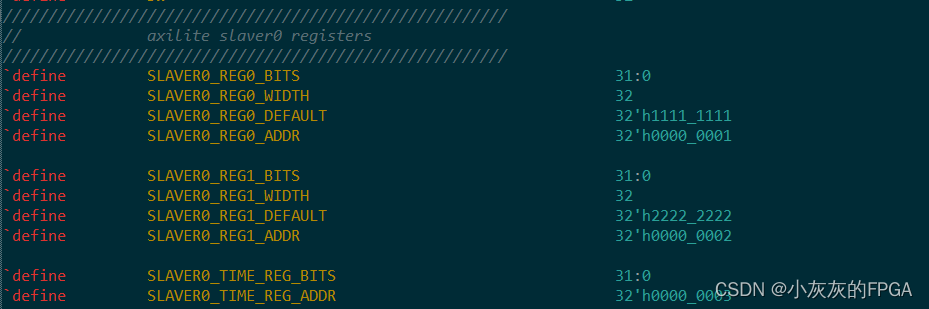

slaver0寄存器地址范围为0x00000000—0x0000FFFF,内部寄存器使用必须在此范围

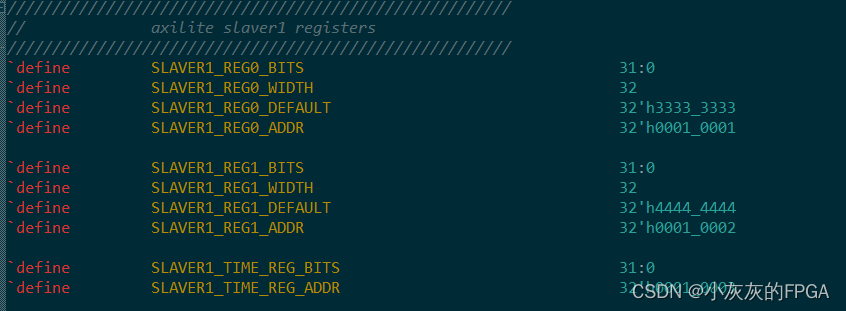

slaver1寄存器地址范围为0x00010000—0x0001FFFF,内部寄存器使用必须在此范围

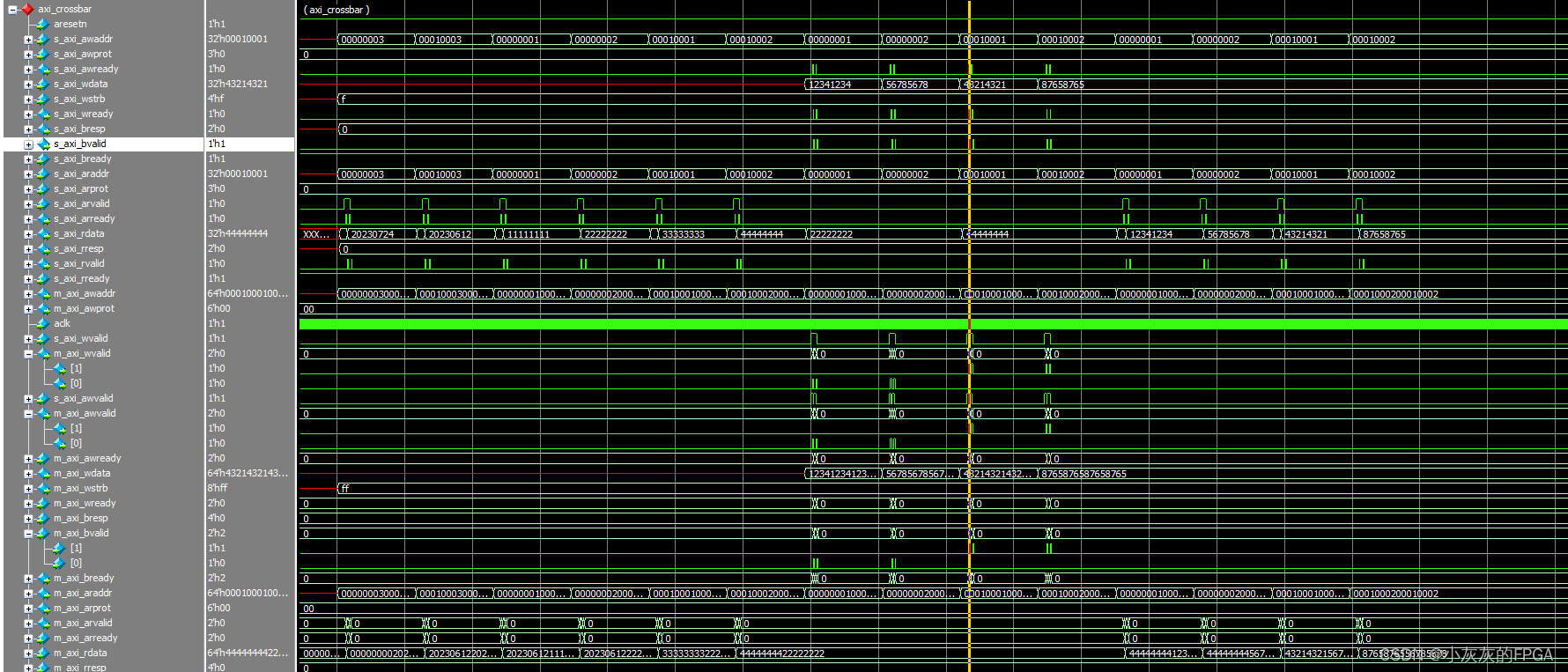

仿真时序图

AXI协议之AXILite开发设计(三)

news2026/2/11 21:33:55

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如若转载,请注明出处:http://www.coloradmin.cn/o/801673.html

如若内容造成侵权/违法违规/事实不符,请联系多彩编程网进行投诉反馈,一经查实,立即删除!相关文章

智能RFID追溯系统优化空调装配效能

智能RFID追溯系统优化空调装配效能

空调作为现代家庭和工业建筑中必备的设备,其装配过程对生产效率和质量至关重要。传统的装配方式往往依赖于人工操作,存在一定的人为失误和效率低下的问题。而RFID技术的应用能够为空调装配带来一系列的优势。

RFID技…

景区如何对旅行社进行分销管理?

旅行社的买票能力强,一般景区会跟多家旅行社合作门票分销。其中卖票下单、价格设定、财务对账结算都出现了很多问题,导致对账困难,查询困难,甚至可能有偷票漏票的情况出现,给景区收入造成损失。那要怎么处理呢…

C#..上位机软件的未来是什么?

C#是一种流行的编程语言,广泛应用于桌面应用程序和上位机软件开发。未来,C#上位机软件将继续不断发展和创新,以满足用户日益增长的需求。以下是我认为C#上位机软件未来可能会涉及的一些方向:

更加智能化:随着人工智能…

全面防护!Fortinet发布混合式部署防火墙HMF

在企业IT复杂性日益增长、网络安全威胁日趋紧迫、网络安全设施可维护性逐渐降低的背景下,企业迫切寻求可无缝跨越所有IT区域,有效简化企业防护架构的统一解决方案。近日, Fortinet Accelerate 2023中国区15城巡展圆满落幕,在收官之…

CentOS 项目发出一篇奇怪的博文

导读最近,在红帽限制其 RHEL 源代码的访问之后,整个社区围绕这件事发生了很多事情。

CentOS 项目发出一篇奇怪的博文

周五,CentOS 项目董事会发出了一篇模糊不清的简短博文,文中称,“发展社区并让人们更容易做出贡献…

安卓:Picasso——加载网络图片的库

目录

一、Picasso介绍及其优势

二、Picasso的使用方法

1、添加依赖:

2、Picasso常用方法:

1、加载图像: 2、图像显示: 3、图像处理:

4、图像占位符和错误处理:

5、缓存控制:

6、清除缓…

INDEMIND:告别人工智障,扫地机器人哪种避障方式能让你“躺平”?

方寸之间,腾转自如,这或许是人们对扫地机器人避障功能的理想期待。 谁才是扫地机器人的“最优解”?

评判一款扫地机器人好用与否,避障表现无疑是核心因素。一款能够准确有效规避家居、行人、动物的产品,不仅能够保障产…

从大众汽车7亿美元入股小鹏说起,中国汽车时代已经来了

监制 | 何玺 排版 | 叶媛

中国汽车时代已经来了!

7月26日,世界汽车企业大众宣布,将以7亿美元入股国内新势力造车企业小鹏汽车,并与后者共同开发面向中国的大众品牌电动车型;与此同时,大众旗下的奥迪品牌也…

pandas处理什么样的数据?

Pandas 是一个开源的第三方 Python 库,从 Numpy 和 Matplotlib 的基础上构建而来,享有数据分析“三剑客之一”的盛名(NumPy、Matplotlib、Pandas)。Pandas 已经成为 Python 数据分析的必备高级工具,它的目标是成为强大…

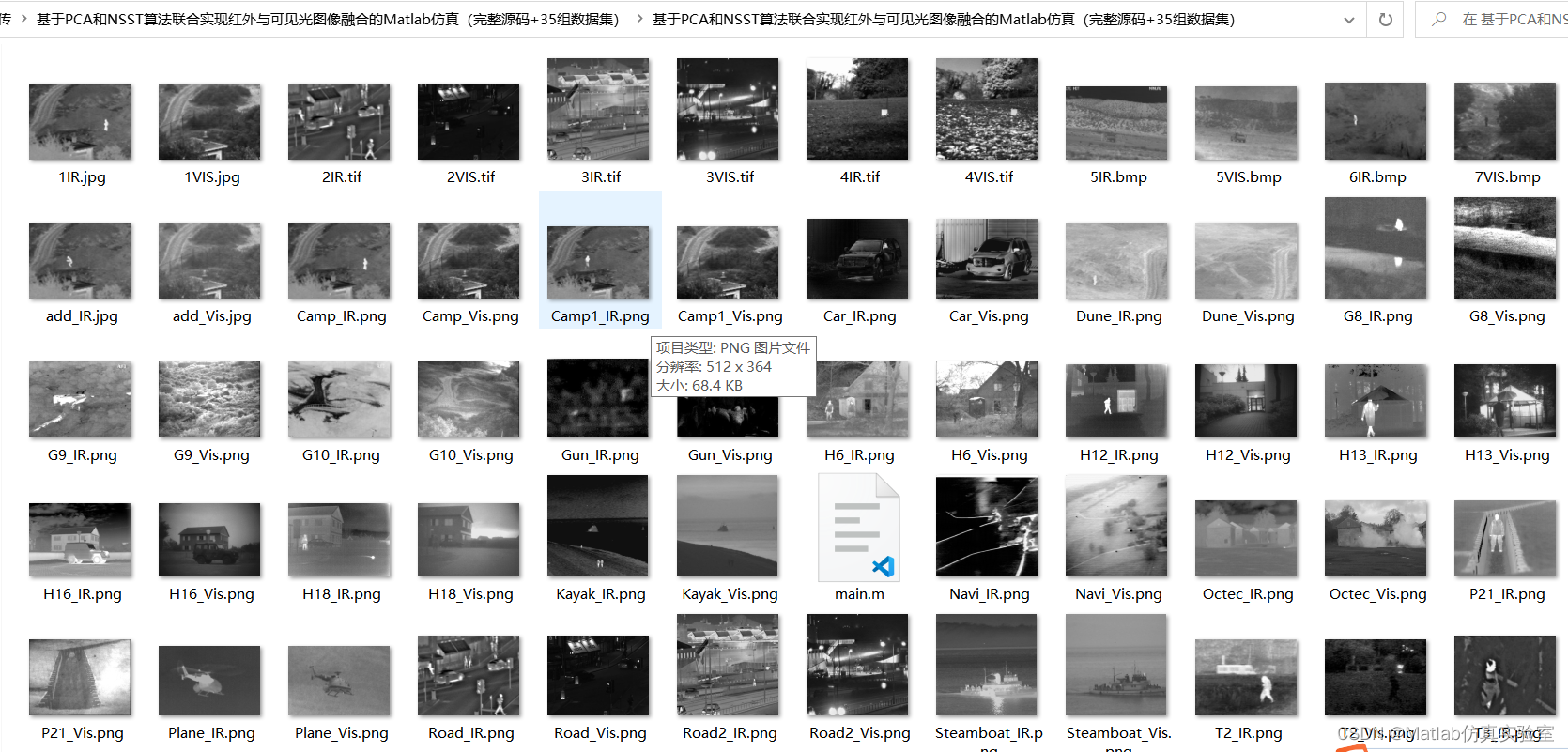

基于PCA和小波算法联合实现红外与可见光图像融合的Matlab仿真(完整源码+35组数据集)

以下是一个使用PCA和小波实现红外与可见光图像融合的Matlab仿真完整源码。源码中只需修改红外图像(IR.bmp)和可见光图像(VI.bmp)名字即可 文章目录 效果展示数据集展示步骤说明完整源码下载地址 效果展示 最终融合效果展示&#x…

HTML5网页设计小案例:帝豪集团总裁办通知网页设计

前言:本案例使用了HTML5和CSS3的知识点,使用HTML5设置了页面的基本布局,使用CSS3给字体设置了颜色,大小,类型,是否居中等内容,使页面设计更加美观。 帝豪集团总裁办通知网页设计HTML5全部代码如…

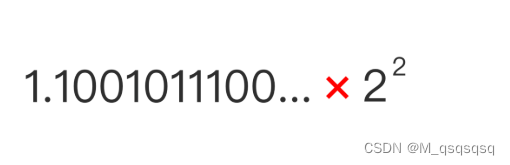

浮点数如何转二进制?

本文转载自CodeSheep这位大佬的推文https://mp.weixin.qq.com/s/LVpvmBO0GY6TC4gwL_12Yw

一、浮点数在计算机中是如何表示的? 学过《计算机组成原理》或者类似《计算机系统》这些课程的小伙伴们应该都知道,浮点数在计算机中的存储方式遵循IEEE 754浮…

如何维护你的电脑:提升性能和延长使用寿命

如何维护你的电脑:提升性能和延长使用寿命 😇博主简介:我是一名正在攻读研究生学位的人工智能专业学生,我可以为计算机、人工智能相关本科生和研究生提供排忧解惑的服务。如果您有任何问题或困惑,欢迎随时来交流哦&…

本地编译rocketmq源码

源码下载

RocketMq下载

运行 这是rocketmq源码大致的业务分层,本地调试主要是启动nameserver和broker,其他的发送和接收的实现代码可直接使用example包中的官方例子,也可以自己编码代码实现。

启动namesrv包下的启动类,Namesrv…

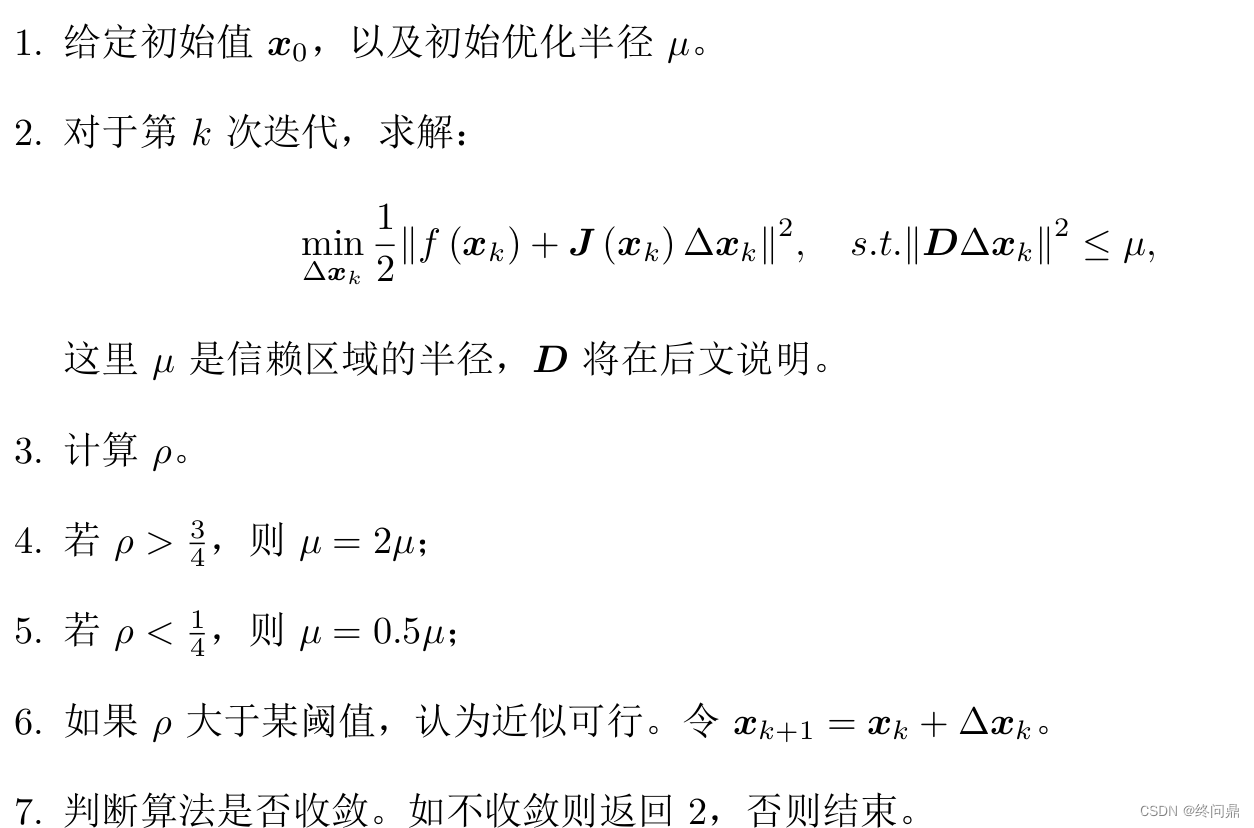

【视觉SLAM入门】4.2 非线性最小二乘理论部分------线搜索,信赖域,最速/牛顿下降法,高斯牛顿,LM等原理推导

"天之道也" 0. 引入1. 最速下降法2. 牛顿法3. (实用)G-N法4. (实用)L-M方法5. 总结 注意: 上一节得到的最小二乘问题,本节来讨论---- 求解非线性最小二乘问题 \color {red}求解非线性最小二乘问题 求解非线性最小二乘问题 0. 引入

求解这个简…

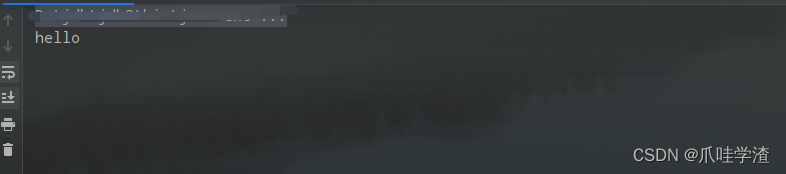

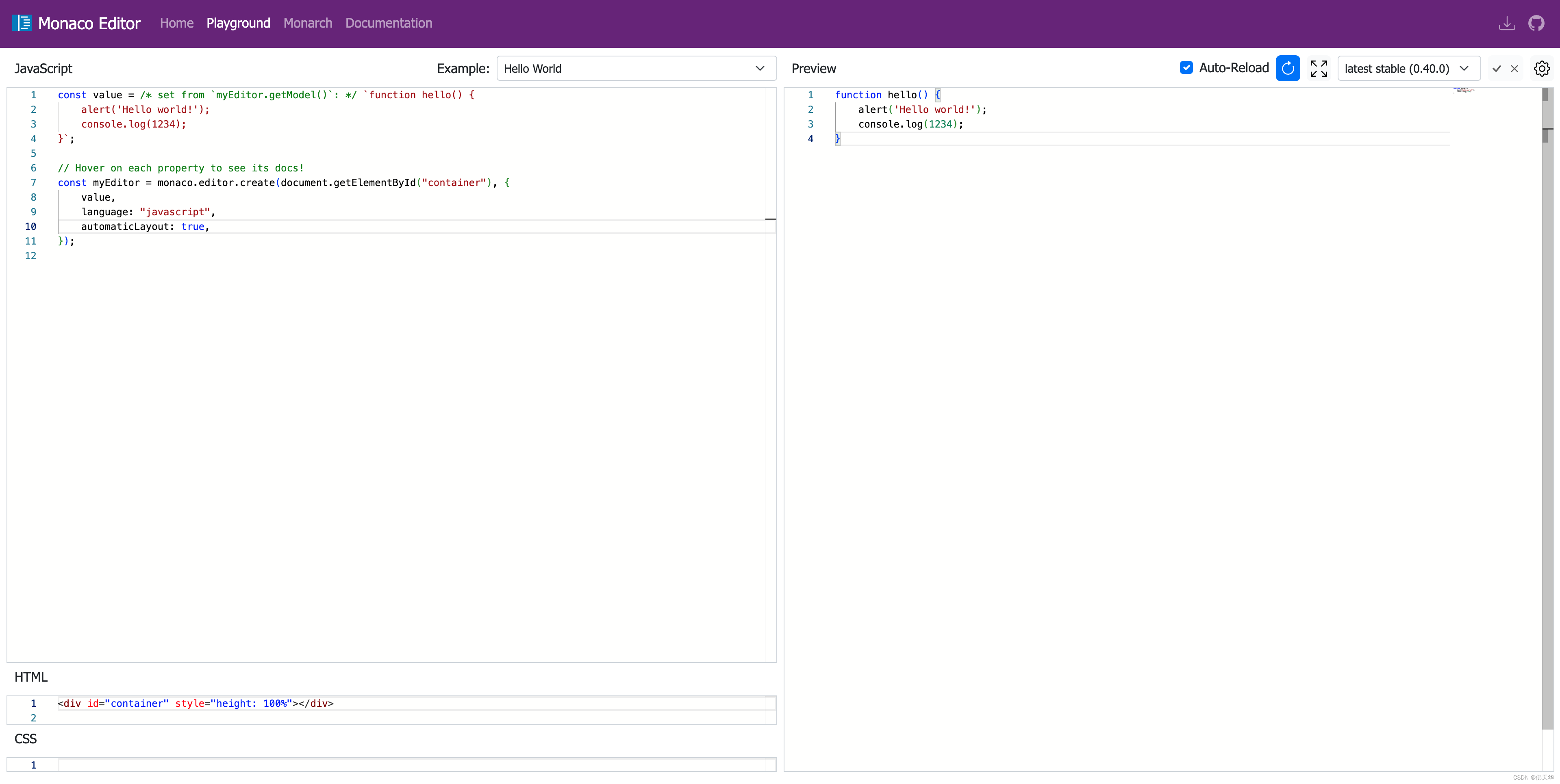

在线 Javascript 代码编辑器,有代码提示功能

分享一个在线代码编辑器,有代码提示功能 github地址: https://github.com/microsoft/monaco-editor

在线预览:https://microsoft.github.io/monaco-editor/playground.html?sourcev0.40.0#example-creating-the-editor-hello-world

效果图…

7. Spring Boot 配置文件

目录

1. 配置文件作用

2. 配置文件格式

3. properties 配置文件说明

3.1 properties 基本语法

3.2 读取配置文件

3.3 缺点

4. yml 配置文件说明

4.1 properties 基本语法

4.2 读取配置文件

4.3 yml 配置不同的数据类型

布尔值

整数值 null 值

配置对象 配置集合

…

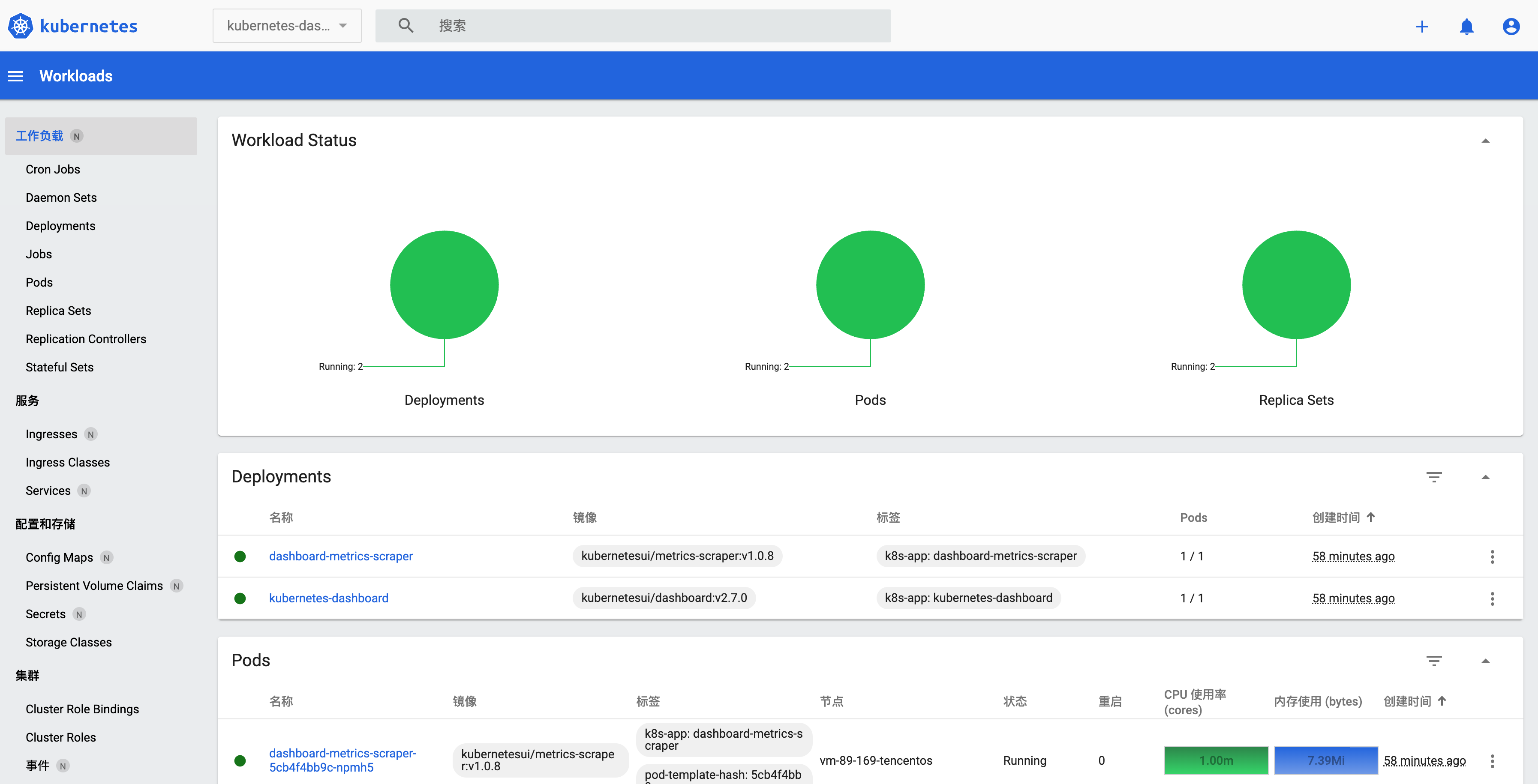

有状态的应用如何部署 1?

前面我们分享很多关于 K8S 的内容,有没有发现 pod 都是无状态,RS / RC 管理的 pod 也是无状态的,我们可以任意删除一个 pod,副本管理器又会马上给我们创建一个 pod

那么如果咱们的这个 pod 是有挂载持久卷的,那么我们…