实验三 触发器及其应用

一 实验目的

1 了解触发器的触发方式(上升沿触发、下降沿出发)及其触发特点;

2 测试常用触发器的逻辑功能;

3 掌握用触发器设计同步时序逻辑电路的方法。

二 实验内容

1 测试双D触发器74HC74的逻辑功能:

测试双D触发器的输入、输出以及时钟脉冲的关系。注意观察输出是在时钟脉冲的什么时刻(上升沿、下降沿、高电平)发生变化的。

(1)D触发器

D触发器的特性方程为Q*=D。

根据D触发器的方程,可得到其特性表,结果如下表所示。

| D | Q | Q* |

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

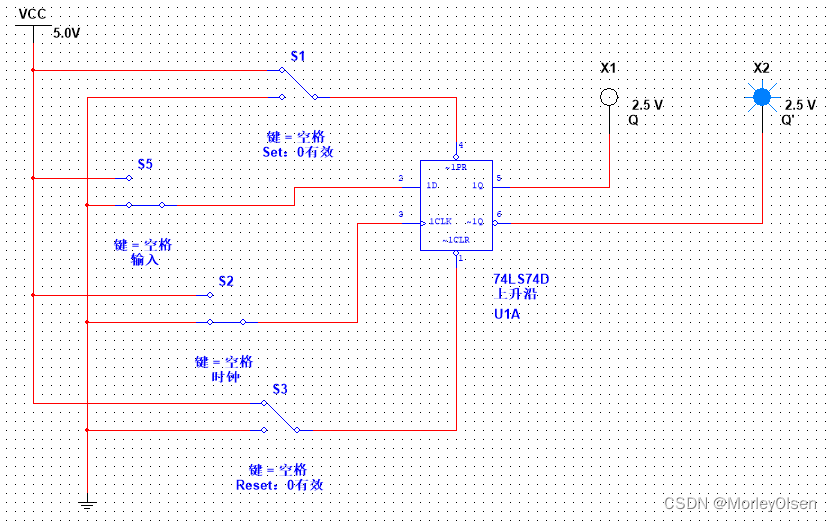

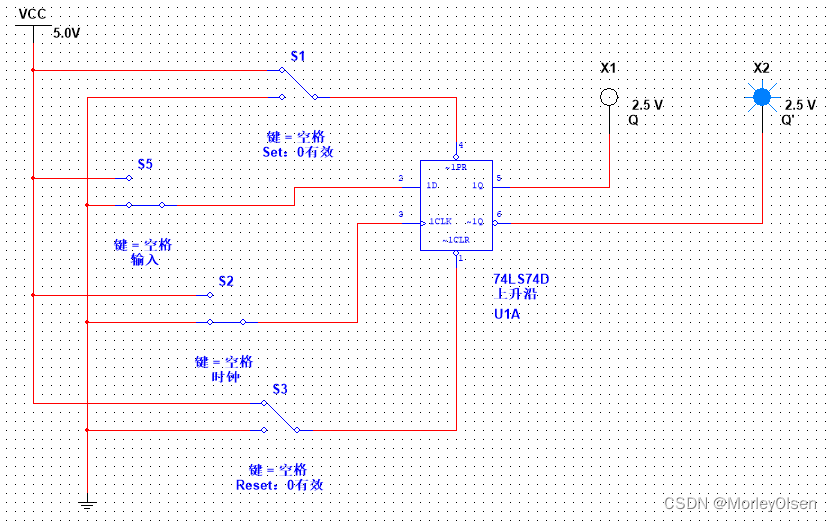

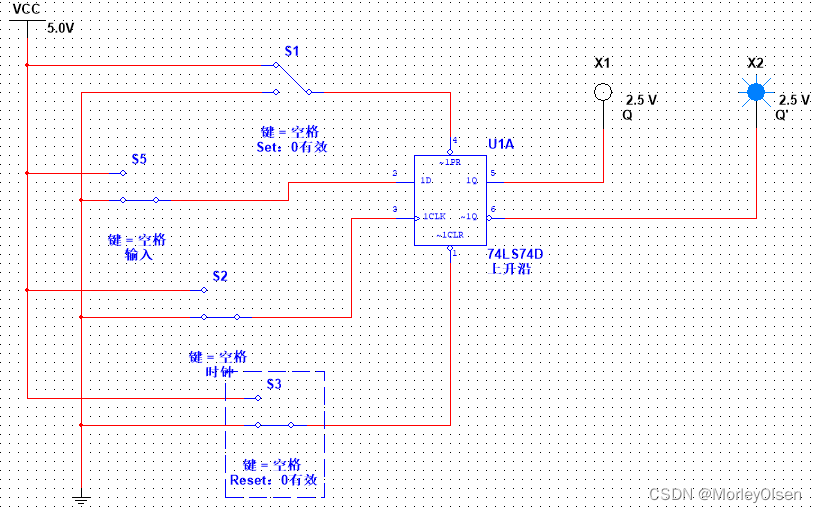

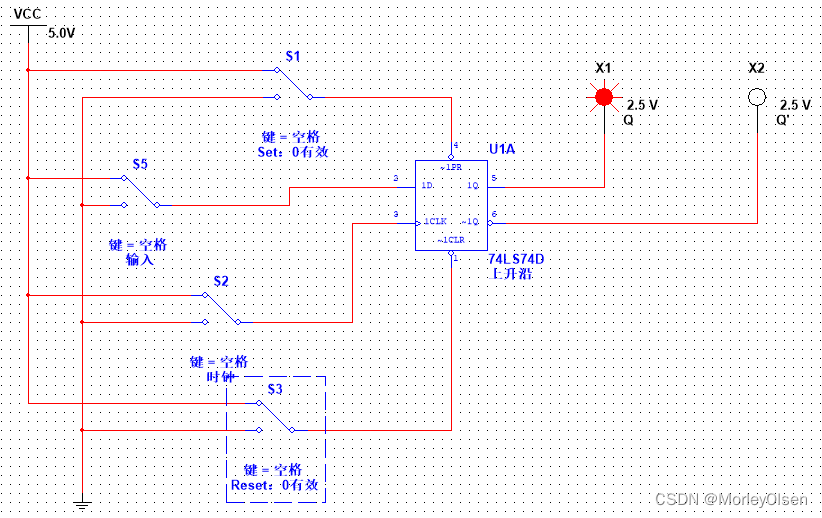

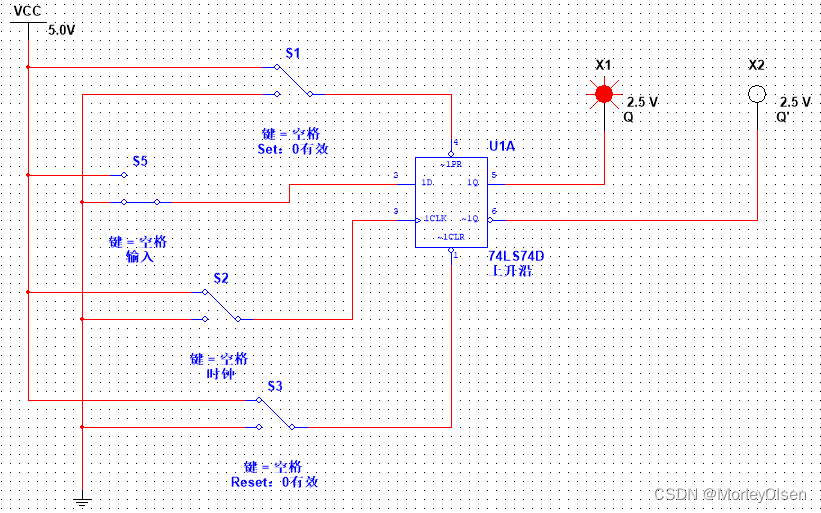

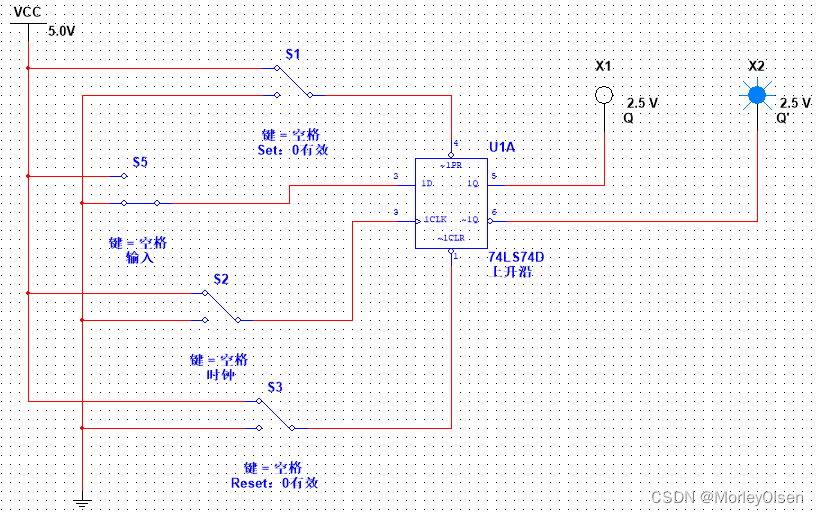

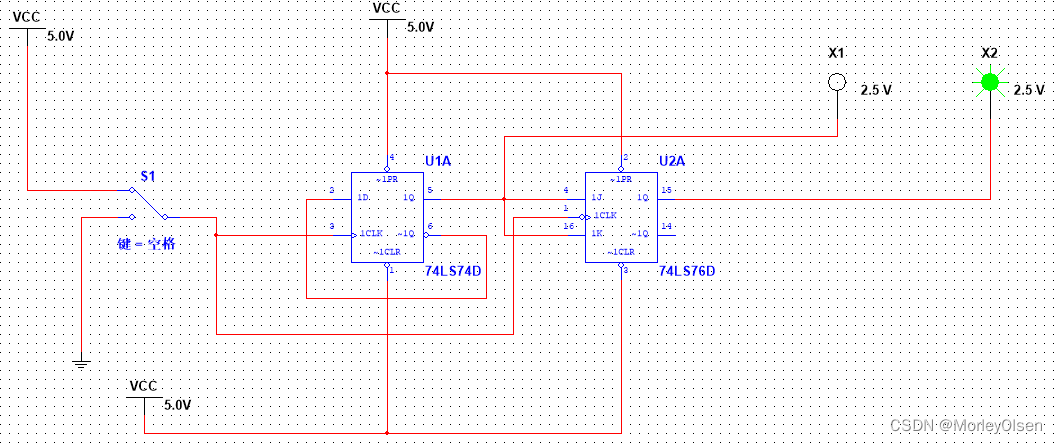

(2)Multisim电路图

(3)仿真模拟过程

在软件中连接成以上电路图后,点击运行即可开始仿真。设计电路时,左侧X1显示Q的状态,有输出时显示红色;右侧X2显示Q*的状态,有输出时显示蓝色。首先需要验证SET、RESET与输出结果(Q和Q*)的关系。然后,可以通过控制时钟的开关来观察上升沿(CLK从0变1)和下降沿(CLK从1变0)时电路的输出情况,验证输入、时钟与输出结果(Q和Q*)的关系。下面将依次展示每个步骤过程及电路对应的输出状态。

初始状态:

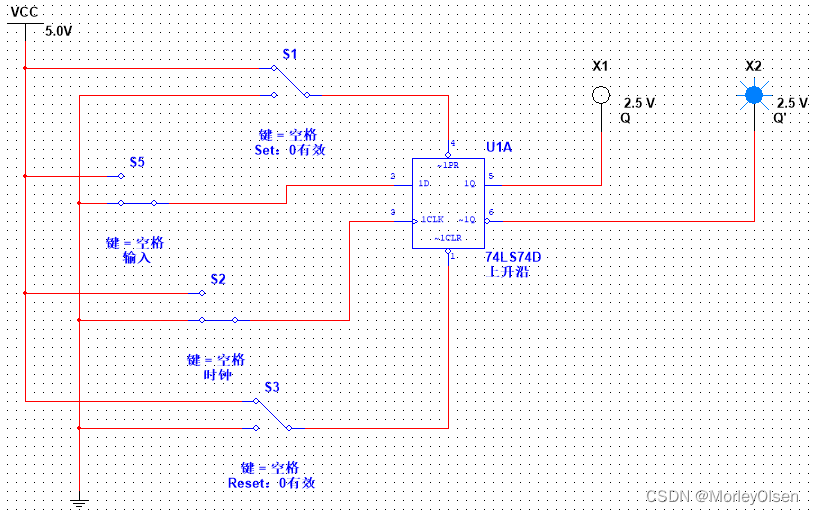

将SET端从1变0:

将SET端从0变1:

将RESET端从1变0:

将RESET端从0变1:

由上述几个步骤可知,当SET和RESET接在VCC上时,均为无效;当SET和RESET接地时,均为有效。即验证完SET、RESET分别与输出结果(Q和Q*)的关系。因此,接下来可以验证输入、时钟与输出结果(Q和Q*)的关系。

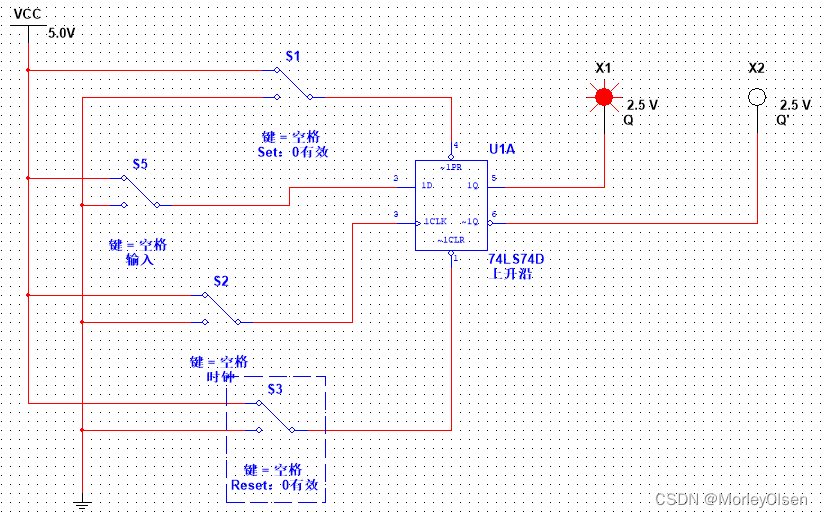

将输入端从0变1,紧接着将时钟端从0变1:

将时钟端从1变0:

再次将时钟端从0变1:

再次将时钟端从1变0:

由上述几个步骤可知,当CLK输入一个上升沿时,因为输入为1,所以Q输出为有效,Q*输出为无效。且后续不论CLK怎么变化,输出状态仍然保持不变。

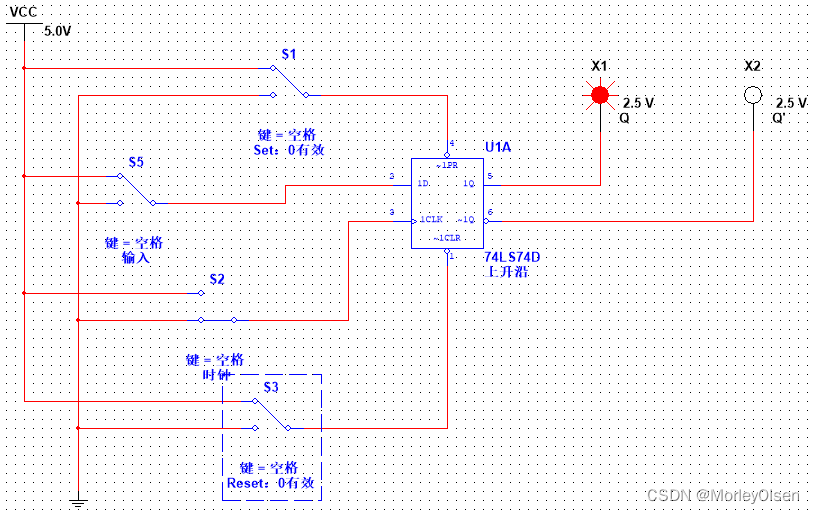

将输入端从1变0:

将时钟端从0变1:

由上述几个步骤可知,当输入端从1变0时,由于CLK没有变化,输出状态仍然保持不变。但是当CLK输入一个上升沿时,因为输出为0,所以Q输出为无效,Q*输出为有效。

(4)实验结论

由仿真模拟过程可知,双D触发器的输出是在时钟脉冲的上升沿时刻发生变化的。

并且,如果多次调试CLK、SET、RESET和输入端,可以得到双D触发器中输出、输出以及时钟脉冲的关系,结果如下表所示。

| 输入 | CLK | SET | RESET | Q | Q* |

| 1 | ↑ | 1 | 1 | 1 | 0 |

| 1 | 其他情况 | 1 | 1 | 保持原有状态 | 保持原有状态 |

| 1 | 其他情况 | 1 | 0 | 0 | 1 |

| 0 | ↑ | 1 | 1 | 0 | 1 |

| 0 | 其他情况 | 1 | 1 | 保持原有状态 | 保持原有状态 |

| 0 | 其他情况 | 0 | 1 | 1 | 0 |

2 设计三分频电路:

用双D触发器设计一个同步三分频电路。用示波器观察并记录时钟脉冲CLK和触发器输出Q1、Q2的波形。(按三进制计数器来设计)

(1)设计思路

三分频电路可以通过对待分频时钟上升沿触发计数器进行计数来实现,具体实现方法如下:进行模3计数,在时钟上升沿进行加 1操作,比如可以在计数器计数到1时,输出时钟进行翻转,计数到2时再次进行翻转,计数到 2时清零,从头开始计数。这样实现的三分频占空比为1/3。占空比为高电平的时间与周期的比值。

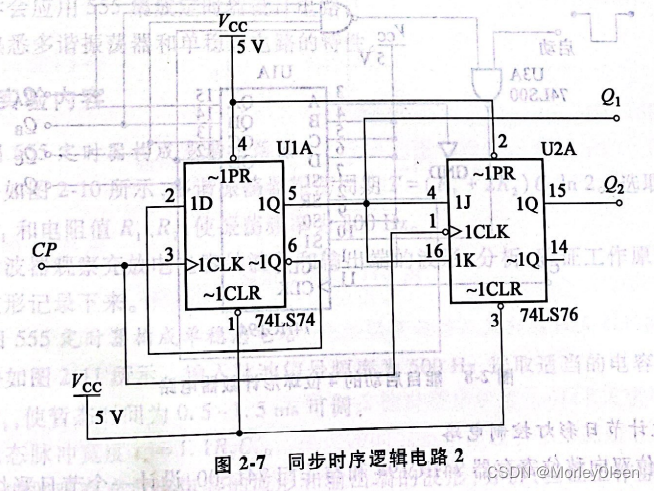

(2)理论电路图和Multisim电路图

理论电路图:

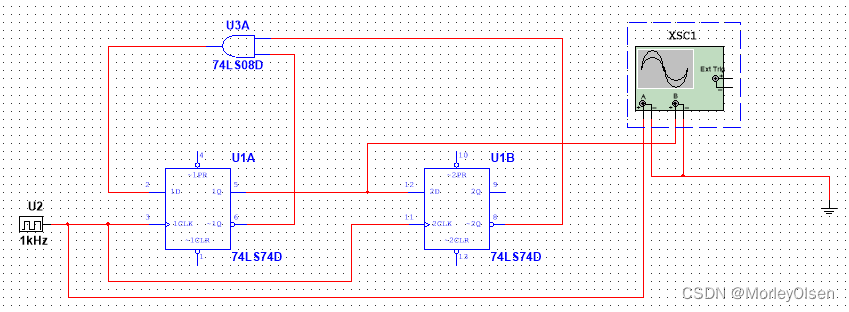

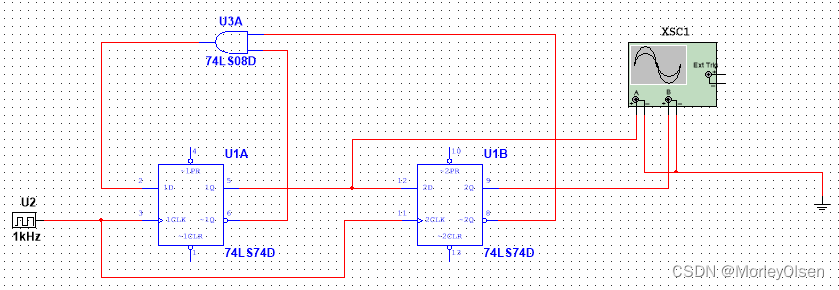

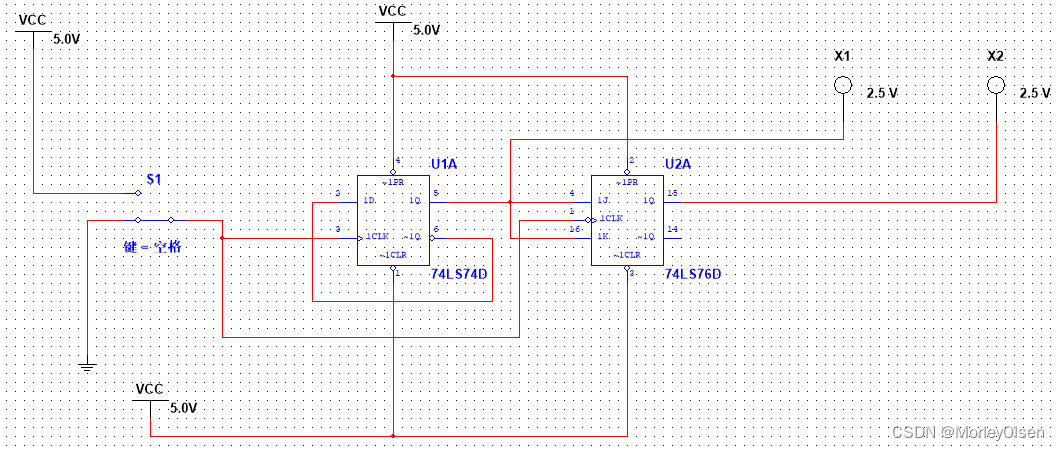

Multisim电路图:

可观察Q2与CLK周期关系的电路:

可观察Q1与CLK周期关系的电路:

可观察Q1与Q2周期关系的电路:

(3)实验结论

最终设计的三分频电路如上图所示。并且,实验3所观察分析的电路是本实验所设计的电路,因此仿真模拟过程在实验3中详细阐述。

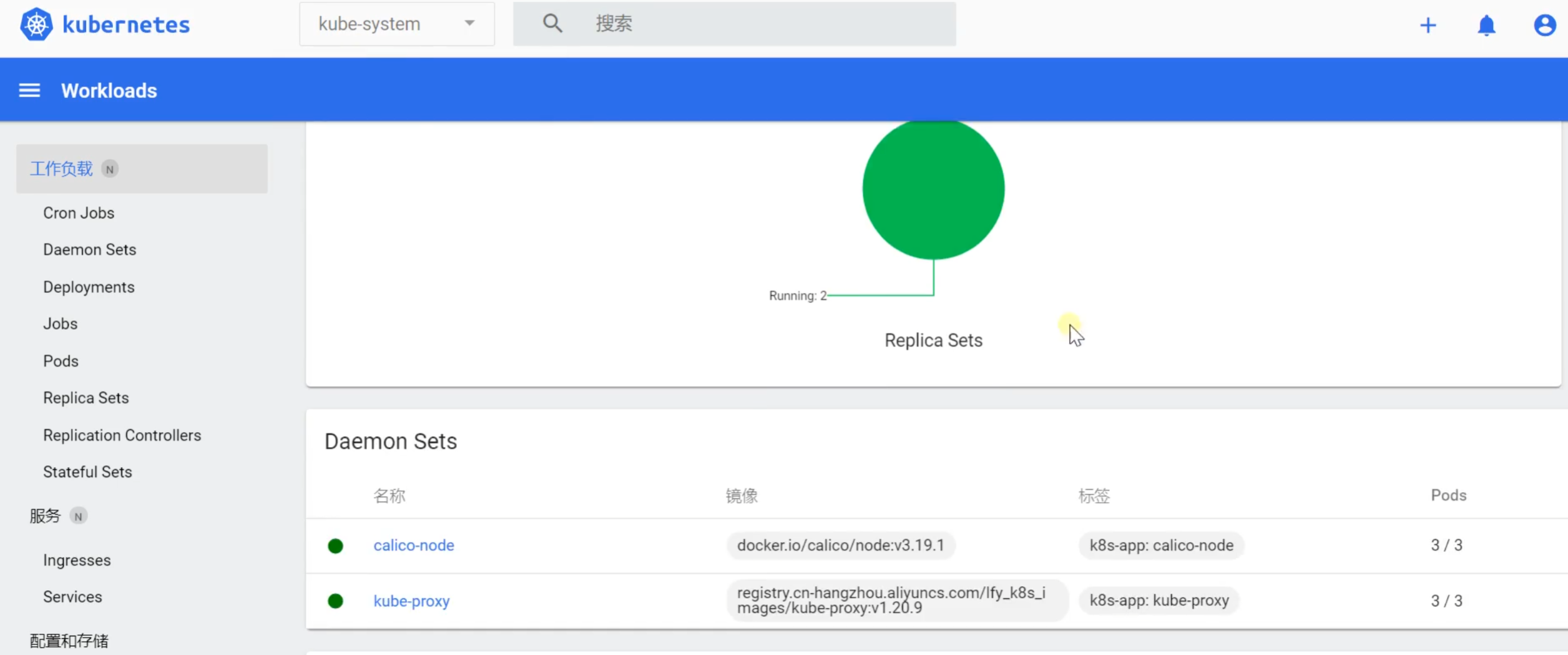

3 观察分析同步时序逻辑电路1:

分析同步时序电路的逻辑功能,用示波器观察并记录CLK、Q1、Q2的波形。

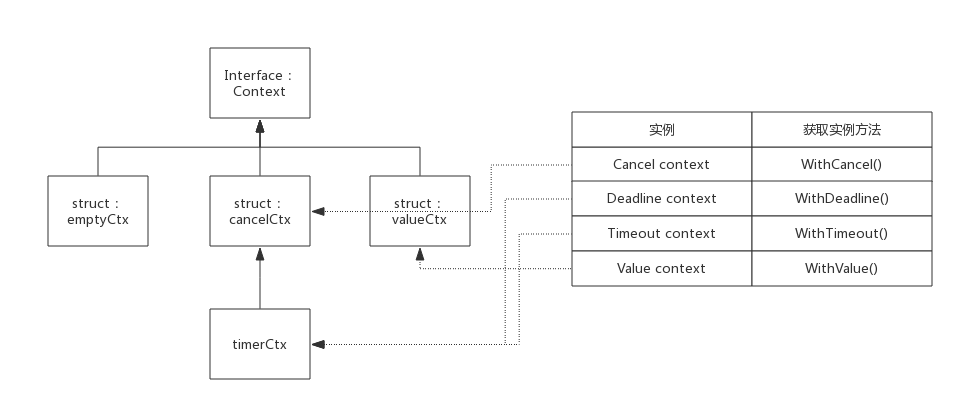

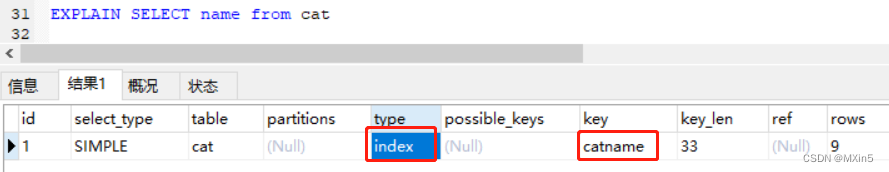

(1)逻辑功能分析

驱动方程:D1=Q1‘Q2’ D2=Q1

特性方程:Q1*=D1 Q2*=D2

状态方程:Q1*=Q1‘Q2’ Q2*=Q1

令输出Y1=Q1,Y2=Q2,所以输出方程:Y1=Q1‘Q2’ Y2=Q1

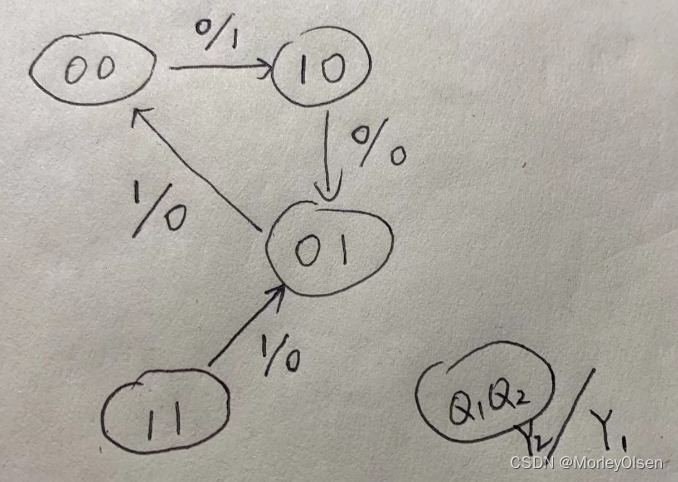

状态转换图如下图所示。可以发现电路能自启动。

(2)仿真模拟过程

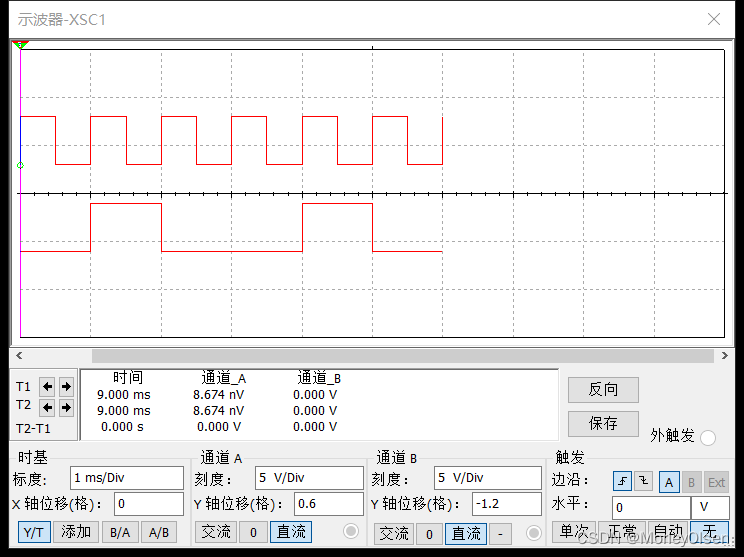

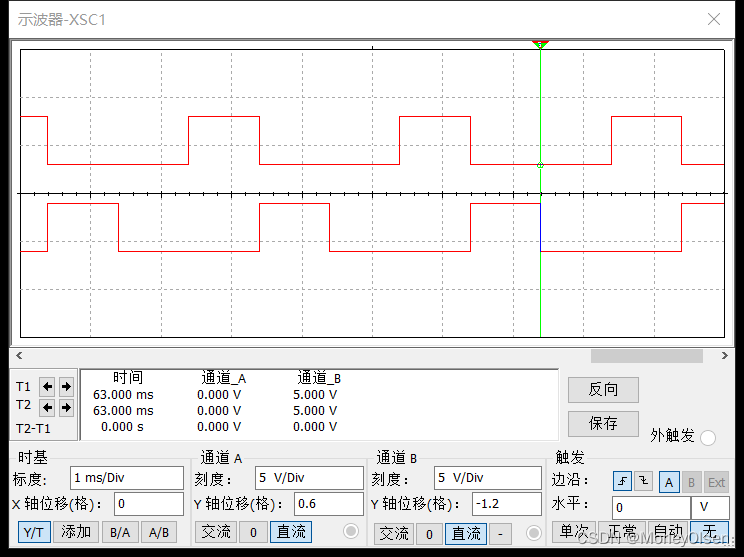

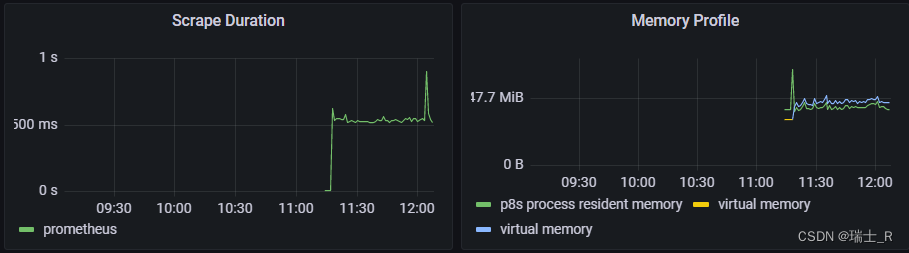

可观察Q2与CLK周期关系的电路:

通过观察示波器图像可知,Q2的占空比为1/3,Q2的周期是CLK周期的三倍。

可观察Q1与CLK周期关系的电路:

通过观察示波器图像可知,Q1的占空比为1/3,Q1的周期是CLK周期的三倍。

可观察Q1与Q2周期关系的电路:

通过观察示波器图像可知,Q1的占空比为1/3,Q2的占空比为1/3,Q1的周期和Q2的周期相同;但是Q1和Q2在出现高电平的时刻不同,Q1的规律为0-1-0,Q2的规律为0-0-1。

(3)实验结论

Q1和Q2的占空比均为1/3,周期相同且均为CLK周期的三倍;但是二者在出现高电平的时刻不同,Q1的规律为0-1-0,Q2的规律为0-0-1。

4 观察分析同步时序逻辑电路2:

分析同步时序电路的逻辑功能。用示波器观察并记录CP、Q1(74LS74的1Q端)、Q2(74LS76的1Q端)的波形。说明各触发器的翻转条件。

(1)逻辑功能分析

驱动方程:D = Q1’ J = K = Q1

特性方程:Q1* = D Q2* = JQ2’ + K’Q2

状态方程:Q1* = Q1’ Q2* = Q1Q2’ + Q1’Q2 = Q1 ⊕![]() Q2

Q2

令输出Y1=Q1,Y2=Q2,所以输出方程:Y1=Q1’ Y2=Q1 ⊕![]() Q2

Q2

由于D触发器是上升沿触发,JK触发器是下降沿触发,因此Q1和Q2的变化不同步,需要单独对CLK的上升沿和下降沿时刻进行独立的分析,需要注意Q2的暂存情况和Q1的变化情况。通过分析状态转换可得到真值表,结果如下表所示。

| 操作次数 | CLK | Q1 | Q2 |

| 0 | 初始状态,无输入 | 0 | 1 |

| 1 | ↑ | 1 | 1 |

| 2 | ↓ | 1 | 0 |

| 3 | ↑ | 0 | 0 |

| 4 | ↓ | 0 | 0 |

| 5 | ↑ | 1 | 0 |

| 6 | ↓ | 1 | 1 |

| 7 | ↑ | 0 | 1 |

| 8 | ↓ | 0 | 1 |

后续模拟仿真实验将验证是否符合上表的分析情况。

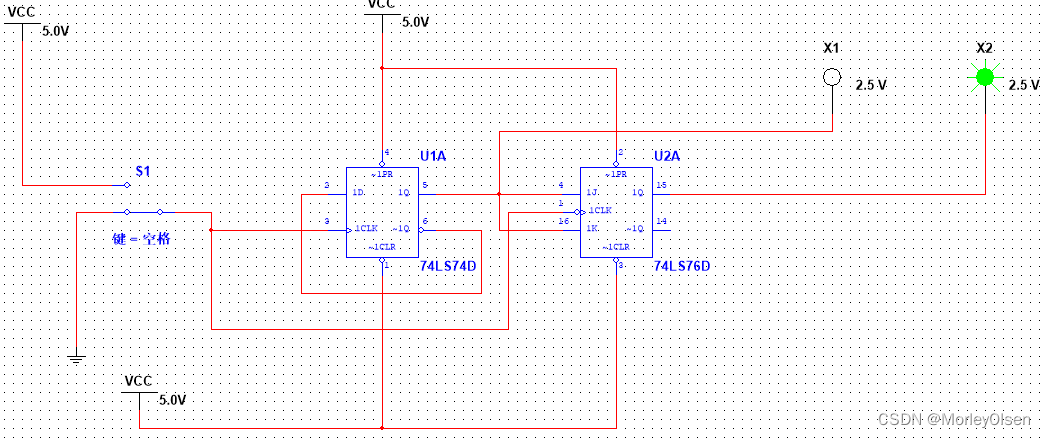

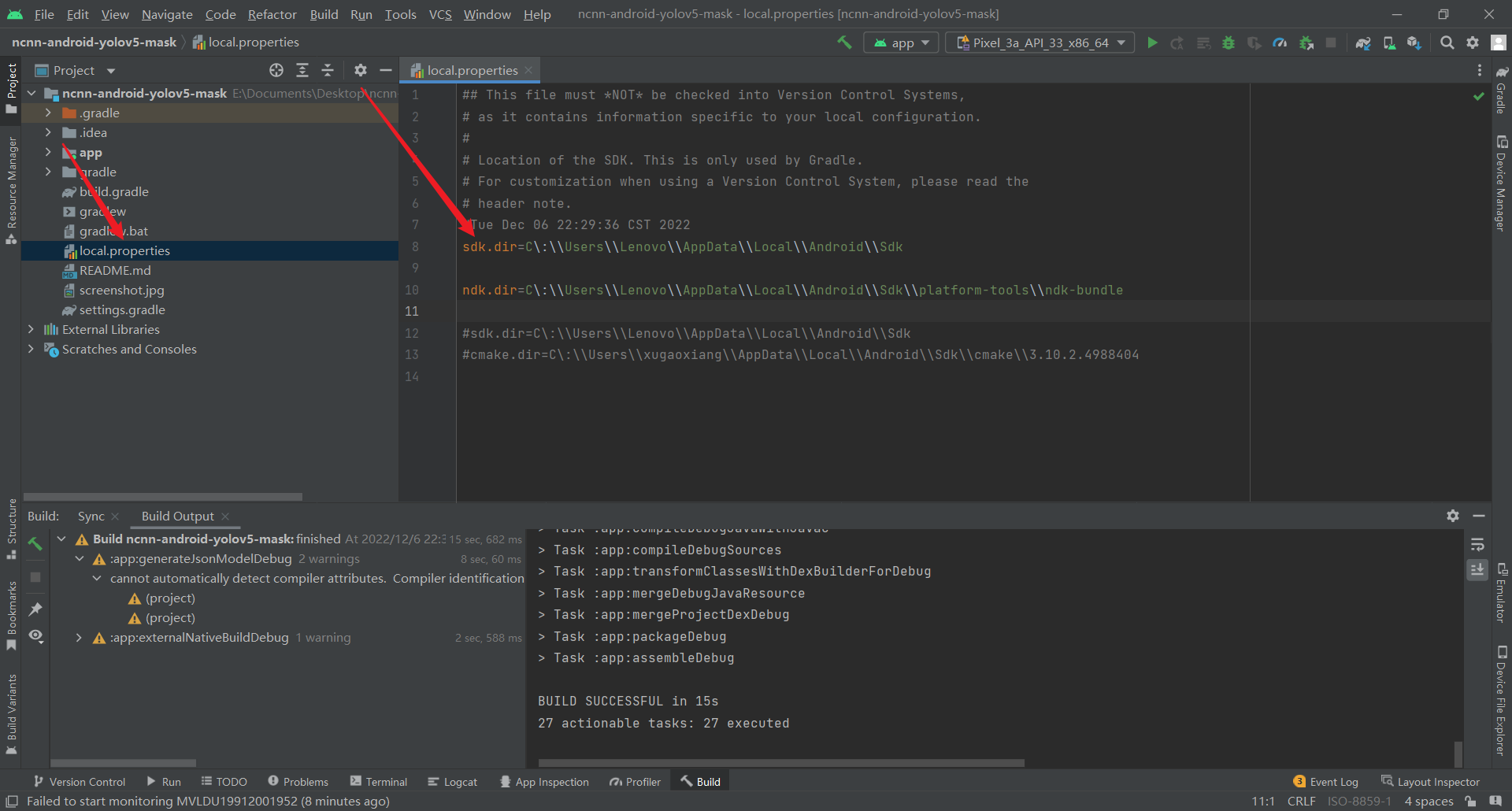

(2)理论电路图和Multisim电路图

理论电路图:

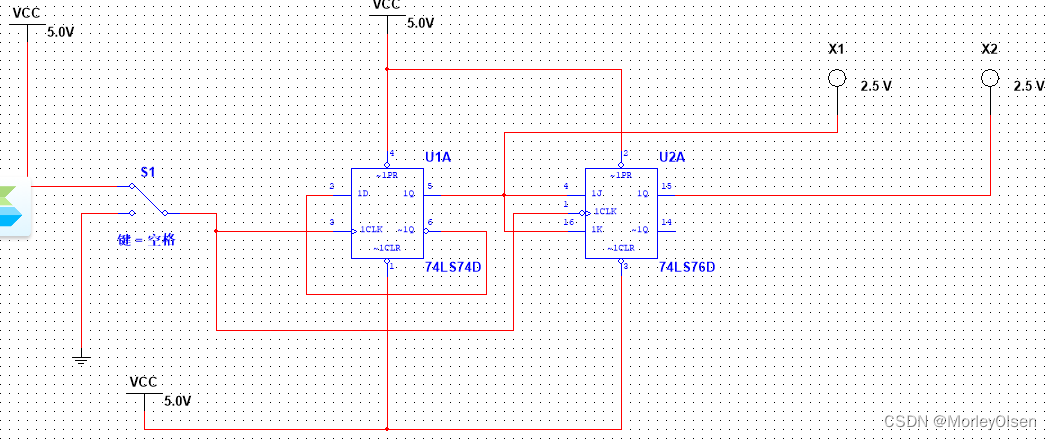

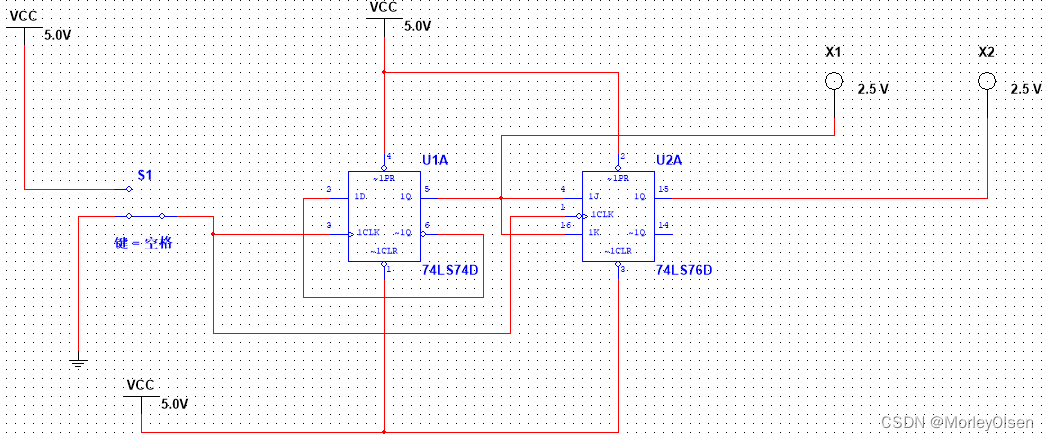

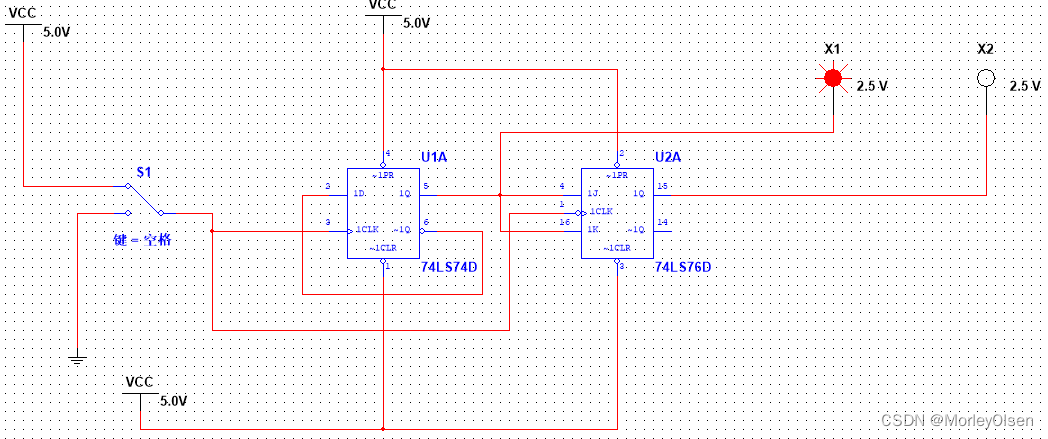

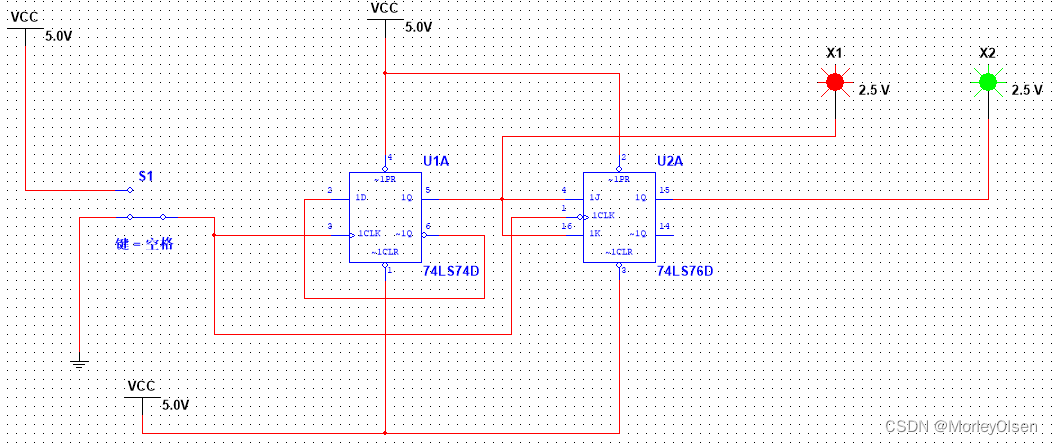

Multisim电路图:

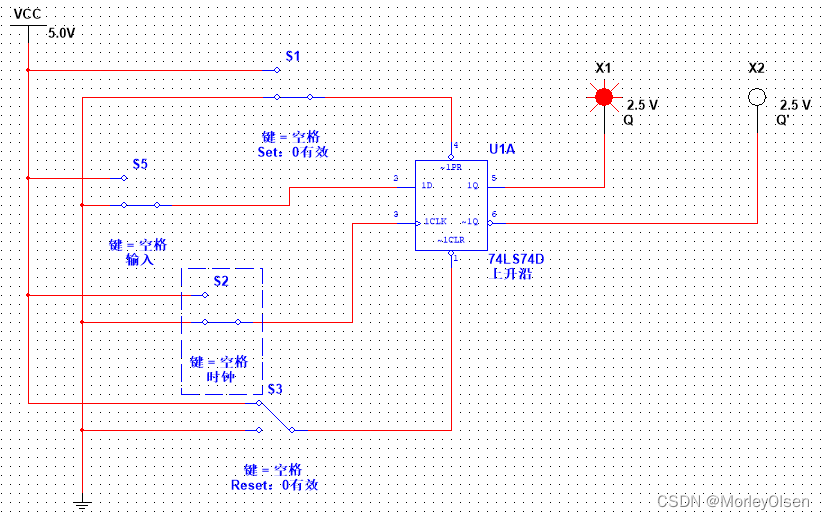

(3)仿真模拟过程

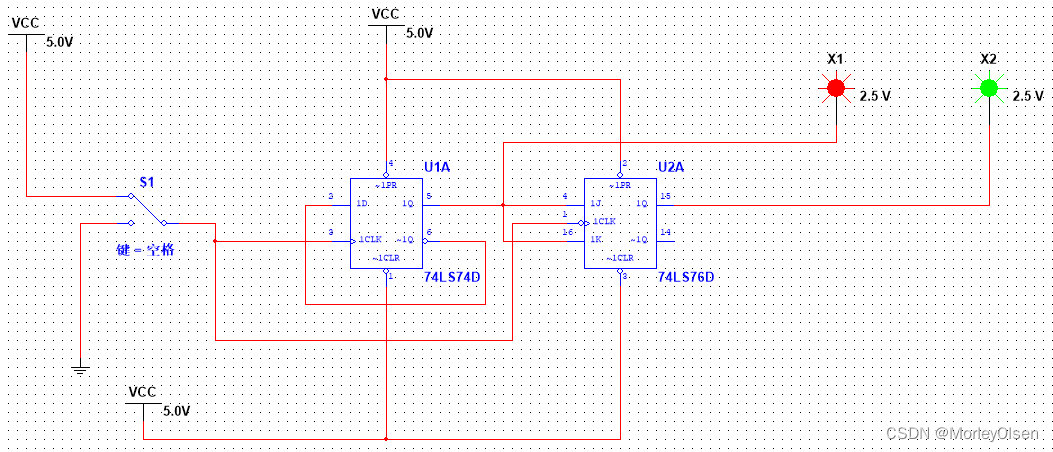

根据理论分析时的CLK状态,依次操作单刀双掷开关控制CLK的上升沿和下降沿时刻,观察Q1和Q2的输出情况。各个时刻的电路输出状况依次为下图所示。

0——初始状态:

1——第一个上升沿:

2——第一个下降沿:

3——第二个上升沿:

4——第二个下降沿:

5——第三个上升沿:

6——第三个下降沿:

7——第四个上升沿:

8——第四个下降沿:

综上所述,仿真模拟实验与理论分析真值表完全拟合。

(4)各触发器的反转条件

对于所有的触发器,如果想要实现翻转情况,需要具备如下的条件:一是触发脉冲信号,二是触发器输入信号状态要满足输出状态翻转条件,三是触发器的置位端及清零端禁止使能。

本实验的D触发器的反转条件为:CLK输入一个上升沿信号。

本实验的JK触发器的反转条件为:Q1=1,同时CLK输入一个下降沿信号。

(如果Q2=0,那么需要Q1=1,同时CLK输入一个下降沿信号;如果Q2=1,那么需要Q1=1,同时CLK输入一个下降沿信号)

三 实验总结

总体而言,本次模拟仿真实验与理论情况完全拟合,实验效果良好。

通过本次触发器实验,我学习了分析时序电路的步骤为:写出驱动方程——把驱动方程带到触发器的特性方程——得到状态方程——将所有可能的输入带到状态方程——得到次态——得到状态转换图。

同时,基于实验中对D触发器和JK触发器的设计与连线,我对这两个触发器特性方程进行了再次巩固,也更加理解了四句口诀的含义。

![【无需注册账号】只需两步, Ai Studio上也可以玩[ChatGPT]了](https://img-blog.csdnimg.cn/img_convert/b92a0899d329d252c5d708cc0a1df9e1.png)

![[附源码]Python计算机毕业设计SSM基于的校园失物招领平台(程序+LW)](https://img-blog.csdnimg.cn/eecb39d791844f34881801cb954f4124.png)