什么是PCIE

PCIe Peripheral Component Interconnect express

快速外部组件互联 高速串行计算机扩展总线标准

处理器系统的局部总线 连接外部设备

- 高速、低时延

- 支持热插拔

- 可靠

- 扩展性好

- 复杂度高

- 点对点串行连接

附一个博主写的总结文章,非常好

《PCI EXPRESS体系结构导读》读书笔记之存储器域与PCI总线域

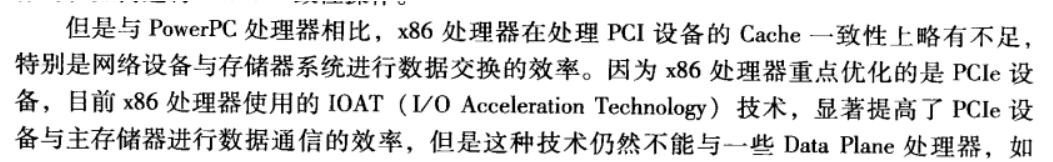

PCI EXPRESS体系结构导读》读书笔记之X86处理器的HOST主桥

在Intel的x86处理器系统中,所有的外部设备都使用PCI总线管理。

Device ID:厂商所生产的具体设备 Vendor ID代表PCI设备的生产厂商

Revision ID寄存器记载PCI设备的版本号 Class Code寄存器记载PCI设备的分类

Cache Line Size寄存器 PCIe设备在进行数据传送时,在其报文中含有一次数据传送的大小,PCIe总线控制器可以使用这个大小,判断数据区域与Cache行的对应关系。

使用Subsystem ID和Subsystem Vendor ID来区分设备

有些PCI设备在处理器还没有运行OS之前,需要完成基本的初始化设置

PCIe设备使用INTx中断消息,模拟PCI设备的中断信号

使用pci_resource_start 函数获得BAR空间对应的存储器域的物理地址,而不能使用从BAR寄存器中读出的地址。

DFS算法 深度优先 遍历PCI树

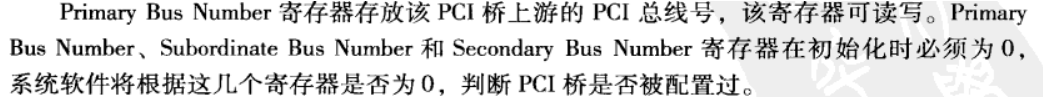

访问PCI设备的配置寄存器 一定要有Bus Number 、Device Number 、Function Number和Regiseter Number

负向译码 在没有任何PCI设备响应时PCI-to-ISA桥,PCI桥可以作为负向译码设备。

存储器写使用Posted方式,存储器读使用Non-Posted方式

PCEI 链路

RC(Root Complex)主要功能与PCI总线中的HOST主桥类似,但增加了许多功能。

Intel使用RC管理PCIe总线,不仅管理 PCIe设备的数据访问,还包括访问控制,错误处理和虚拟化技术等一系列内容。

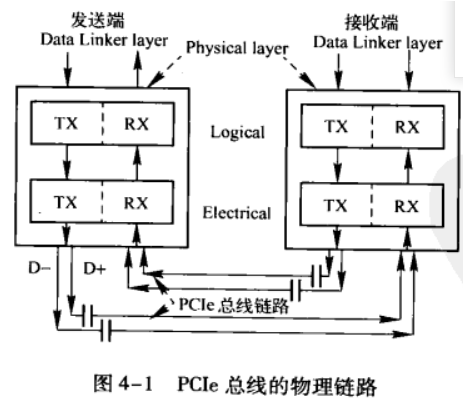

高速差分总线 更高时钟频率,更少的信号线 端到端连接

Lane 数据通路 两组差分信号,共4根信号线 差分信号抗干扰能力强,外部干扰噪声影响较小,能有效抑制电磁干扰

弱点:传送延时

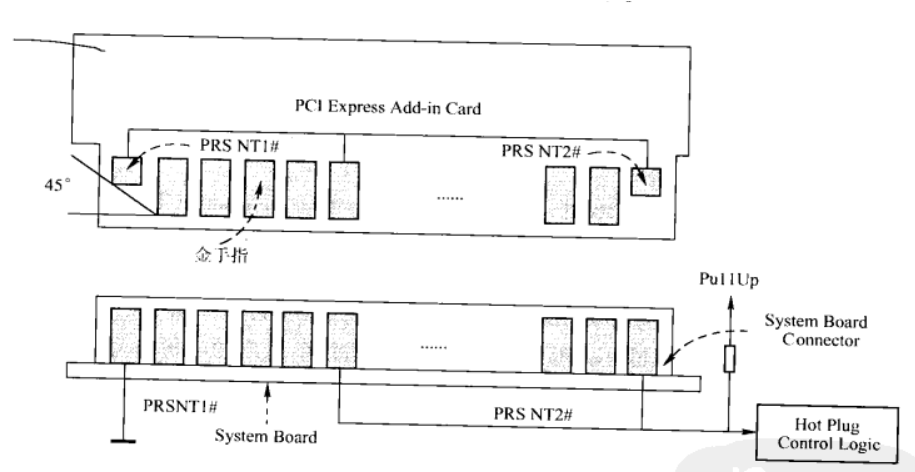

热拔插功能 Add-In卡需要使用**“长短针”**结构。

switch

Switch可以采用Crosslink连接模式。使用非透明桥仅解决 两个处理器间的数据通路问题 ,最终解决方法是 使用MR-IOV技术。要求:Switch具有多个上游端口分别与不同的RC互连。

基于PCIe总线的设备,也称为EP(Endpoint)。

3种VC仲裁方式,分别为

Strict Priority绝对优先级,

RR(Round Robin)轮询

WRR(Weighted Round Robin)加权轮询算法。