1. 硬件构成、工作原理、评价指标

2.主存储器

- 基本构成为DRAM&SRAM+ROM,

- 工作原理为串行访问

- 特点是采用多体交叉提高读取速度

RAM工作原理

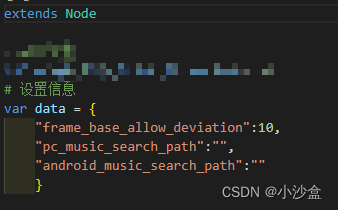

- SRAM的读写过程如下:

-

WE控制读写;

-

CS为片选信号;

-

VCC为接地端;

-

GND为接地端。

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-fI0aVOXK-1689585466989)(./assets/IMG_20230717_140900-1689574197955-2.jpg)]](https://img-blog.csdnimg.cn/895f8014ade94b10a650a83ef6879b1a.png)

- tRC表示连续读周期的间隔;

- tA表示从地址有效到输出有效;

- tCO表示从片选有效到输出有效;

写周期也类似

- tWC为write cycles之间的间隔;

- tAW=地址有效到片选信号的间隔;

- 片选有效同时WE信号有效(WE=0);

- tDTW=写信号有效到输出数据有效;(为了防止输入被遗漏,输出信号Dout必须在输入信号Din有效之前生效,DIN失效之后失效);

- 为了保证输入写入正确的地址,DIN必须在片选信号和写入信号实效之前产生,tDW表示DIN有效到CS&WE实效的间隔;

- tDH表示片选失效到完成写入的间隔;

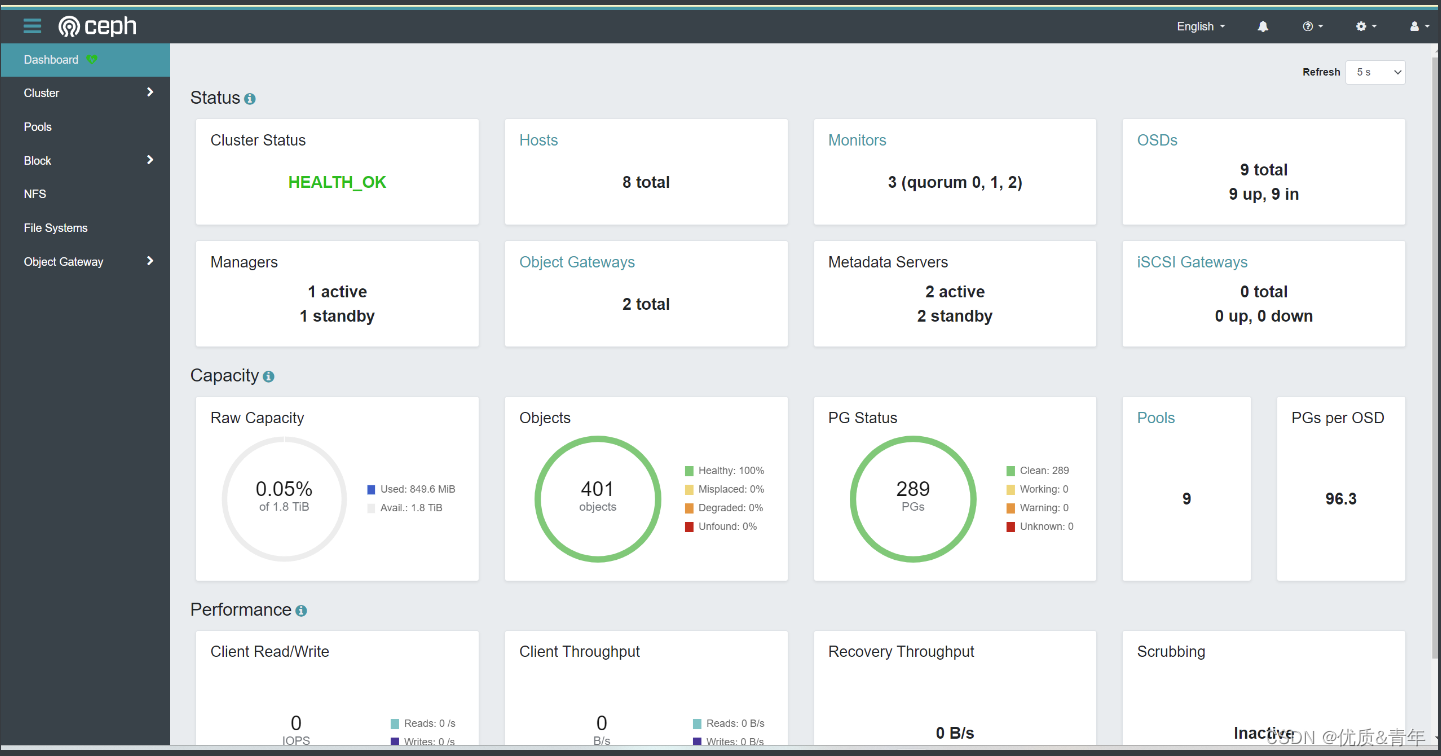

DRAM的读出与写入更为简单,分3管式和单管式

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-7j0GMNK4-1689585466989)(./assets/IMG_20230717_145924.jpg)]](https://img-blog.csdnimg.cn/7e3856845b964dcf8b85f9bbfa3b3e64.png)

- 三极管在C极有效时,BE导通,否则BE断开;

- 预充电信号有效,T4导通,读数据线开始为VDD高电平,

-

读取时,读选择线有效,

若Cg有电荷,三极管VCE>0,则T1导通,于是读数据线通过T2,T1接地,变成0电平,读出0;若Cg无电荷,VCE=0,T1截止,读数据线为高电平,读出1;

-

写入时,写选择线有效,T3导通,

若写数据线有效,Cg最终被充电,实际读出为0;

若无效,Cg被放电,无电荷,实际读出为1;

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-Xz96jAQ0-1689585466990)(./assets/IMG_20230717_150011.jpg)]](https://img-blog.csdnimg.cn/94b60e6253574d2eb4f88a4dac18475d.png)

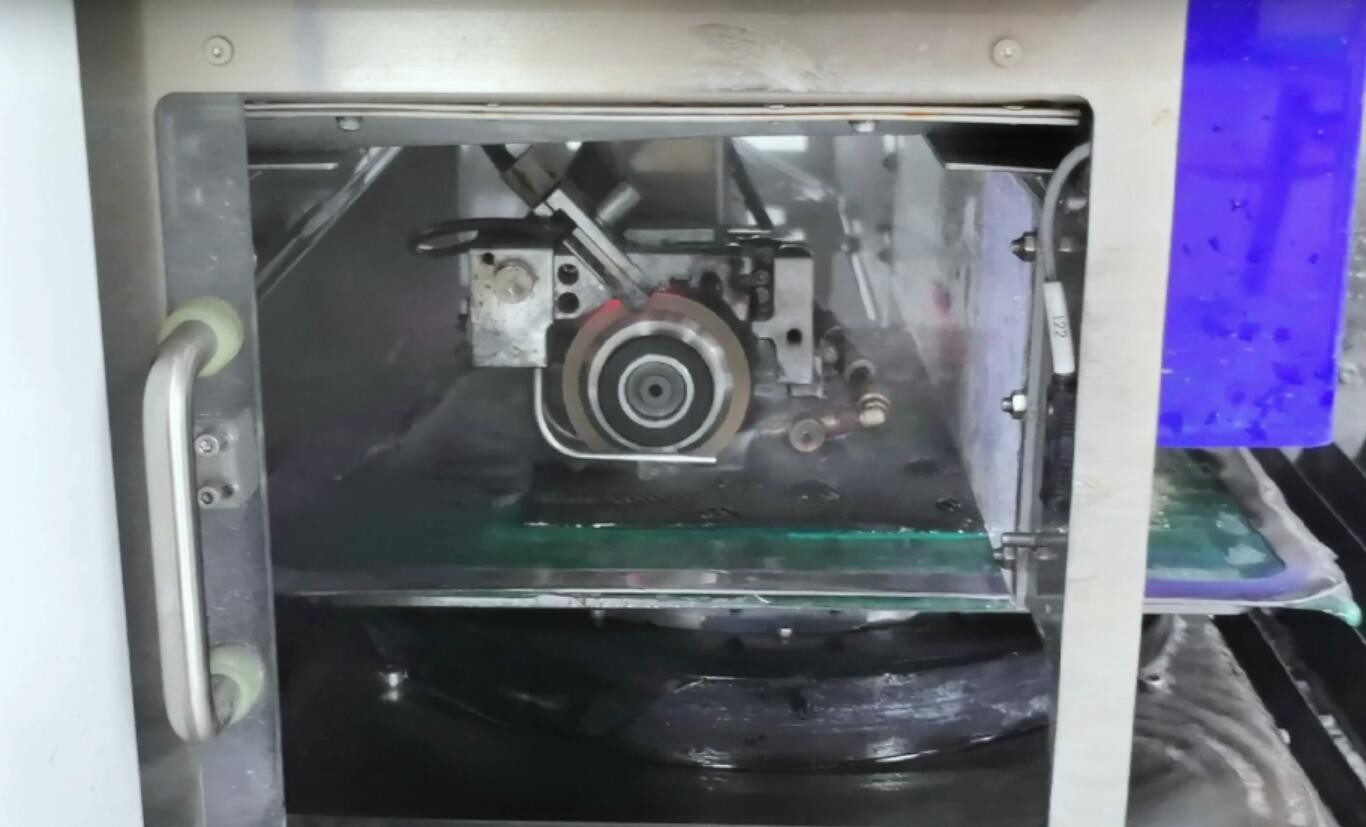

- 写入时,字线有效,T导通,dataline有效,Cg为1;dataline无效,Cg为0;

- 读出时(数据线不充电),字线有效,若Cg带电荷,数据线读出1,Cg不带电荷,数据线读出0;

- 如何区分读写信号?

实际实现的时候,阵列单元共用1条读数据线+1条写数据线

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-MRNbTCmf-1689585466990)(./assets/IMG_20230717_152820.jpg)]](https://img-blog.csdnimg.cn/087c4932a8d445cb8278248ec9adbaf6.png)

- RAS为行片选,CAS为列片选,WE为写信号,WE=1表示读

- 同理,Dout必须在CS和WE有效之后,无效之前生效,tRD-CAS表CAS无效到WE无效的time interval,tCAS-out= time interval of CAS无效到out无效;(言下之意=CAS无效之后WE才能无效,WE无效Dout才能无效)

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-zzh5vSt8-1689585466991)(./assets/IMG_20230717_152848.jpg)]](https://img-blog.csdnimg.cn/fa55207ba9a24eeca60aa0c2b5840407.png)

- WE=0表示写,

WE=1表示读 - WE、CAS、RAS一定在DIN失效之后失效;

- 为了保证正确杜写入内存阵列,CAS(选择列后读取Din到阵列),DIN必须在RAS之前生效,WE同理;

RAM动态刷新

- 电信号随时间衰减

| 集中刷新 | 分散刷新 | 异步刷新 | |

|---|---|---|---|

| 存取周期 | t存取 | 2t存取 | t存取 |

| 死时间(每行) | t存取*行数 | 0 | t存取 |

| 刷新周期(均有效) | t刷新max | 2t存取*行数 | t刷新max |

| 特点 | 存取时间短,死时间长 | 存取时间长,死时间短/无 | 存取时间短,死时间短 |

多体交叉

多存储器体,被交叉的是体号,

高位交叉=高位为体号,低位为体内地址,

此时,顺序访问内存中的连续地址,相当于存储体串联,需要1个存储体一个存储体访问,

这会带来一个问题:访问内存中一个地址的存取周期T=存取时间+恢复时间,而利用总线的时间r<存取时间<T,

这就导致总线大部分时间为空闲状态;

为了充分利用总线时间,采用低位为体号的形式——低体交叉;

采用流水线方式,各存储体的存储共用 MAR+MDR+总线,易见前提为T>=mr(m为存储体个数),

访问m个地址的用时从mT缩短为T+(m-1)r,

访问n个地址用时从nT缩短为 ⌈ \lceil ⌈n/m ⌉ \rceil ⌉*(T+(m-1)r) - ((-n)%m)r,