🔥点击查看精选 CXL 系列文章🔥

🔥点击进入【芯片设计验证】社区,查看更多精彩内容🔥

📢 声明:

- 🥭 作者主页:【MangoPapa的CSDN主页】。

- ⚠️ 本文首发于CSDN,转载或引用请注明出处【https://mangopapa.blog.csdn.net/article/details/131744826】。

- ⚠️ 本文目的为 个人学习记录 及 知识分享。因个人能力受限,存在协议解读不正确的可能。若您参考本文进行产品设计或进行其他事项并造成了不良后果,本人不承担相关法律责任。

- ⚠️ 若本文所采用图片或相关引用侵犯了您的合法权益,请联系我进行删除。

- 😄 欢迎大家指出文章错误,欢迎同行与我交流 ~

- 📧 邮箱:mangopapa@yeah.net

- 💬 直达博主:loveic_lovelife 。(搜索或点击扫码)

文章目录

- 1. CXL ATS 简介

- 2. CXL ATS 的应用范围

- 3. CXL ATS 请求与完成

- 3.1. CXL ATS 请求

- 3.2. CXL ATS 完成

- 4. CXL ATS 流程

- 5. 问题

- 6. 参考

1. CXL ATS 简介

地址转换服务(Address Translation Services,ATS)是 PCIe 的一项 Capability,用以把虚拟地址(Virtual Address,VA)转换为主机物理地址(Host Physical Address,HPA)。之前《PCIe 地址转换服务(ATS)详解》介绍过 ATS 相关内容,今天看 ATS 在 CXL 中应用。

CXL ATS 可概括为两点:

- D2H Req 请求采用 地址路由 且地址采用 HPA,当 HPA 未知时需要采用 CXL.io 的 ATS 做地址转换把 VA 转换为 HPA;

- CXL ATS Req 中的 CXL.Src=1 指示当前为 CXL Device,ATS Cpl 中的 CXL.io=0/1 指示当前页为 Cacheable/Uncacheable,Cacheable 的页支持 CXL.io/cache/mem 访问,Uncacheable 的页仅支持 CXL.io 访问。

接下来做展开介绍——

2. CXL ATS 的应用范围

在 CXL.cache 及 CXL.mem 所有 Channel 中,只有 H2D Req、D2H Req、M2S Req/RwD、S2M BISnp 等访问请求是基于 HPA 地址路由的,Rsp/Data 均采用 ID 路由。对于 H2D Req、M2S Req/RwD 等 Host/Master 主动发起的请求,Host/Master 可以直接在其内部拿到 HPA;对于 S2M BISnp,其采用的 HPA 可以在 Host 访问 HDM-DB 的 M2S Req/RwD 中拿到。真正需要 ATS 来拿 HPA 的,只剩下 D2H Req。

ATS 是 CXL.cache 的必选项,对 CXL.io 和 CXL.mem 则是可选项。对于 Type 1/2 等支持 CXL.cache 的 CXL Device 必须支持 ATS Capability,对于支持 CXL.io+CXL.mem 的 Type 3 Device 则没有强制要求。

D2H Req 可以访问 Host Memory,也可以访问 HDM-D Host Bias 的 Device Memory,这也意味着 ATC 中 Cacheline 所存放的地址映射(VA->HPA)可以为 Host Memory 区域,也可以为 Device Memory 区域。Device 可以直接访问到 HDM-D Device 区域,Device 在访问该区域之前可以通过 ATS 来获取 HPA,也可以通过其他方式来获取。

3. CXL ATS 请求与完成

PCIe ATS 请求、完成、Invalidation 等相关规则在 CXL ATS 中仍然适用,CXL 在 PCIe ATS 基础上做了些增强。

3.1. CXL ATS 请求

ATS Req 包格式如下图所示。有别于 PCIe ATS Req 的是 CXL.Src 字段,该 bit 只对 CXL 系统有效。

CXL.Src 用以指示发起 ATS Req 的 Function 是否支持 CXL.io,为 1 表示支持 CXL.io,为 0 表示不支持 CXL.io。CXL.io 发起 ATS 请求时必须将 ATS Req 中的 CXL.Src 置为 1,表明当前发起请求的 Function 支持 CXL.io,或者说 Function 工作在 CXL Mode 下。

注意

CXL ATS Capability 中 Page Aligned Request 必须置 1,即发出的 ATS 请求为 4KB 边界对齐,不支持地址 bit [11:2]非零的非 4KB 对齐情况。

ATC 是 Host 端 ATPT 的子表,是 Inclusive 的,FLR(Function Level Reset)时 ATC 无需将其 Cacheline 写回。FLR 后,ATC 内所有 Cacheline 均失效,需要重新使能 ATS 并重新获取相关 Cacheline。

3.2. CXL ATS 完成

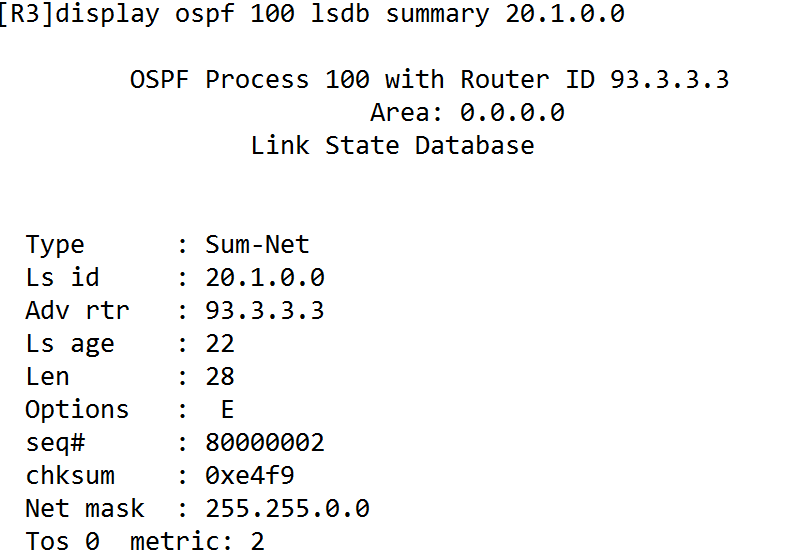

Host 通过 ATS Cpl(Completion)来响应 ATS Req,CXL ATS Cpl 包格式如下图所示。有别于 PCIe ATS Cpl 的是 CXL.io 字段,该 bit 只对 CXL 系统有效。

考虑到并非所有 Memory Region 都支持 Cache 访问,CXL ATS Cpl 采用 CXL.io bit 来指示当前 HPA 所对应的页(Page)是否只能被 CXL.io 访问,为 1 表示 Uncacheable 只能采用 CXL.io 进行访问、不支持通过 CXL.cache/mem 进行访问,为 0 表示 Cacheable 且 CXL.io/cache/mem 均可以访问该页。

4. CXL ATS 流程

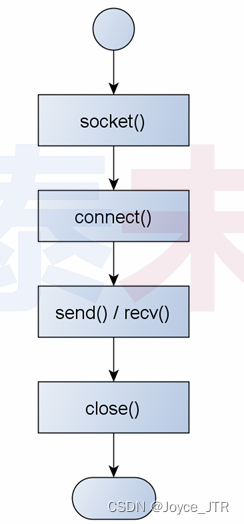

对于支持 CXL.cache 的 CXL Device,当 Device Processor 想要访问主存时,先查找该地址在 Device Cache 内是否存在数据副本。若存在数据副本(Cache Hit),则直接对 Device Cache 中的该 Cacheline 进行读写操作即可;若不存在数据副本(Cache Miss),则需要通过 CXL.cache 去主存存取数据。D2H Cache 请求 Message 中采用的为 HPA,Device Processor 发起请求时采用的为 VA,需要将 VA 转换为 HPA。若 Device ATC 内不存在该 VA->HPA 的转换,需要通过 CXL.io 发起 ATS 请求。

对于支持 ATS、PRS(Page Request Services,页请求服务,详参 PCIe 页请求服务介绍)的 CXL Device,Device Processor 访问 Host VA 的流程如下图所示。

解释如下:

- Processor 发出访问 VA 地址的请求。

- 判断 ATC 中是否存在 VA 对应的 HPA。若存在,直接跳转至 Step 6;若不存在,继续 Step 3。

- Device 通过 CXL.io 发送 ATS 地址转换请求给 Host。

- 判断 ATS 请求是否成功。若成功,跳转至 Step 6;若不成功,继续 Step 5。

- Device 通过 CXL.io 发送页请求服务给 Host,完成后跳至 Step 3。(假设 Device 支持 PRS 且不会失败)

- VA 转换为 HPA。

- 判断 HPA 地址对应的 Memory 是否 Cacheable。若 Non-cacheable,进行 Step 8;若为 Cacheable,进入 Step 9。

- CXL.io 发送 VA 访问请求给 Host,跳至 Step 12。

- 判断 HPA 地址是否在 Device Cache 内存在有效副本。若不存在,继续 Step 10;若不存在,跳至 Step 11。

- CXL.cache 发送地址为 HPA 的 D2H Cache 请求,取回的数据缓存在 Device Cache 中。(假设不会 Cache 请求成功。)

- 从 Device Cache 中取出 HPA 对应的 Cacheline 数据。

- 得到 VA/HPA 地址的数据,结束访问。

5. 问题

-

为什么CXL.mem不需要ATS, CXL.mem用的地址不是HPA吗?

M2S Req/RwD 能直接在 Host 拿到 HPA,S2M BISnp 能从之前的 M2S Req/RwD 中拿到 HPA。

-

Host能给Device发ATS请求吗?Host能看到Device的物理地址吗?

HPA,主机物理地址,Host 没必要到 Host 去取 HPA,Host 能看到统一编址下的 Device Memory 物理地址。

6. 参考

- CXL Base Spec, r3.0

- PCIe Base Spec, r6.0.1

- PCIe地址转换服务(ATS)详解

- PCIe页请求服务(PRS)介绍

|

|

🔥 精选往期 CXL 协议系列文章,请查看【 CXL 专栏】🔥

⬆️ 返回顶部 ⬆️