文章目录

- 前言

- 一、单端走线布线

- 1.1.带有短截线的菊花链布线

- 1.2.没有短截线的菊花链布线

- 1.3.星型布线

- 1.4.蛇型布线

- 二、差分走线布线

前言

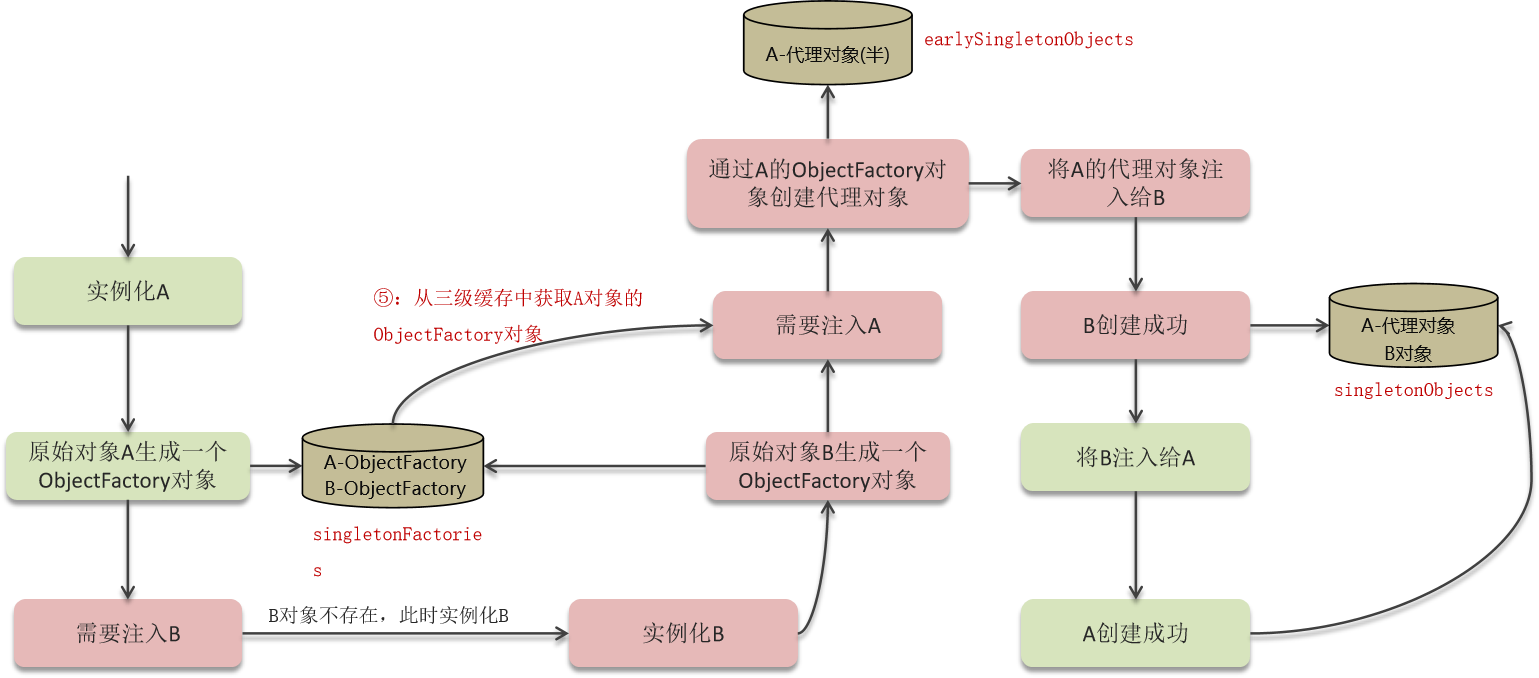

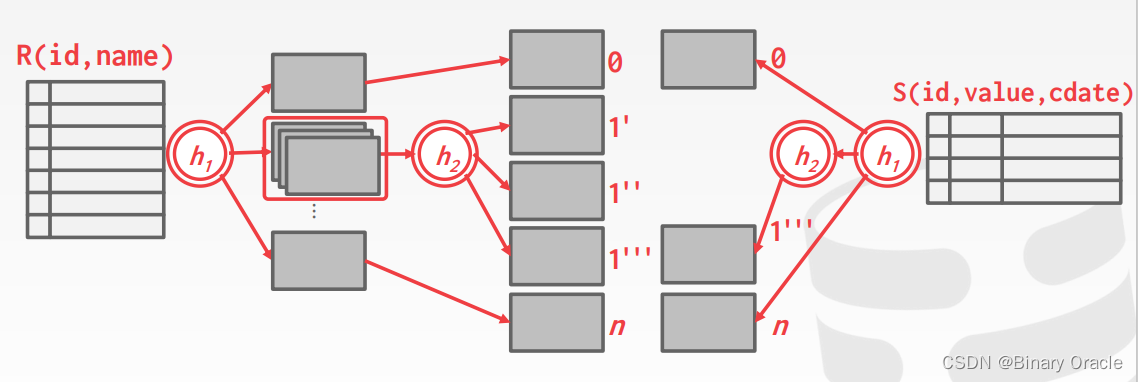

串扰是并行走线间不需要的信号耦合。微带线和带状线正确的布线和叠层布局能够降低串扰。

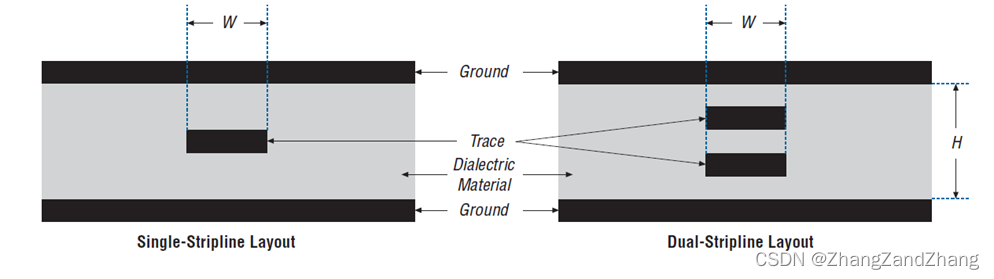

双带线布局有两个靠近的信号层,为降低双带线的串扰,所有走线垂直布设,增大两个信号层之间的距离,减小信号层和邻近参考平面的距离。

使用下面步骤来减小微带线或者带状线布局的串扰:

■ 在布线要求允许范围内,尽可能加宽信号线之间的距离。走线之间尽量不要靠近,距离保持在介质高度三倍以上。

■ 对传输线进行设计,使得导体尽可能靠近地平面。这一方法使传输线能够与地

平面紧耦合,有助于和邻近信号去耦合。

■ 尽可能使用差分布线方法,特别是关键网络(例如,匹配长度,以及每条走线串通回转等)。

■ 如果存在明显的耦合,不同层之间布设互相垂直的单端信号。

■ 减小单端信号之间并行走线长度。以较短的并行走线布线,减小网络之间的长耦合走线。

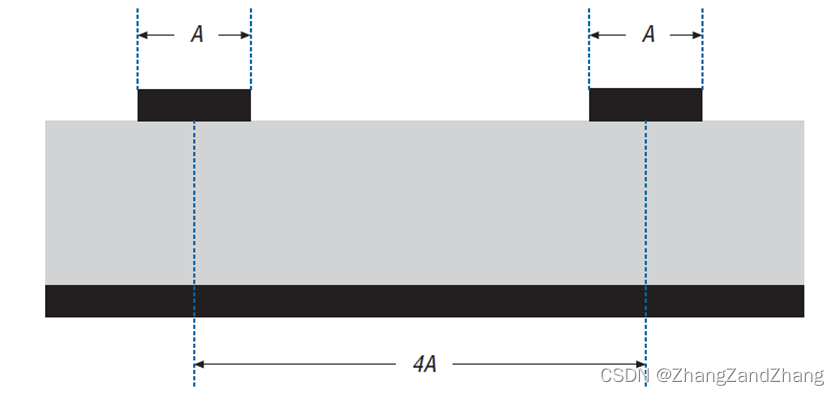

当两条或者多条单端走线并行布设,没有分开足够的距离时,也会有很大的串扰。两条 邻近走线中心之间的距离应至少是走线宽度的四倍,如图所示。为提高设计性能,减小走线和地平面之间的距离,使其小于10mils,不改变两条走线之间的间隔。

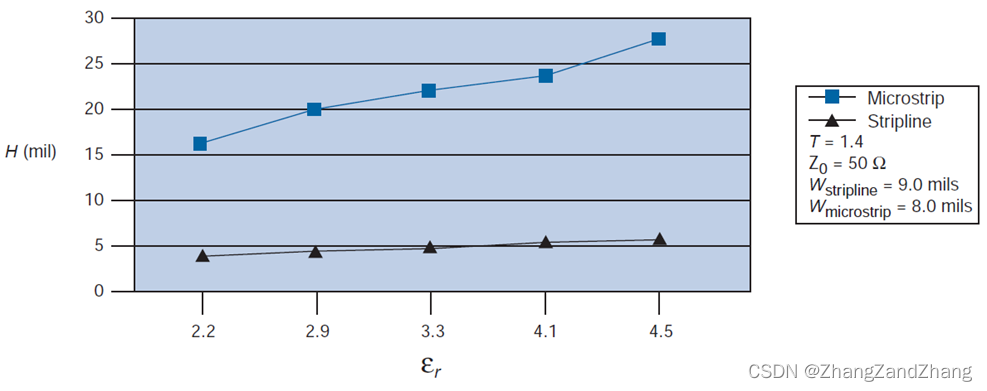

与相对介电常数较大的材料相比,相对介电常数较小的材料有助于减小走线和地平面之 间的厚度,同时保持了信号完整性。图显示了高度与相对介电常数关系,使用了公式,保持阻抗、宽度和厚度不变。

信号走线布线

正确的布线有助于维持信号完整性。为实现干净的布线,您应该采用良好的信号完整性(SI)工具进行仿真。下面介绍了适合布线的两类信号走线:

■ 单端走线

■ 差分对走线

一、单端走线布线

单端走线连接源和负载/接收器。单端走线用于普通点对点布线、时钟布线、低速和不 关键的 I/O 布线。这一部分讨论时钟信号的各种布线方法。您可以使用以下类型的布线 来驱动具有相同时钟的多个器件。

■菊花链布线

– 带有短截线

– 没有短截线

■星型布线

■蛇型布线

使用以下指南来提高时钟传输线的信号完整性:

■ 时钟走线尽可能保持直线。使用弧形走线,而不是直角弯曲。

■ 时钟信号不要使用多个信号层。

■ 在时钟传输线上不要使用过孔。过孔会导致阻抗变化和反射。

■ 靠近外层布设地平面,降低噪声。如果您使用内层进行时钟走线布线,该层应 夹在参考平面之间。

■ 匹配时钟信号以降低反射。

■ 尽可能多的使用点对点时钟走线。

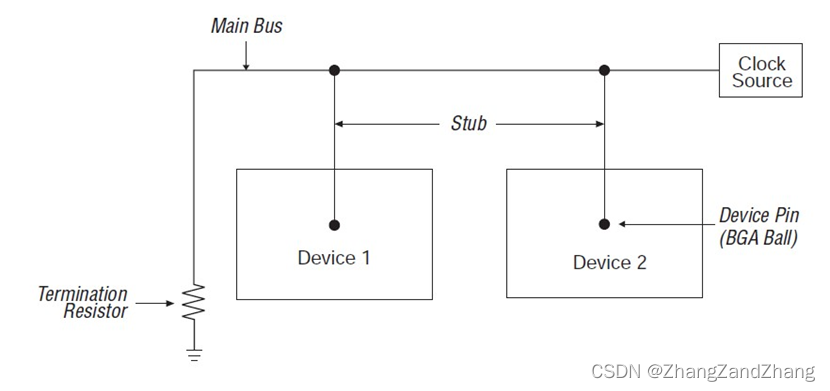

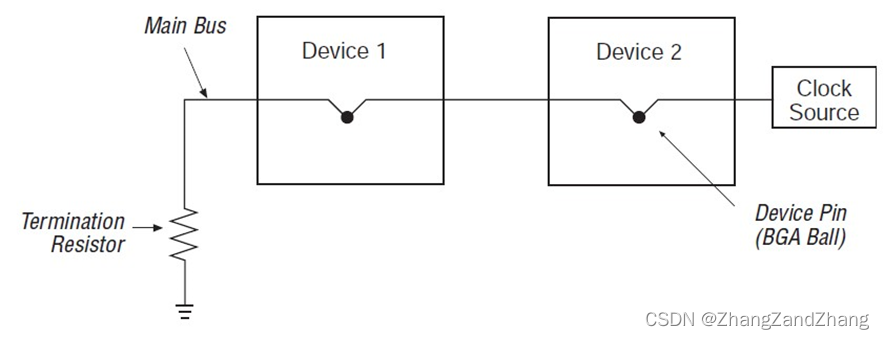

1.1.带有短截线的菊花链布线

菊花链布线是最常见的 PCB 设计。菊花链布线的一个缺点是通常需要短截线,或者短 走线将器件连接至主总线(参见图 14)。如果短截线过长,会导致传输线反射,劣化信号 完整性。因此,短截线长度应满足以下条件:

其中,TDstub = 短截线电延时

T10% to 90% = 信号边沿的上升或者下降时间

对于1-ns的上升边沿,短截线长度应小于 0.5 英寸。如果您的设计使用多个器件,所有短截线长度应相同,以降低时钟偏移。图显示了短截线布线。如果可能,在PCB设计中,您应该避免使用短截线。对于高速设计,即使非常短的短截线也会带来信号完整性问题。

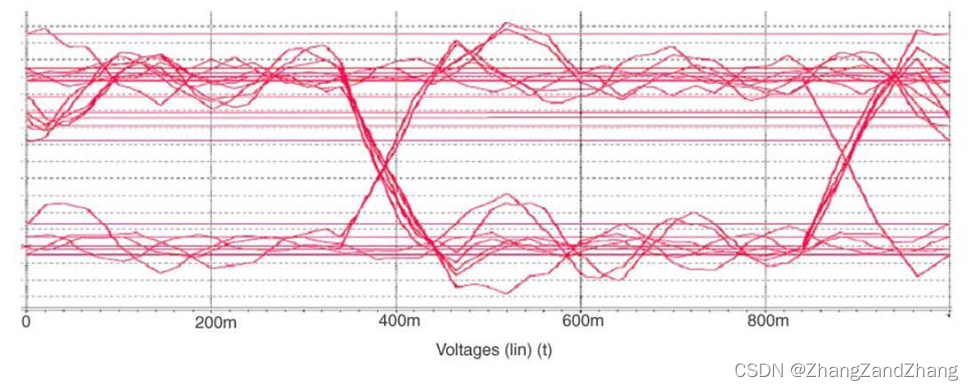

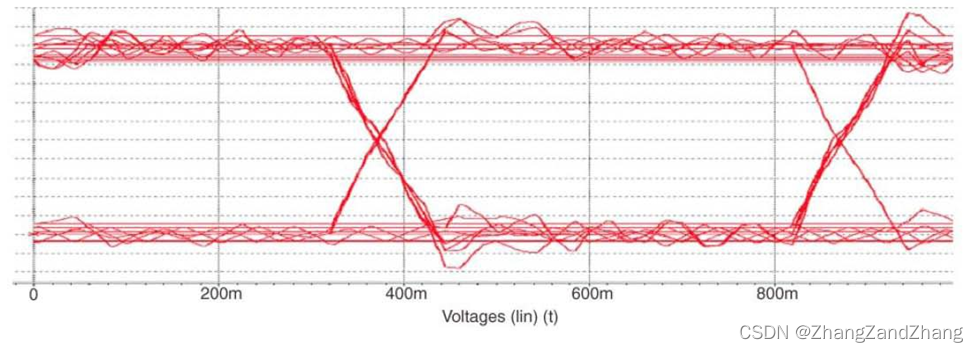

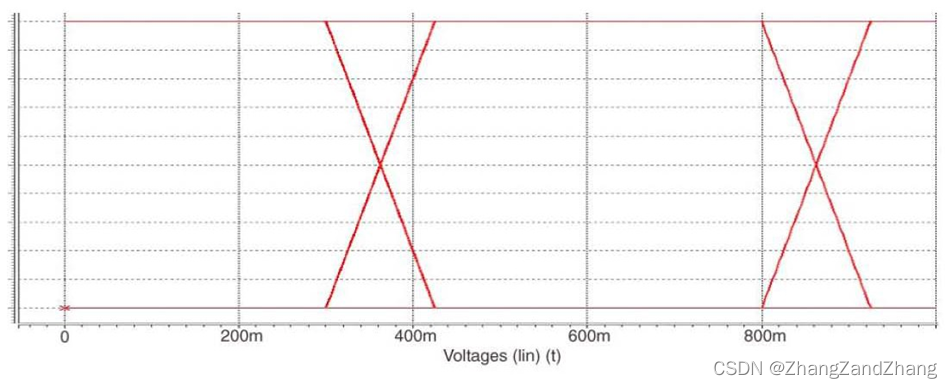

图显示了短截线不同长度时的 SPICE 仿真。随着短截线长度的减小,反射噪 声随之降低,因此,眼图进一步张开。

短截线长度 = 0.5 英寸

短截线长度 = 0.25 英寸

短截线长度 = 0 英寸

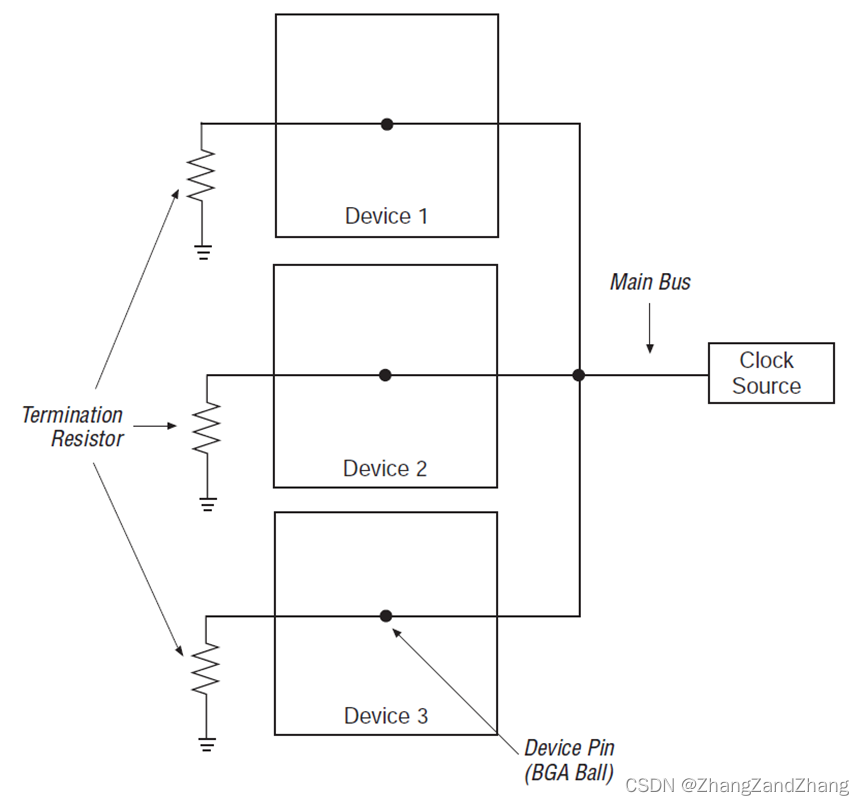

1.2.没有短截线的菊花链布线

图中菊花链布线的主总线通过器件引脚,避免了短截线。这种布局降低了主总线和 短截线之间的阻抗不匹配风险,避免了信号完整性问题。

1.3.星型布线

在星型布线中,时钟信号同时连接至所有器件。因此,时钟源和器件之间的 所有走线长度都应匹配,以降低时钟偏移。每一负载应相同,从而减小信号完整性问题。 在星型布线中,主总线阻抗和连接多个器件的长走线阻抗必须匹配。

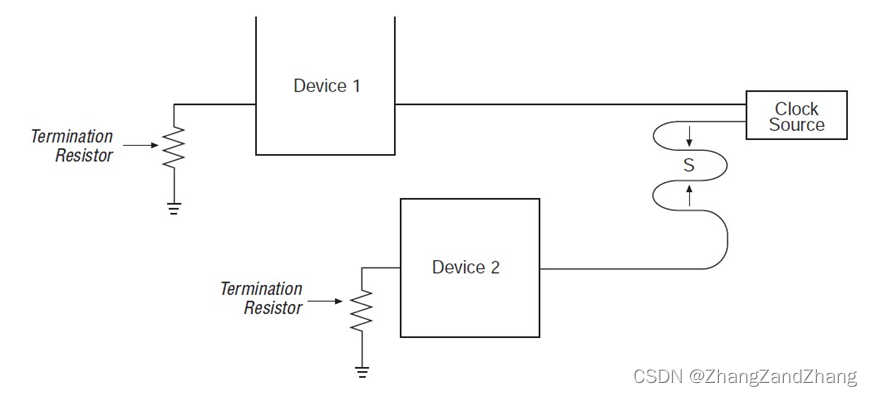

1.4.蛇型布线

当设计的源和多个负载之间需要等长走线时,您可以弯曲一些走线来匹配走线长度。不合适的走线弯曲会影响信号完整性和传播延时。为降低串扰,应确保S≥3×H,其中,S是并行部分之间的间距,H是参考地平面之上信号走线的高度。请参考图。

建议尽可能避免使用蛇行布线。相反,应使用弧形来建立等长走线。

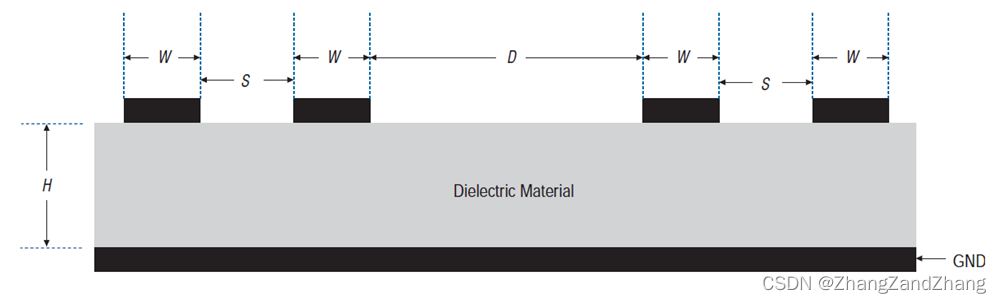

二、差分走线布线

为提高信号完整性,采用正确的差分信号布线方法对于高速设计非常重要。图 21 显示 了使用微带线布局的差分对。

注释:

(1) D = 两个差分对信号之间的距离;W = 差分对走线宽度;S = 差分对走线之间 的距离;H = 地平面之上的介质高度。

使用两个差分对时,请参考下面的指南:

■确定 D > 2S,以减小两个差分对之间的串扰。

■为减小反射噪声,差分走线离开器件时,使差分走线 S = 3H。

■在整条走线上,保持差分走线之间的距离(S)不变。

■保持两条差分走线的长度相同,以降低偏移和相差。

■避免使用多个过孔,这些过孔会导致阻抗不匹配和电感。