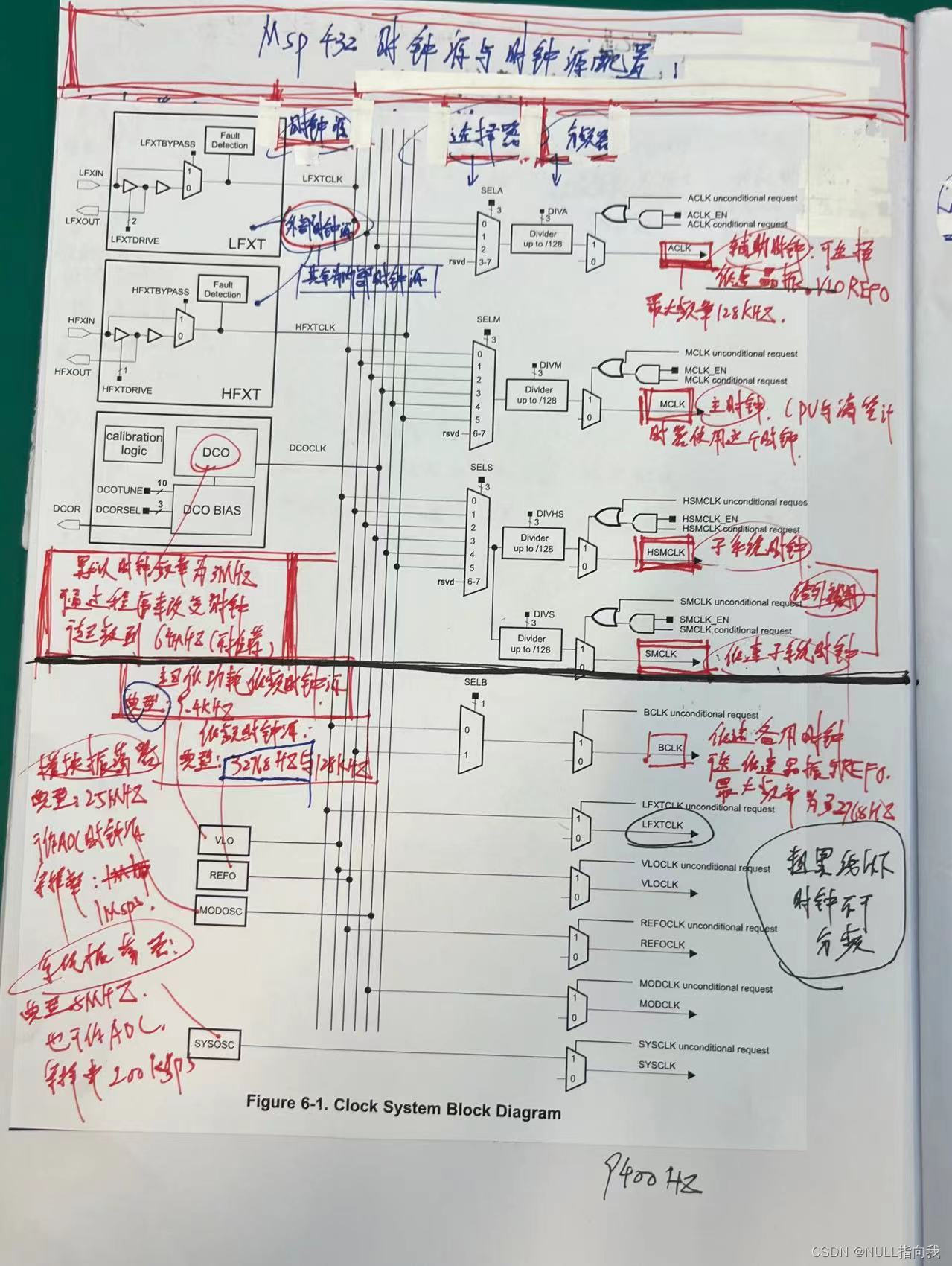

今日深入学习一下MSP432的时钟源与配置,

可以结合之前的滴答计时器相关文章:

MSP432学习笔记4:时钟与滴答计时器_NULL指向我的博客-CSDN博客

目录

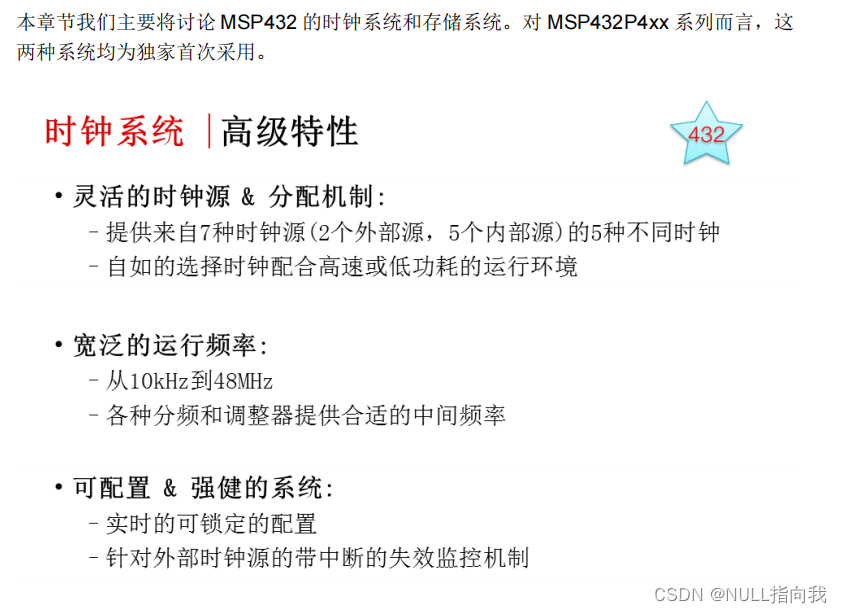

MSP432有关时钟源系统的性能:

七种时钟源:

五种时钟:

主函数时钟源初始化:

定时器A初始化选择时钟源:

ACLK的时钟源频率默认是REFO超低功耗的32768Hz频率:

实验验证:

下回预告:

杂毛笔记记录:

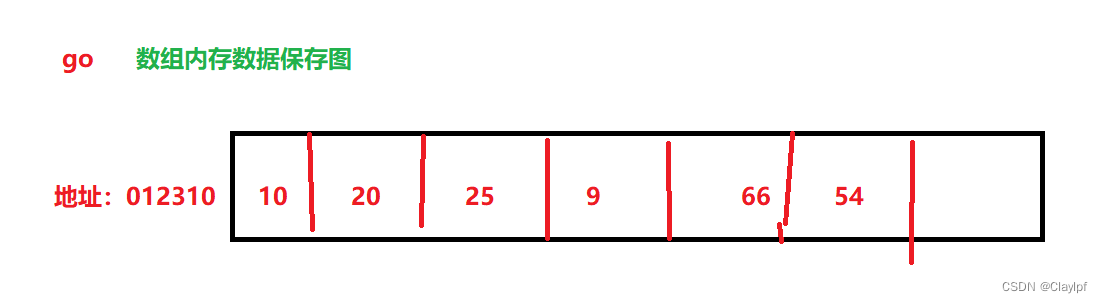

MSP432有关时钟源系统的性能:

首先看到商家产品训练手册的吹股环节:

整个时钟系统可分为两个部分:一个部分适用于高速和高性能的操作,另一个部分则专门 针对超低功耗应用进行了优化。如此一来,通过组合,这两组时钟便可涵盖从 10KHz 直 至 48MHz 的较大工作频率范围,和各种应用场合。

七种时钟源:

MSP432P4xx 系列共计提供了七种时钟源:DCO 是高频的数控振荡器。这是一种最为常用的高频内部时钟源,它可在任意环境下生成 1 到 48 MHz 的高频率时钟。HFXT 是通过外接高频晶体实现的高频时钟源,同样可以实现 1 到 48 MHz 的任意高频率时钟源。MODOSC 是一种可运行于 24MHz 的内部振荡器。 MODOSC 适用于内部模拟模块(仅 ADC 或闪存),特别面向于需要 24MHz 时钟源方可运行的 1MHz ADC 。SYSOSC 是内部的低频率振荡器,运行于 5MHz ,对于一些较低频率的操作和应用,可使用 SYSOSC 。LFXT 是通过外接低频晶体实现的低频时钟,此类晶体为典型 32KHz 晶体。它可用于运行精确的 RTC 时钟。REFO 是低频的内部振荡器,可生成 128KHz 的时钟信号,同时它还可被分频为32KHz 用于 RTC 。最后则是超低频振荡器 VLO ,它是另一种可生成 10KHz 时钟信号的内部振荡器。

DCO数控时钟源,默认频率为3MHz,可通过程序改变频率,使用内部电阻时精度不高,

可外接精密电阻使用,通过DCO可以时钟超频至64MHz。(超频有风险,试玩需谨慎)

VLO超低功耗低频时钟源,典型频率为9.4KHz。

REFO低频时钟源,典型频率为32768Hz和128KHz。

MODOSC模块振荡器,典型频率为25MHz。可做ADC时钟源,采样频率1M。

SYSOSC系统震荡器,典型频率为5MHz。可做ADC时钟源,采样频率200K。

五种时钟:

MCLK ,它是用于驱动 CPU 以及潜在 DMA 运算的主时钟。SMCLK 和 高速 SMCLK(也称为 HSMCLK) 。这两种时钟可用于驱动不同外设,例如ADC 、高速计时器和通信模块。ACLK 和 BCLK 是专为超低功耗模式而优化的低频时钟,适用于低频和低功耗模式。需特别提出的是, ACLK 和 BCLK 均可在从 128KHz 到 10KHz 范围内的任意环境下运 行。

主函数时钟源初始化:

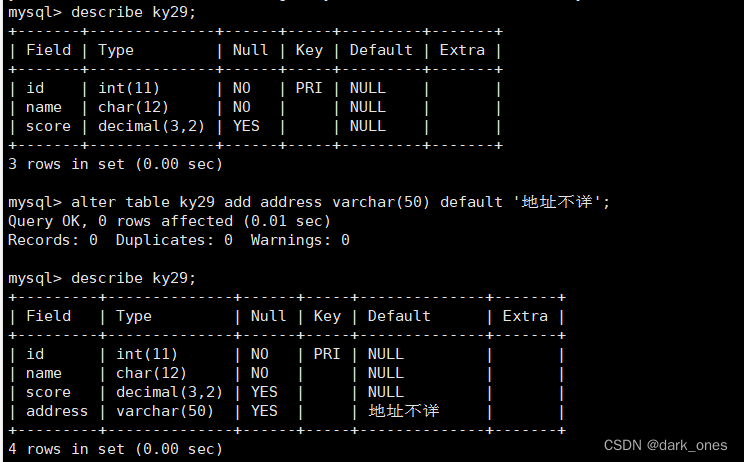

以下为空项目工程对时钟的配置情况:

外部高速晶振、MCLK、SMCLK都被配置为48MHz

外部低速晶振配置为 32768Hz

#include "sysinit.h"

//外部时钟 High:48MHz Low:32768Hz

// MCLK=48MHz SMCLK=48MHz

void SysInit(void)

{

WDTCTL = WDTPW | WDTHOLD; // 停用看门狗

/* 第一步需要配置我们的时钟引脚,这里的高速时钟使用的是外部晶振*/

//低速时钟初始化比较慢

MAP_GPIO_setAsPeripheralModuleFunctionOutputPin(GPIO_PORT_PJ, GPIO_PIN3 | GPIO_PIN2, GPIO_PRIMARY_MODULE_FUNCTION); //High

MAP_GPIO_setAsPeripheralModuleFunctionOutputPin(GPIO_PORT_PJ, GPIO_PIN0 | GPIO_PIN1, GPIO_PRIMARY_MODULE_FUNCTION); //Low

CS_setExternalClockSourceFrequency(32768, 48000000);

/* Starting HFXT in non-bypass mode without a timeout. Before we start

* we have to change VCORE to 1 to support the 48MHz frequency */

MAP_PCM_setCoreVoltageLevel(PCM_VCORE1);

/* 更改闪存控制器使用的等待状态数用于读取操作。

当改变时钟的频率范围时,必须使用此函数以允许可读闪存

通俗来讲就是CPU跑太快了,Flash跟不上,让CPU等等它 */

MAP_FlashCtl_setWaitState(FLASH_BANK0, 1);

MAP_FlashCtl_setWaitState(FLASH_BANK1, 1);

CS_startHFXT(false); //这是晶体 需要驱动

CS_startLFXT(CS_LFXT_DRIVE3); //驱动等级3

MAP_CS_initClockSignal(CS_MCLK, CS_HFXTCLK_SELECT, CS_CLOCK_DIVIDER_1); //48MHz 16分频时,滴答延时可达到最长

MAP_CS_initClockSignal(CS_SMCLK, CS_HFXTCLK_SELECT, CS_CLOCK_DIVIDER_1); //48MHz

}

/*

这个函数是针对MSP432微控制器的系统初始化函数。下面是对函数每个步骤的详细解释:

1. 停用看门狗:

通过将WDTCTL寄存器设置为WDTPW | WDTHOLD,将看门狗定时器停用。

2. 配置时钟引脚:

使用GPIO端口 PJ(引脚 2、3和0、1)将引脚配置为带有主要模块功能的外设输出引脚。在这里,引脚2和3用作高速时钟引脚,引脚0和1用作低速时钟引脚。

3. 设置外部晶振频率:

使用CS_setExternalClockSourceFrequency函数设置外部晶振的频率。在这里,外部晶振的频率被设置为32768Hz,并且主时钟被设置为48000000Hz。

4. 启动48MHz高速外部晶振(HFXT):

在非旁路模式下启动HFXT,并设置VCORE电压级别为1以支持48MHz频率。

5. 设置闪存控制器的等待状态:

使用FlashCtl_setWaitState函数设置引导加载程序等待状态,以满足增加时钟频率的要求。在这里,设置FLASH_BANK0和FLASH_BANK1的等待状态为1。

6. 启动低速外部晶振(LFXT):

使用CS_startLFXT函数启动LFXT,并设置驱动等级为3。

7. 初始化主时钟(MCLK)和子系统时钟(SMCLK):

使用CS_initClockSignal函数将MCLK和SMCLK时钟源设置为HFXTCLK,并设置时钟分频器为1,从而将主时钟和子系统时钟设置为48MHz。

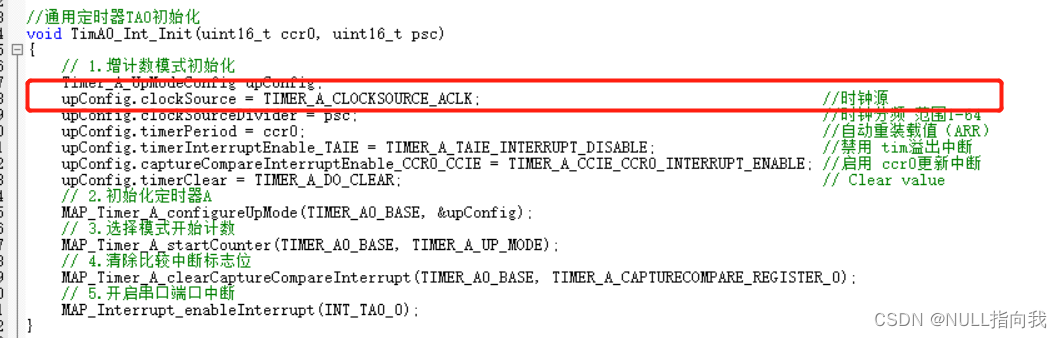

*/定时器A初始化选择时钟源:

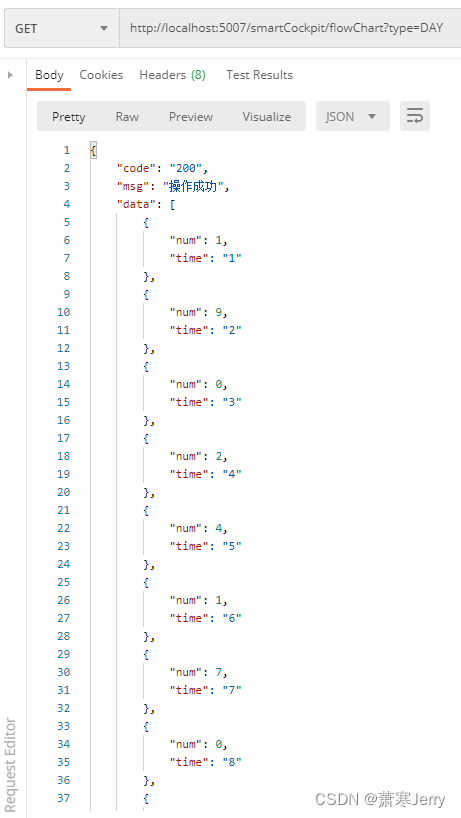

在主时钟配置结束后,例如定时器A的初始化,一般也会要求我们选择时钟,

定时器A有四种时钟可以选择,不同频率任务的定时器选择的时钟源也应该不同:

//*****************************************************************************

//

// The following are values that can be passed to the clockSource parameter

//

//*****************************************************************************

#define TIMER_A_CLOCKSOURCE_EXTERNAL_TXCLK TIMER_A_CTL_SSEL__TACLK

#define TIMER_A_CLOCKSOURCE_ACLK TIMER_A_CTL_SSEL__ACLK

#define TIMER_A_CLOCKSOURCE_SMCLK TIMER_A_CTL_SSEL__SMCLK

#define TIMER_A_CLOCKSOURCE_INVERTED_EXTERNAL_TXCLK TIMER_A_CTL_SSEL__INCLK

根据MSP432上的默认时钟频率设置,这些地址表示的时钟源的频率如下:

TIMER_A_CLOCKSOURCE_EXTERNAL_TXCLK:

外部时钟(TXCLK)的频率。

TIMER_A_CLOCKSOURCE_ACLK:

ACLK(Auxiliary Clock)的频率。

TIMER_A_CLOCKSOURCE_SMCLK:

SMCLK(Sub-main Clock)的频率。

TIMER_A_CLOCKSOURCE_INVERTED_EXTERNAL_TXCLK:

反转后的外部时钟(TXCLK)的频率。

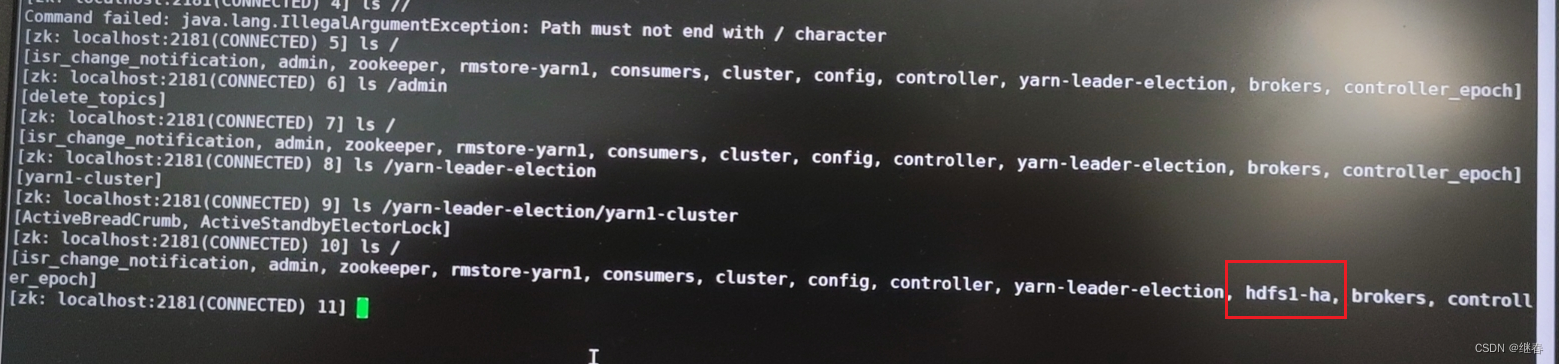

ACLK的时钟源频率默认是REFO超低功耗的32768Hz频率:

MSP432微控制器的ACLK默认时钟源是内部低功耗晶振(LFXT1CLK)。

如果不进行ACLK的时钟源配置,MSP432会默认使用LFXT1CLK作为ACLK的时钟源。这个时钟源可以在外部连接一个低功耗晶振(通常是32.768kHz的晶振),也可以使用MSP432内部提供的内部晶振。

注意,如果需要正确配置ACLK的时钟源,需要使用相应的时钟初始化函数进行配置,例如`CS_initClockSignal()`函数。

经过对时钟框图的研究,发现ACLK的时钟源频率默认是REFO超低功耗的32768Hz频率:

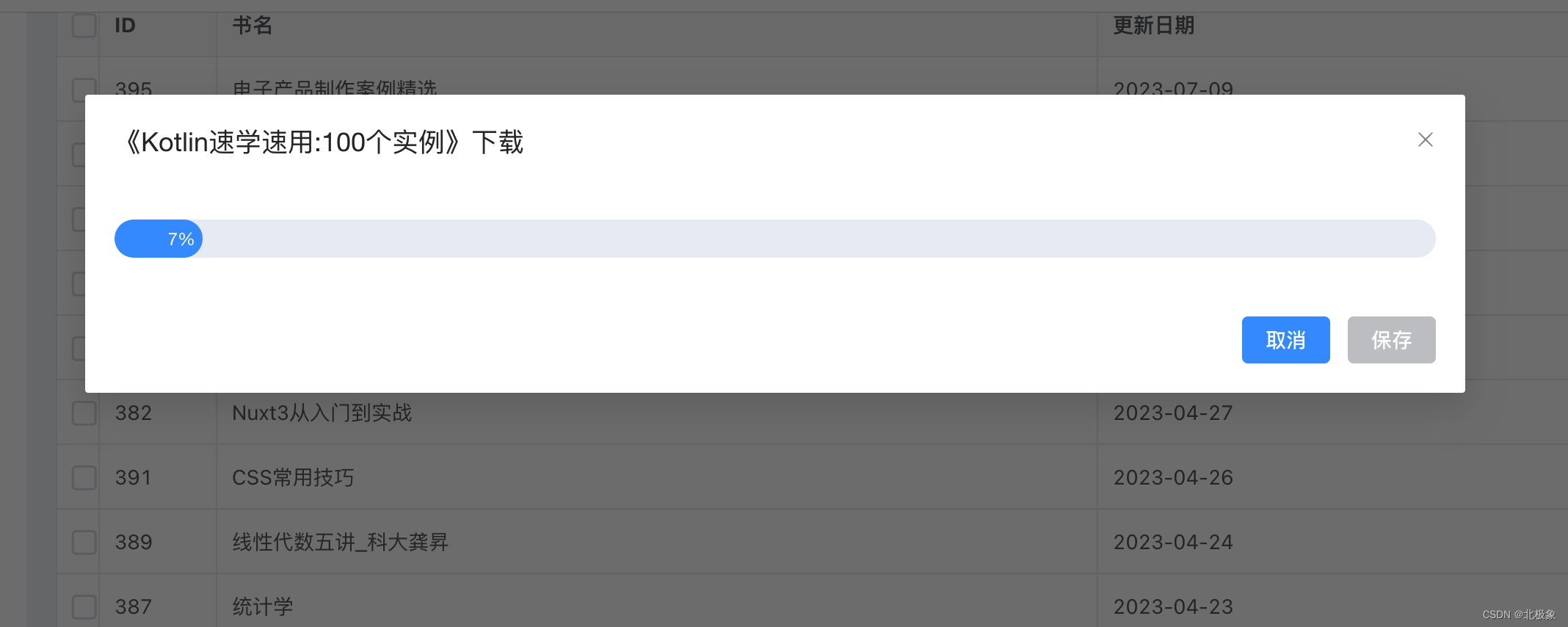

实验验证:

此部分仅为个人验证过程,就不贴出代码了!

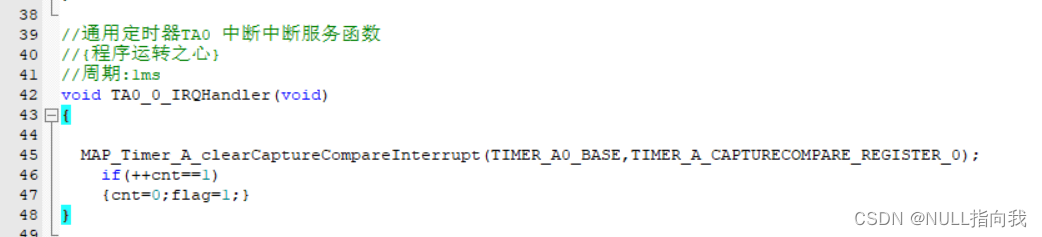

定时器中断控制串口每隔一秒发送测试字符串

定时器配置:

主函数相应标志:

测试结果:

下回预告:

定时器A的这俩默认时钟源配置将在下节文章做研究

杂毛笔记记录: