1 接口信号与控制寄存器

- EMIF(External Memory Interface)外部存储器接口

- 为DSP芯片与众多外部设备之间提供一种连接方式,EMIF最常见的用途就是同时连接FLASH和SDRAM。

- EMIF性能优良,跟外部SDRAM和异步器件连接时,具有很大的方便性和灵活性。

- 根据DSP器件的不同,EMIF数据总线可以是32位、16位或8位。

1. 1EMIF接口信号

主要特点是:

- 系统需要为C67x提供一个外部时钟。该外部时钟由ECLKIN输入后会产生EMIF接口的时钟信号ECLKOUT。

- SBSRAM接口、SDRAM接口和异步接口的信号合并复用。由于不需要进行后台刷新,系统中允许同时具有这3种类型的存储器。

- CE1空间支持所有的3种存储器接口。

- 同步存储器接口提供4 字突发访问模式。

- SDRAM接口更灵活,支持更广泛的SDRAM配置。

2. EMIF接口地址

虽然C6000提供32位地址寻址能力,但是经EMIF直接输出的地址信号只有EA[21:2]。一般情况下,EA2信号对应逻辑地址A2,但这并不意味着DSP访问外存时只能进行字(32 bit)或双字(64 bit)的存取。实际上内部32位地址的最低2~3位经译码后由BEx输出,是能够控制字节访问的。某些情况下,EA2还可能对应最低位逻辑地址A1或A0

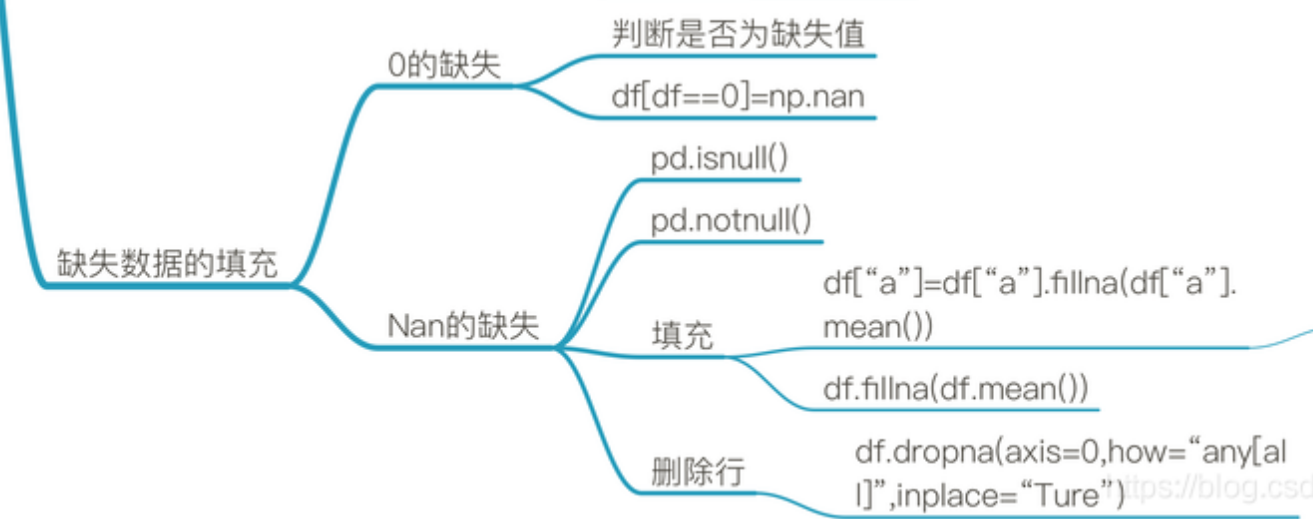

3. EMIF控制寄存器

- EMIF接口由一组存储器映射的寄存器进行控制与维护,包括配置各个空间的存储器类型和设置读写时序等。

- GBLCTL寄存器完成对整个片外存储空间的公共参数的设置,CExCTL寄存器分别控制相应存储空间的存储器类型和接口时序,另外3个SDRAM寄存器负责控制所有属于SDRAM空间的存储接口情况

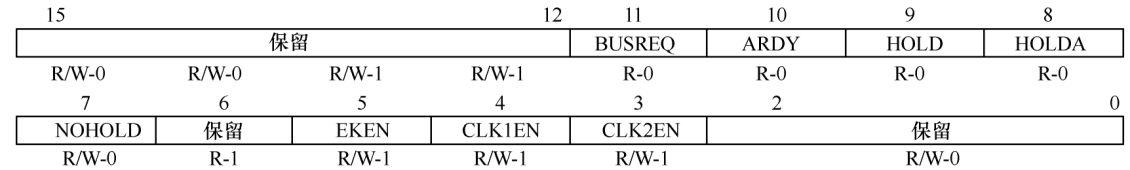

GBLCTL寄存器

CExCTL寄存器

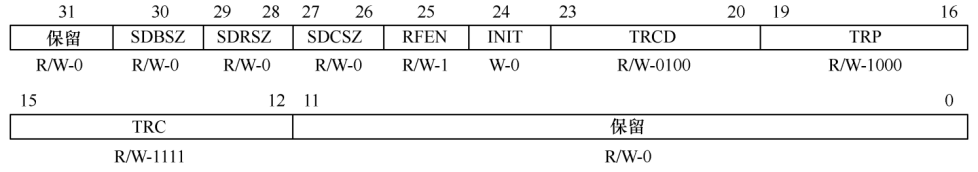

SDCTL寄存器

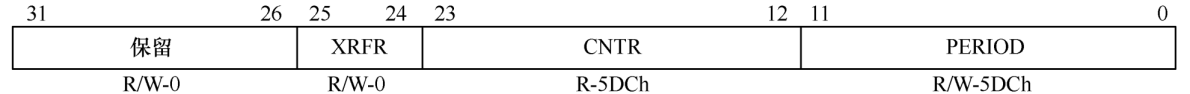

SDTIM寄存器

SDEXT寄存器

2、SDRAM同步接口设计

- SRAM是Static Random Access Memory的缩写,中文含义为静态随机访问存储器,它是一种类型的半导体存储器。“静态”是指只要不掉电,存储在SRAM中的数据就不会丢失。这一点与DRAM不同,DRAM需要进行周期性的刷新操作。 同时,我们不应将SRAM与只读存储器(ROM)和Flash Memory相混淆,因为SRAM是一种易失性存储器,它只有在电源保持连续供应的情况下才能够保持数据。“随机访问”是指存储器的内容可以任意顺序访问,而不管前一次访问的是哪一个位置。

- DRAM是Dynamic

RAM的缩写,中文含义为动态随机存取存储器,需要不断的刷新,才能保存数据。而且是行列地址复用的,许多都有页模式。SDRAM:Synchronous

DRAM,即数据的读写需要时钟来同步。 DDR(Double Data Rate)

SDRAM:双倍速率同步动态随机存储器,一个时钟周期内传输两次数据。 - 一个是静态的,一个是动态的,静态的是用的双稳态触发器来保存信息,而动态的是用电子,要不时的刷新来保持。

- DRAM容量大,速度快;SRAM容量小,速度慢。

2.1、SDRAM的结构

2.2、 SDRAM的控制

EMIF所支持的SDRAM控制命令

ACTV命令

ACTV命令的作用是激活存储器中的相关页,以尽量降低后续访问的延迟。每次读/写SDRAM中新的一行之前,EMIF会自动发出ACTV命令。

READ 读命令

对SDRAM的突发访问,读取3个数据

WRT 写命令

对SDRAM写3个数据

3. 接口时序的设计

EMIF与SDRAM的接口时序由SDCTL、SDTIM和SDEXT寄存器控制,如何设置上述时间参数,需要用户去查看具体SDRAM芯片的器件手册

接口时序的设计

4. SDRAM读写示例

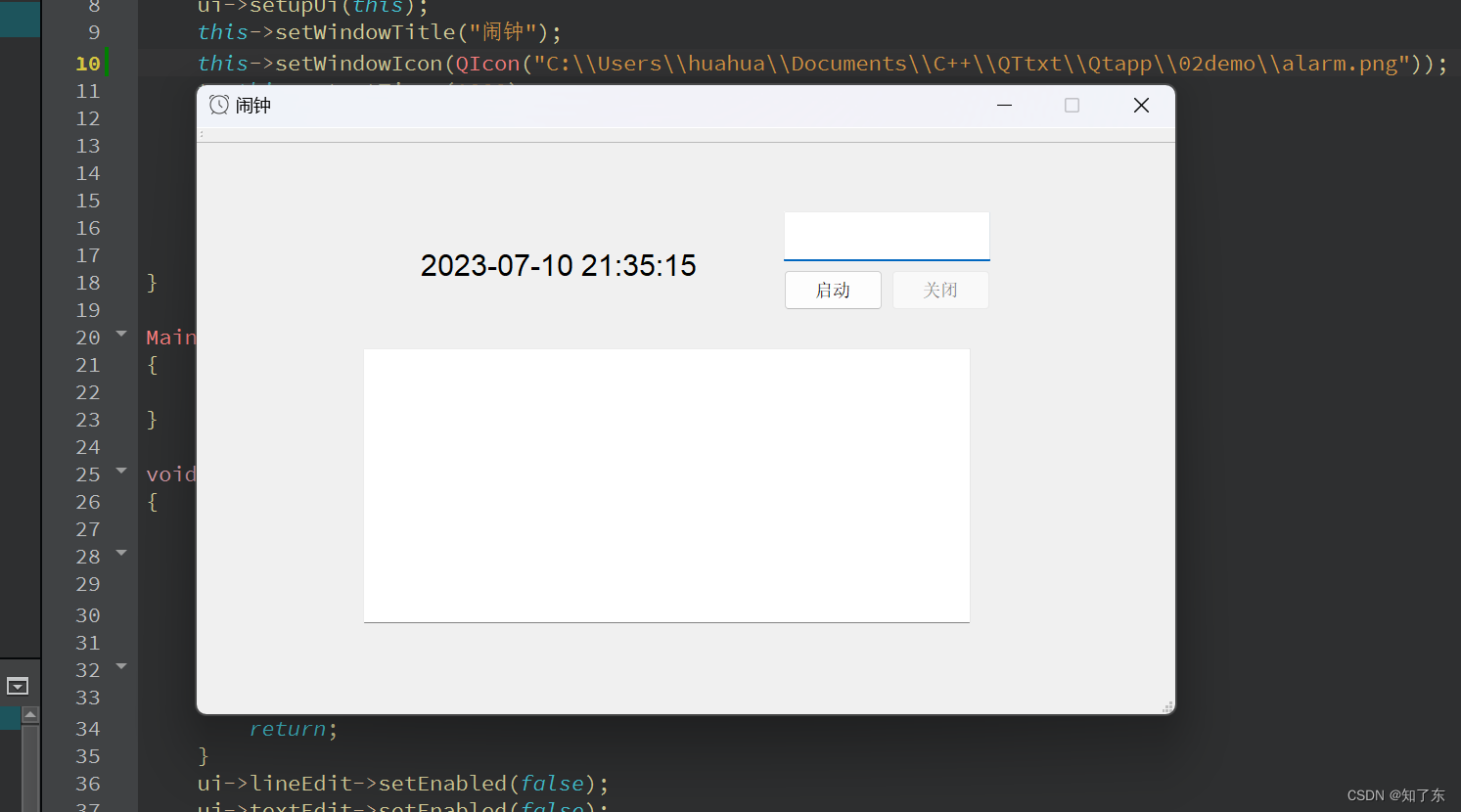

程序类型:

汇编程序

直接寄存器操作的C语言程序

基于CSL的C语言程序

基于DSP/BIOS的C语言程序

5、异步接口设计

EMIF异步接口提供了4个控制信号,这4个控制信号可以通过不同的组合实现与不同类型异步器件的无缝接口(glueless interface)。

EMIF 异步读时序

- 建立时间:从存储器访问周期开始(片选、地址有效)到读/写选通有效之前

- 触发时间:读/写选通信号从有效到无效

- 保持时间:从读/写信号无效到该访问周期结束

EMIF 异步写时序

EMIF 异步读时序

表中RS为读建立时间,RST为读触发时间,RH为读保持时间,WS为写建立时间,WST为写触发时间,WH为写保持时间,E为ECLKOUT周期

CE1CTL控制寄存器

FLASH 的读时序

FLASH 的读时序

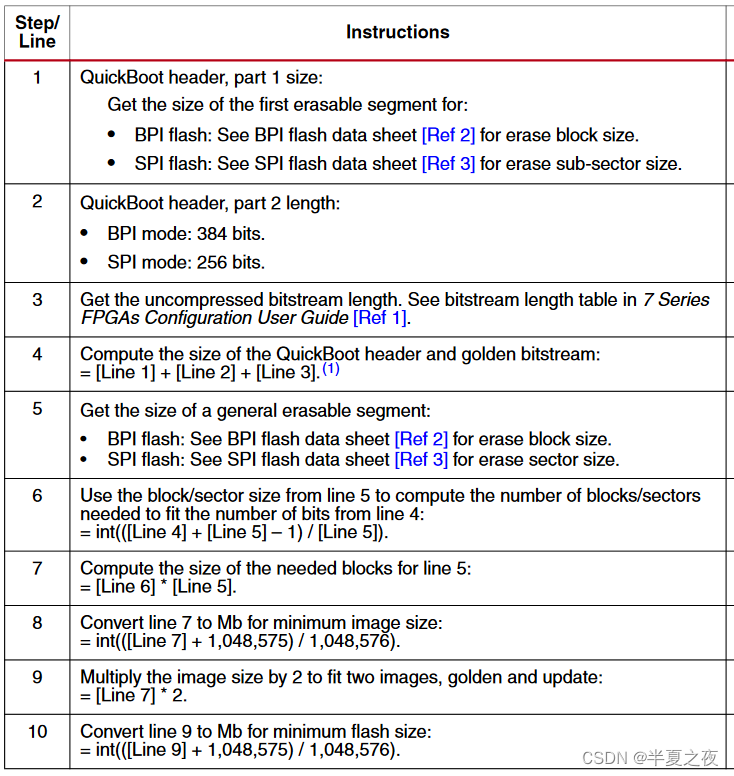

数据是在Strobe阶段结束,ARE信号变高之前的时钟上升沿处被DSP读取,因此可以得出读操作中CE1空间控制寄存器有关参数设定的3个限制条件,设EMIF时钟频率为100MHz,得时钟周期E为10ns,则计算如下:

- Setup+Strobe≥(tacc(f)+tsu+tdmax)/E=(90+6.5+7)/10=10.3

- Setup+Strobe+Hold≥trc(f)/E=90/10=9

- Hold≥(th-toh(f))/E=(1-0)/10=0.1

一般Setup可取1,这样由第1个条件便可以得出Strobe的值为10;再由第2和第3个条件得到Hold的值为1。

FLASH 的写时序

对于写操作,Setup、Strobe和Hold这3个参数可以依照下面的条件来确定:

- Strobe≥twp(f)/E=35/10=3.5

- Setup+Strobe≥twph(f)/E=30/10=3

- Setup+Strobe+Hold≥twc(f)/E=90/10=9

- Setup值和Hold值均取1,则Strobe的值为7

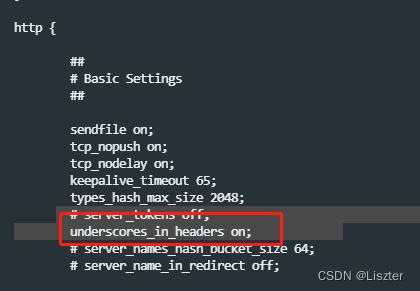

因此得到CE1CTL控制寄存器各字段的值,MTYPE设为2对应32位异步接口。

- RDSETUP = 1 WRSETUP = 1

- RDSTRB = 10 WRSTRB = 7

- RDHLD = 1 WRHLD = 1

Flash 编程命令字及顺序

FLASH 读写流程

FLASH擦除流程

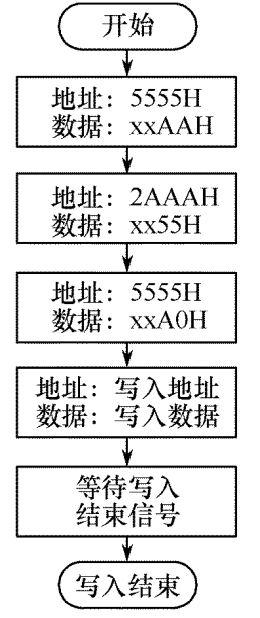

FLASH写入流程

FLASH 操作等待流程

FLASH芯片提供了2种方法来检测是否完成擦除和写数据等编程操作:数据轮询位(DQ7)和数据切换位(DQ6)。当芯片处于内部编程操作时,读DQ7会返回’0’,读DQ6的返回值在’0’和’1’之间切换;当内部编程操作完成后,读DQ7就会返回’1’,DQ6停止切换。因此需要在编程操作的程序中插入2次读操作,如果2次读的结果都是有效数据,才说明器件完成了编程操作。

Flash 读写示例程序

FLASH映射到CE1存储空间,地址范围0x9000 0000~0x9FFF FFFF。选择16位数据总线时, Flash的BYTE输入端被固定为高电平。在这个例子中,Flash的RY/BY端口的输出信号没有被用来决定Flash的状态,而是假定采用轮询法对Flash编程和擦除。

FLASH 读写流程