目录

一、容抗/感抗

1.容抗

2.感抗

二、寄生电容/分布电容/杂散电容

1.寄生电容

2.分布电容

3.杂散电容

4.寄生电容/分布电容/杂散电容对信号的影响

5.怎么减小分布电容?

三.寄生电感

1.什么是寄生电感?

2.怎么减小寄生电感?

四.EMI/EMC

1.什么是EMI/EMC

2.怎么减小EMI?

五.信号串扰

1.信号串扰

2.怎么减小信号串扰?

六.高速信号线

七.高速差分对

八.去耦/旁路/滤波/耦合电容

1.去耦电容

2.旁路电容

3.滤波电容

4.耦合电容

5.直流偏移对音频设备的危害

6.去耦/旁路/滤波电容为什么要靠近作用端?

7.去耦半径计算

8.不同规格电容的摆放顺序

九.阻抗匹配

1.什么是阻抗匹配?

2.PCB走线的阻抗怎么算?

3.怎么做阻抗匹配?

一、容抗/感抗

容抗和感抗都叫阻抗,表现为对电流的阻碍作用,但并不消耗能量。高速PCB设计基本上就是在跟容抗和感抗斗争,所以布局走线的时候,要时刻注意尽量减少不必要的电容和电感效应。

1.容抗

电容是储能元件,可以容纳一定的电能,当电容电压比输入电压小的时候,电容充电;当电容电压等于输入电压的时候,电容停止充电;当电容电压小于输入电压的时候,电容放电。

如果是直流电,电容存在充电电流,充电满了之后,电流消失,表现为开路。如果是交流电,电容存在充电和放电电流,方向相反,交流电流通过电容。交流电虽然可以通过电容,但是电容对交流电也有一定阻碍作用,比如电容充满了,交流电还没有换向,那么就不再能通过电容,直到交流电换向,电容放电,所以会有容抗一说,容抗的公式为:X=1/(2πfC),X是容抗,f是交流电频率(单位Hz),C是电容容值(单位F)由公式可以看出频率越高,容抗越小,容值越大,容抗越小。

总结一下,电容对电流的作用就是,隔直通交,低频小容容抗高。

2.感抗

根据电磁相互作用,当恒定的电流通过线圈的时候会产生恒定的磁场,当交变的电流流过线圈的时候,会产生交变的磁场,而交变的磁场又会产生交变的电场,交变的电场会产生交变电流,根据右手螺旋法则,产生的交变电流跟原电流方向相反,所以对原电流有阻碍作用。

这样可能比较难理解,可以理解电感的作用就是会延迟原有电流大小方向的变化,但交流电反向后,电感的延迟作用导致原方向还有电流,就导致了两个电流方向相反。而直流不会反向,所以对直流电没有阻碍作用。电感对交流电的阻碍叫做感抗,感抗公式:X=2πfL,f是交流电频率(单位Hz),L是电感值单位(H)。由公式可以看出,频率越大感抗越大,电感值越大感抗越大。这点跟电容刚好相反。

总结一下,电感对电流的作用就是,通直阻交,低频小感感抗小。

二、寄生电容/分布电容/杂散电容

1.寄生电容

工艺问题导致元器件内部存在的电容。

2.分布电容

两个元器件之间,或者两根平行走线之间存在的电容。

3.杂散电容

除寄生电容和分布电容之外的,两个元器件或元器件与导体之间形成的电容。

为了简单,也有将三种形式电容混为一谈的说法。

4.寄生电容/分布电容/杂散电容对信号的影响

电容是隔直通交,阻低通高的,如果两条信号线之间形成了分布电容,高频信号就会跑到相邻的信号线中去,而不会传递到接收端,这样不仅接收端的高频信号会被截流,而且相邻的信号线上的信号也会失真。信号频率一定的情况下,分布电容越小,容抗越大,影响也就越小。所以要减小分布电容。

5.怎么减小分布电容?

原则就是减小两线的有效电容面积,增大两线距离。

(1).避免平行布线

(2).走线尽可能窄

(3).走线尽可能短

(4).走线间距尽可能大

(5).走线之间隔地线

三.寄生电感

1.什么是寄生电感?

PCB走线本身存在的电感。

寄生电感对信号的影响

电感的特性是低通高阻,所以信号的高频部分很难通过,导致高频信号丢失。此外,相邻的信号线间产生电磁相互作用,也叫感性耦合(类似于变压器),也会影响到相邻信号线。

2.怎么减小寄生电感?

(1)走线尽可能端

(2)避免走线形成环路

四.EMI/EMC

1.什么是EMI/EMC

EMI电磁干扰,设备内器件或设备间相互的电磁干扰。

EMC电磁兼容性,设备可以抵抗干扰,并且不会产生干扰的能力。

2.怎么减小EMI?

(1)信号线尽量走同一层

(2)避免直角或锐角走线

(3)避免走线形成环路

(4)避免走线开路

五.信号串扰

1.信号串扰

信号串扰有两种,一种是寄生电容导致相邻信号串扰。一种是电磁作用导致出现的共模干扰EMI。

2.怎么减小信号串扰?

(1)减小寄生电容

(2)减小EMI

六.高速信号线

高速信号线是指信号时钟频率高于250MHz的信号线。

高速信号线走线原则

(1)避免平行走线(主要指不同组的信号线隔层平行),最好十字交叉

(2)夹地相邻,相邻信号线之间包夹底线。

(3)走线尽可能短

(4)禁止锐角、直角转弯

(5)避免环路

(6)尽量少过孔

(7)同组信号线等长走线(避免时序错乱)

(8)走线特性阻抗等于50欧姆

七.高速差分对

高速差分对一般只USB/MIPI/LVDS等通过差分电压承载信号的高速信号线。

告诉差分对走线原则

跟普通高速线基本一致,但对等长走线更加严格。

八.去耦/旁路/滤波/耦合电容

1.去耦电容

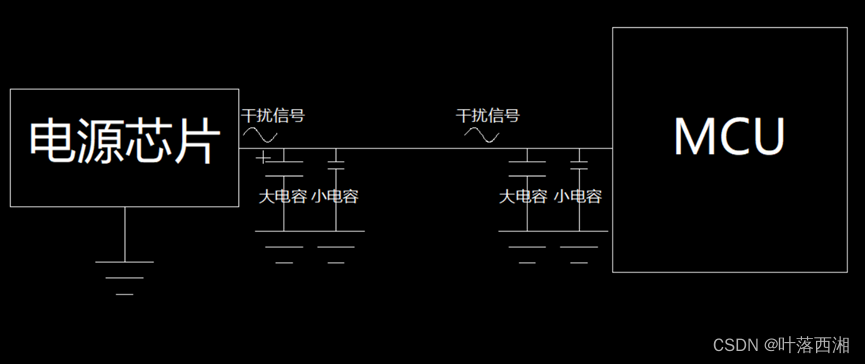

靠近输出端,防止器件内部产生的电压波动影响到后面的负载。一般加在电源输出端,容值较大,主要抵抗的是低频的电源波动,起稳压作用。

2.旁路电容

靠近输入端,一般是芯片输入引脚,主要功能是滤除输入信号的高频干扰,避免对信号处理产生影响,一般容值较小,起低通滤波的作用。

3.滤波电容

滤波电容是为了过滤特定频率的信号设计的电容,即可以位于输入端也可以位于输出端,主要看使用目的,容值要经过专门计算或试验得出。

4.耦合电容

耦合电容的作用是隔直通交,串联在电路中,防止直流输出。一般用于高频交流信号输出,去除直流分量的影响。

5.直流偏移对音频设备的危害

轻微的直流偏移会使耳机/喇叭的音圈不在磁隙的最佳位置,对音效有影响。严重的直流偏置,使音圈剧烈发热,音圈胶融化,线圈烧毁,振膜在巨大的磁推力和音圈的热量作用下变形损坏。

6.去耦/旁路/滤波电容为什么要靠近作用端?

这里就涉及到去耦半径的概念,这里以去耦电容为例,其他类似,去耦电容的作用是补偿干扰源造成的电源抖动,所以这个作用要越快越好(不能还没来得及补偿,已经进了负载了,那这个去耦就去了个寂寞),而干扰信号传输到电容的位置是需要时间的,如果电容跟干扰源较远,那么中间的导线电感会使干扰信号无法及时到达电容位置,这会导致两个结果,(1)负载位置比电容近,干扰还没进电容,先进了负载,这种显然去耦没有起作用。(2)电容感受到了干扰,产生补偿,但是已经追不上原干扰了,干扰和补偿一前一后的进了负载,这就是干扰和补偿的相位不一致。这两个结果都导致了去耦失效,那么去耦有效的走线长度就叫去耦半径。一般来说电容要靠近作用对象越好,最大距离不能超过去耦半径,超过了去耦半径,去耦作用就会失效。

7.去耦半径计算

去耦半径=干扰信号波长/50,注意干扰信号波长计算公式为:波长=电磁波在PCB走线上的传播速度/干扰频率

一般也不用刻意计算去耦半径,尽量靠近即可。

8.不同规格电容的摆放顺序

这其实很简单,只需记住干扰来了让大电容的先上。

对于输出端的去耦电容,干扰从电源芯片往外输出,所以大电容要更靠近输出引脚,大的低配扰动去除后,再去除更高频的干扰。

对于输入端的旁路电容,干扰是从外部输入到芯片里去的,所以小电容要更靠近芯片引脚。

当然,不管大电容还是小电容,都要尽量靠近,不能超出去耦半径。

九.阻抗匹配

1.什么是阻抗匹配?

阻抗匹配的形象比喻,可以把高频信号的传输想象成水流的传输,如果下一节水管的水管直径变窄,那么水流就会受阻,部分水流会反射回来。所以为了畅通无阻的传输水流,必须保证每一段的水管直径一致。

事实上,任何电源(信号源)都会有内阻,也会有最大输出功率,根据公式可以计算出当负载阻抗跟内阻一致的时候,负载上可以得到最大输出功率。根据这个结论,对于电源来说,最大输出功率越大,不可避免的,内阻也会越大。对于射频源来说,天线(射频负载)阻抗跟射频源内阻一致(或共轭),就可以使发射出去的电磁波能量最大。而根据水管的比喻,射频传输线(馈线)的特性阻抗也要跟内阻一致,否则会导致信号反射,由于高频信号波长短,容易在馈线上形成驻波,这样不仅天线得不到最大发射功率,而且还会导致馈线发热,甚至烧毁设备。发热的原因在于入射波和反射波形成驻波,所以阻抗匹配需要重点关注的就是驻波比系数,一般要求驻波比的S11系数为1,即没有反射,能量全部发射出去,阻抗完全匹配。

射频源、传输线(馈线)、天线(负载)的阻抗一致,就是阻抗匹配。根据行业经验,兼顾成本和性能,一般ISM频段和常用的电子设备内阻一般设计为50欧,广播电视行业为75欧姆。所以一般家用电视机的AV视频线阻抗一般为75欧,而电子产品wifi/蓝牙天线和馈线一般为50欧。

2.PCB走线的阻抗怎么算?

对于有严格阻抗要求的走线,如天线馈线,必须50欧,需要联系PCB板厂,板厂会给计算公式,一般是计算出铜箔厚度和宽度,嘉立创可以在线计算。

3.怎么做阻抗匹配?

天线的馈线上一般要留有匹配电容和电感,当阻抗失配的时候,调整匹配电容和电感使阻抗匹配。

阻抗测试一般使用网络分析仪进行测试和调试,关于网络分析仪用法不展开说明。下面只说一下阻抗圆图怎么看,阻抗圆图的中心是50欧阻抗,不同频点可能位于不同位置,阻抗匹配需要做的就是调整匹配电容和电感,使工作频点的阻抗尽量靠近圆心。