多通道数据采集设备在当前信息数字化的时代应用广泛,各种被测量的信息 如光线、温度、压力、湿度、位置等,都需要经过多通道信号采集系统的采样和 处理,才能被我们进一步分析利用[37]。在一些对采集速率要求较高的军事、航天、 航空、工业制造等领域,为满足信号分析的实时性,对信号采集系统的采样及处 理速率提出了更高的要求,高速信号采集系统的需求场景不断增加。

2.2.1.3 JESD204接口

为了解决并行接口下的高速率传输限制,由固态技术协会JEDEC推出的,传 输速率高达10G的串行数据接口:JESD204。结合了差分 LVDS电流型结构驱动 的优势,以CML结构作为其输出驱动单元,推出了 JESD204 系列标准。以串行 的数据传输方式,大幅度的降低了芯片的引脚数量,简化了PCB布局,获得更小 的芯片尺寸,同时还提高了数据传输速率。尤其适用于高转换速度、高分辨率的 场景下。表2-2是对三种高速数据接口的典型特征进行对比。

JESD204协议一共推出了4个版本:JESD204、JESD204A、JESD204B 、 JESD204C。

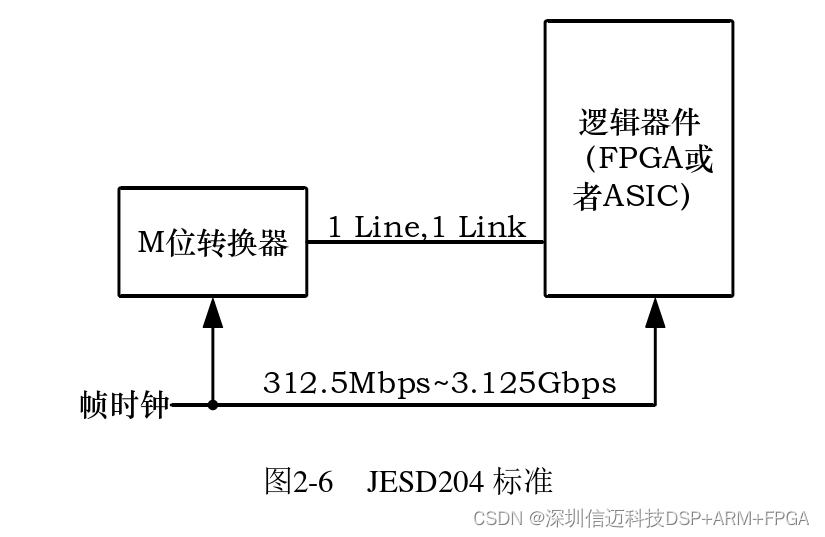

2006年4月JEDEC 固态技术协会发布了第一版JESD204协议[24]:JESD204。 该协议描述了转换器与数据处理器之间的高速串行数据链路传输接口。JESD204 只支持一个转换器与逻辑器件之间进行单通道(line)、单链路(link)的数据传输,M 位数据转换芯片均在一个串行CML通道上传输,最高速率可达 3.125Gbps[25]。如 图2-6所示。

JESD204协议规定了数据链路层使用 8b/10b 的编码方式,转换器与逻辑处理 器件使用同一个时钟:帧时钟(Frame Clock)。把需要的时钟嵌入数据流里,避免了 高速数据传输时,数据要与时钟对齐的难点。

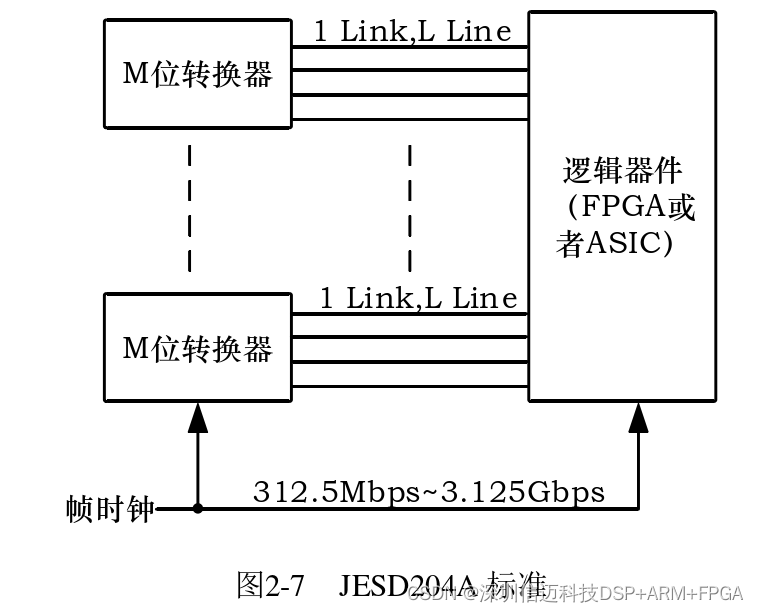

2008年的4月份,JEDEC 推出了JESD204A版本。主要增加的功能有: 1) 单个逻辑处理器可以与多个转换器器件同时传输数据。 2) 单个转换器器件单个链路下多个通道同时传输功能。 3) 单个链路下多个通道数据对齐功能。

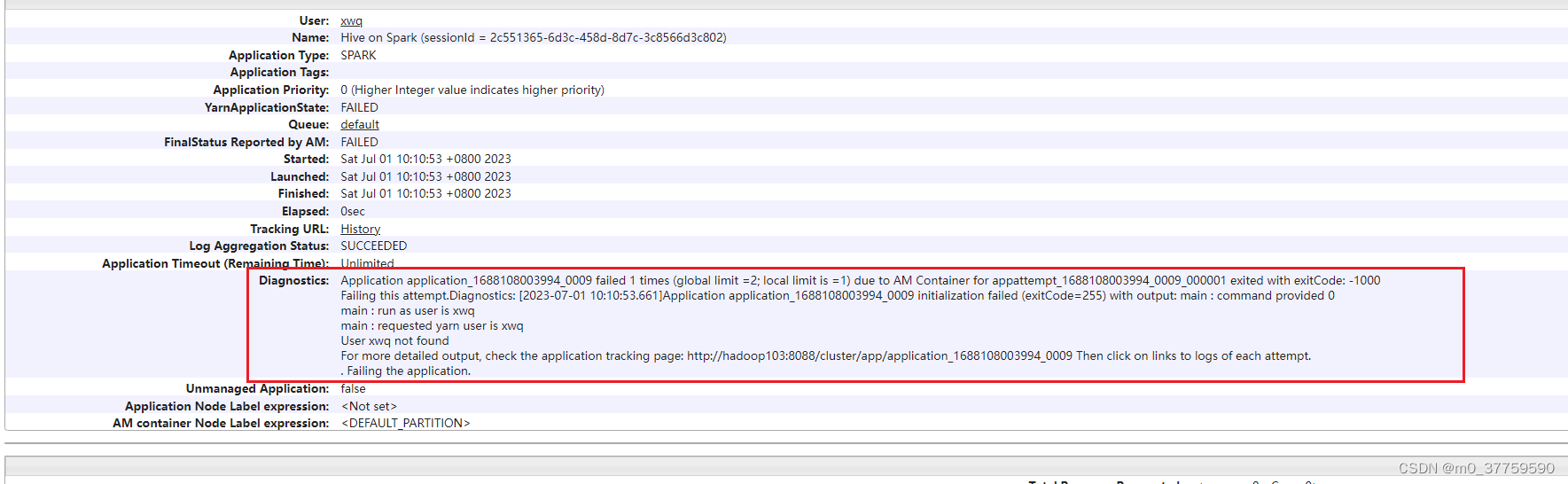

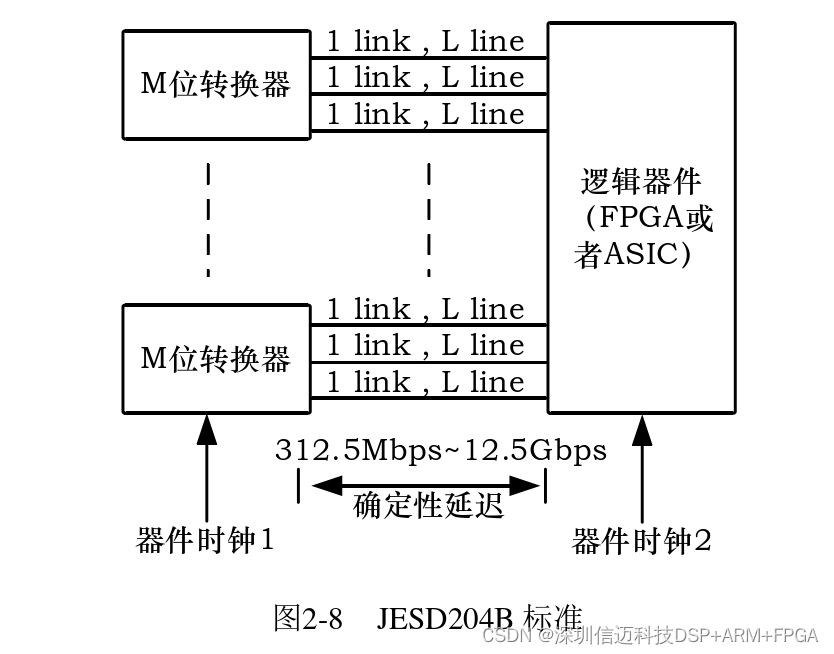

2011年的8月份,JEDEC 推出了JESD204B版本。该版本的主要改变为: 1) 取消帧时钟,数据转换器与逻辑处理器使用各自的的器件时钟(Device

clock),提升器件使用灵活度。 2) 支持确定性延迟,支持多器件多通道同步。 3) 最大传输速度提高到了 12.5Gbps。

JESD204B存在3个子类[26],分别是子类0,子类1,子类2。三个子类根据 同步的方式进行划分。子类0兼容JESD204A,子类1使用SYSREF同步,子类2 使用SYNC进行同步。只有子类1和子类2支持确定性延迟,即从数据发送到数 据接收之间的链路延迟固定。

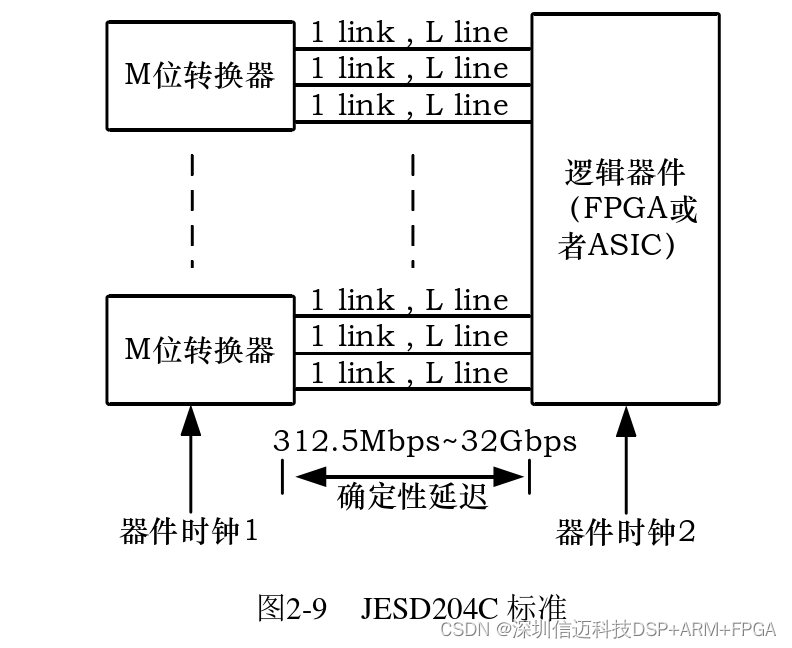

2017年10月,JEDEC发布了JESD204标准的第三个修订版本JESD204C。 该版本的主要改变为:

1) 通道最大传输速率可达 32Gbps。

2) 6.375Gbps 到 32Gbps传输速率下,按照链路功耗划分成三个子类,分别

为:C-S、C-M、C-R。

3) 引入了两种编码方式:64B/66B和64B/80B。

表2-3是对四种版本的JESD204接口典型特征进行对比。

与CMOS和LVDS接口相比,JESD204与JESD204A接口的优势没有特别明 显,没有被普遍应用。而JESD204B协议因其显著的优势,受众多高速转换器公 司的青睐,推出了大量基于JESD204B协议接口的高速转换器产品,典型的公司 有亚德诺(ADI)、德州仪器(TI)。JESD204C协议推出时间较晚,用户应用需求不是 很强烈,应用广泛度暂时不如JESD204B接口。 2.2.2 多芯片同步

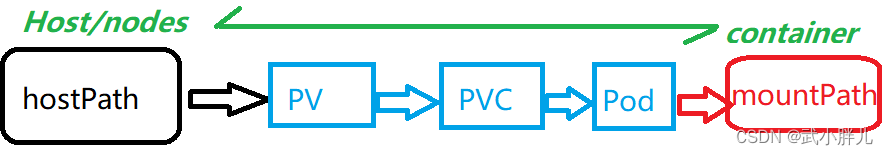

在多通道数据采集技术中,不同的通道在相同的时刻进行数据采集,相位是 相同的。而实际上,由于通道间的物理路径延迟不同,导致多路原始信号在传输 过程中存在着不同的延迟,信号数据没有对齐。同理,多个采样时钟也存在着链路延迟,也没有达到同步采样的效果。通过对通道间延迟标校,再进行通道间延 迟补偿和修正,使得不同通道的原始信号起点一致,采样时刻一致,进而实现数 据同步采集的效果。

文献[27]提出一种多物理量集体效应思想,阐述了多个物理因素造成的通道间 延迟时间差,并用时基补偿和修正,完成数据采集的同步。多个物理因素可以分 成模拟因素和数字因素,因此多通道数据采集同步技术分可为模拟信号同步和数 字信号同步。其中模拟信号同步保证多通道模拟信号相位一致,数字信号同步保 证多通道数字信号采样时刻一致。 2.2.2.1 模拟信号同步

文献[28]给出了多片模拟信号同步的方法:当多个模拟信号采集通道使用同一 个本振时,可以忽略模拟信号接收链路中放大、滤波、衰减带来的相位偏移影响, 实现模拟信号同步。

目前的ADC普遍支持单片多通道模拟信号同步采集,不一定支持模拟信号多 片同步(Multi-Chip Sync,MCS)采集。例如ADI公司的AD9361芯片,采用零中频 架构,芯片支持片内两通道同步,但不支持多片多路模拟信号同步。若此类芯片 需要实现多片多路模拟信号同步,有两种实现方法:

1) 一是多片ADC共用一个本振方法。

2) 二是测量多片内部LO的相位差,然后通过FPGA算法进行校准。 其中方法一对本振信号质量要求极高。针对方法二文献[29]给出了通过算法补 偿实现多片AD9361相位同步的方法。 2.2.2.2 数字信号同步

在常用的多通道信号同步采集方法中,使用同一个时钟,根据链路延时稍加 调整后去采集多片ADC芯片的数据。在采集时,选取其中一个ADC的同步时钟 作为采样时钟,该时钟与各片ADC数据同源,但相位关系未知[30]。通过FPGA内 部的输入输出延迟单元功能,将各片ADC输入的数据信号进行延时调整,调整数 据信号与采样时钟之间的相位差,保证采样时钟可以正确的采到对应的数据,实 现了多片数字同步采样的功能,结构简单,易于工程实现。

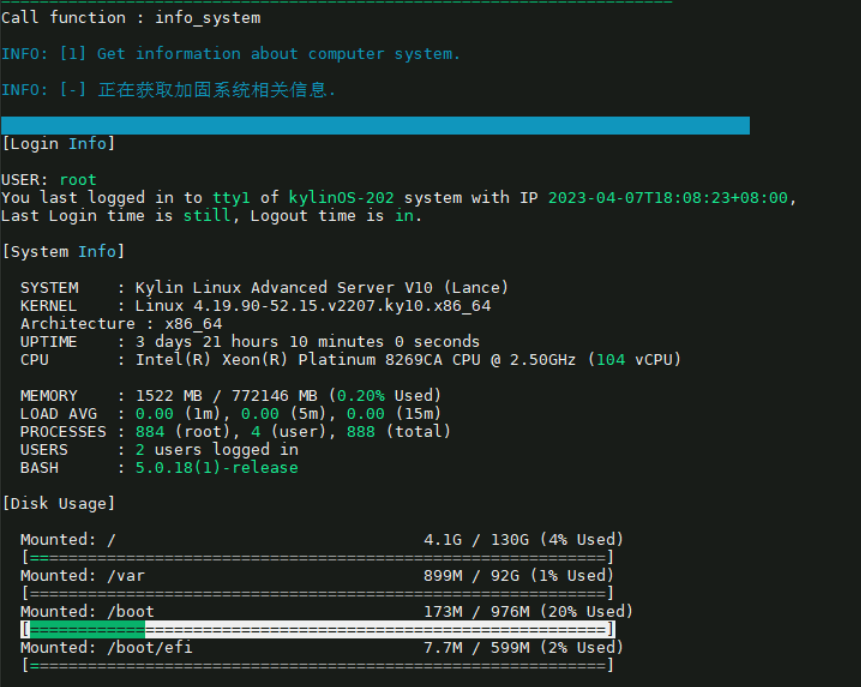

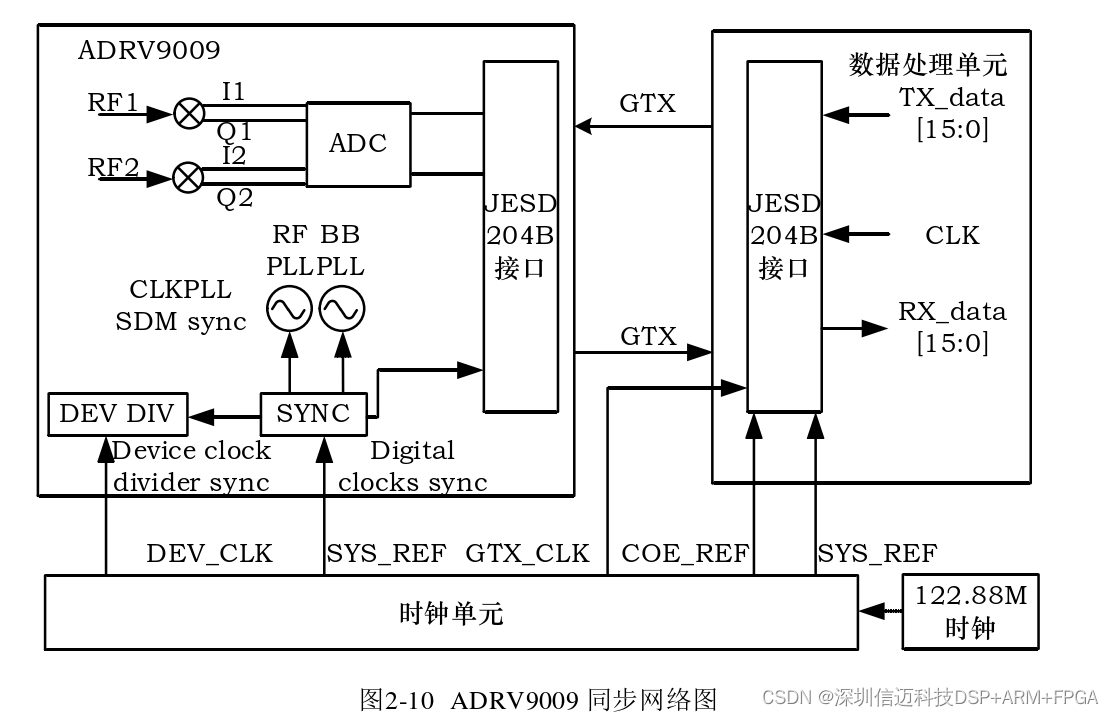

以ADI公司的ADRV9009芯片[31]为例,该芯片支持 JESD204B接口,通过对 板内两片FPGA同步协调管理配置,达到在两片FPGA上配置多片ADRV9009芯 片的功能,实现多片ADRV9009同步采集的要求。本设备多片ADRV9009芯片的 同步网络如图2-10所示。

JESD204B接口在同源时钟下使用自带的同步协议便可以达到多片同步的功 能。由ADRV9009同步网络图可以看到该模拟信号集成芯片内部不仅有JESD204B 接口还有内部基带锁相环(BBPLL)、模拟信号锁相环(RFPLL)、输入分频模块 (DEVDIV)、同步管理模块(SYNC)。参考时钟进入该芯片内部后,还经过了内 部的同步管理模块、分频模块和基带锁相环再分给JESD204B使用。所以想要达 到多片同步的功能,还需要对ADRV9009芯片内部各个模块进行同步触发。 2.2.3 多线程同步

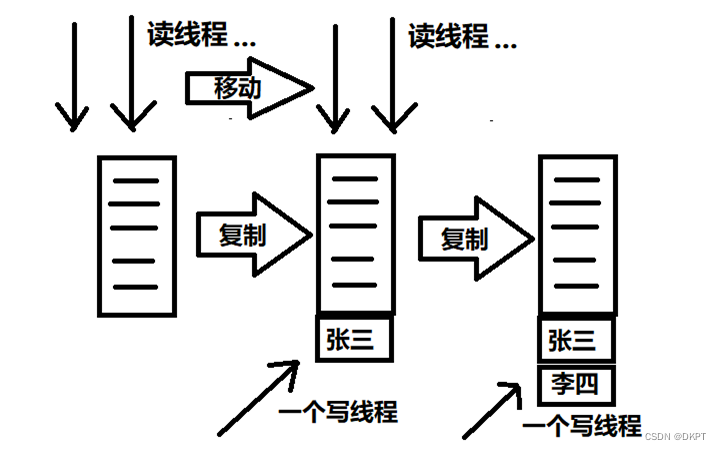

因为多片数据转换器需要同步采集,所以不能依次配置各个数据采集器。为 了满足同时配置的需求,运用操作系统的多任务特性,即在一个应用程序中创建 多个线程来分别完成各个数据采集器的参数配置任务。

以ADI的ADRV9009芯片为例,实现多片ADRV9009同步的核心是需要三个 相位相同的SYSREF脉冲信号。每个线程在配置ADRV9009时,都会阻塞在等待 3个SYSREF脉冲信号的状态,当主线程检测到每片ADRV9009都处于等待脉冲 的状态时,控制时钟管理芯片产生3个SYSREF脉冲,这样多片ADRV9009就同 时收到了3个同相位的SYSREF脉冲。